#### **Project: IEEE P802.15 Working Group for Wireless Personal Area Networks (WPANs)**

Submission Title: The Next Frontier for Circuit Designers: CMOS THz Systems Date Submitted: 13 November 2012 Source: Ehsan Afshari Company: Cornell University Address 424 Phillips Hall, Cornell university, Ithaca, NY 14850 Voice:[607-255-0603], FAX: [6072544208], E-Mail: ehsan@ece.cornell.edu Re: n/a

**Abstract:** There has been a growing interest in mm-wave and Terahertz frequencies for communication, imaging, and sensing applications. In this talk, we will look into recent advances in CMOS implementation of various building blocks. First, we show how to implement mW-level signals up to 500GHz. Then we show different amplifiers as well as two transmitters at 260GHz and 350GHz.

#### **Purpose:** Information to IEEE 802.15 IG THz

**Notice:** This document has been prepared to assist the IEEE P802.15. It is offered as a basis for discussion and is not binding on the contributing individual(s) or organization(s). The material in this document is subject to change in form and content after further study. The contributor(s) reserve(s) the right to add, amend or withdraw material contained herein.

**Release:** The contributor acknowledges and accepts that this contribution becomes the property of IEEE and may be made publicly available by P802.15.

# The Next Frontier for Circuit Designers: CMOS THz Systems

#### $\overset{}{\longrightarrow}$

Ehsan Afshari Cornell University (http://unic.ece.cornell.edu)

November 2012

#### Acknowledgement

• The people who actually make it happen!

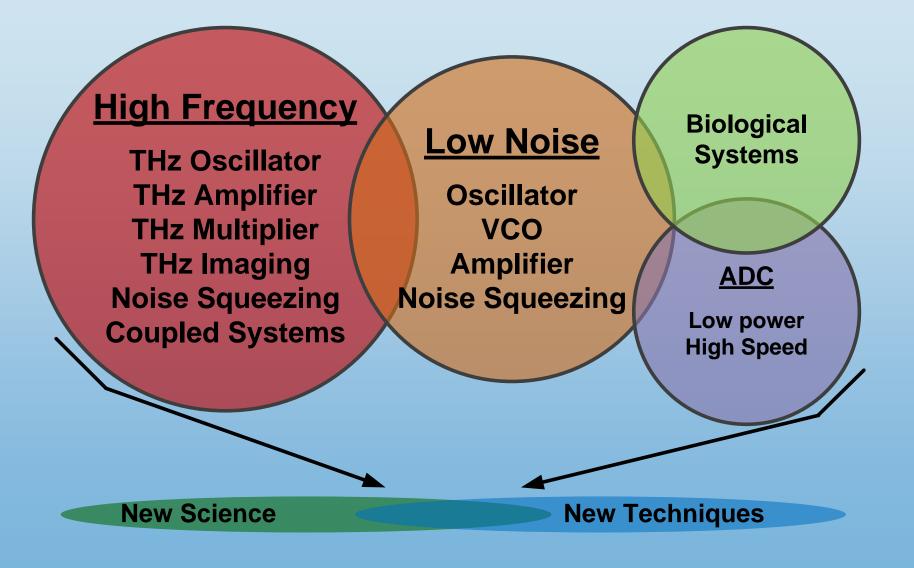

#### **Our Research**

### **Other Projects**

- Low phase noise oscillators:

- Dual mode,

- Quadrature.

- Wideband low phase noise VCO:

- 2.4GHz 5.6GHz that satisfies ALL cellular specifications

- Low power, high speed ADC

- 8GS/sec, 4b with 32mW

- 1.2GS/sec, 4b with 2mW

- Narrow pulse generation on CMOS

- 1.6ps pulse on standard 65nm CMOS

- A 260GHz Amplifier

- 9.2dB gain

- -4dBm Psat

| Process      | 65nm Low Power CMOS                    |        |        |           |        |        |

|--------------|----------------------------------------|--------|--------|-----------|--------|--------|

| Vdd (V)      | VCO Core: 0.6 V; Digital Control: 1.2V |        |        |           |        |        |

| Tuning Range | 2.48GHz~5.62GHz continuous tuning      |        |        |           |        |        |

| Chip Area    | 0.294 mm <sup>2</sup>                  |        |        |           |        |        |

| Phase Noise  | Odd Mode Even Mode                     |        |        |           |        |        |

| Phase Noise  |                                        |        |        | Even Mode |        |        |

| (dBc/Hz)     | Low                                    | Middle | High   | Low       | Middle | High   |

| Freq (GHz)   | 2.517                                  | 3.696  | 3.880  | 3.312     | 4.463  | 5.515  |

| ldc (mA)     | 23.61                                  | 17.43  | 16.49  | 25.27     | 20.97  | 16.43  |

| PN@100kHz    | -101.1                                 | -96.44 | -94.42 | -105.3    | -96.03 | -89.3  |

| PN@300kHz    | -114.4                                 | -112.7 | -112.3 | -117.5    | -110.3 | -105.1 |

| PN@1MHz      | -128.6                                 | -128.3 | -128.3 | -129.5    | -124.8 | -121.3 |

| PN@3MHz      | -139.8                                 | -137.1 | -137.2 | -139.5    | -134.6 | -130.7 |

| PN@10MHz     | -151.9                                 | -151.4 | -151.9 | -150.2    | -147.6 | -145.8 |

| PN@20MHz     | -156.8                                 | -156.6 | -156.7 | -155.5    | -153.1 | -151.7 |

| FoM@10MHz    | 189.4                                  | 192.5  | 193.7  | 188.8     | 189.6  | 190.7  |

# Outline

- Motivation

- Terahertz Frequency Multipliers

- High Power Terahertz Oscillator Design

- A High Power THz VCO

- THz Radiator Arrays

- Conclusion

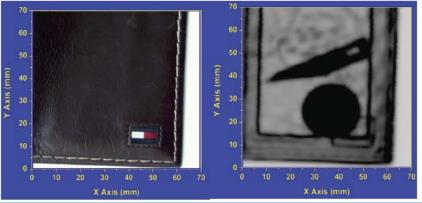

- Imaging (e.g., detection of concealed weapon, cancer diagnosis, and semiconductor wafer inspection )

- Compact range radars

- High data rate communication (e.g.,100 Gbps)

High power is needed for these applications

- Skin cancer detection:

- Large tumors can extend 15mm beyond the visible border

- Significant number occur on face

- Existing techniques can have high false negative rates and is time and personnel intensive

- At 700GHz, we can have  $40\mu m$  depth resolution and 1mm penetration

- Tooth decay:

- Small cavities are hard to detect

- Earlier detection equates to better outcomes

- X-ray has limited resolution

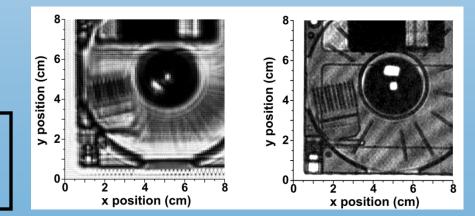

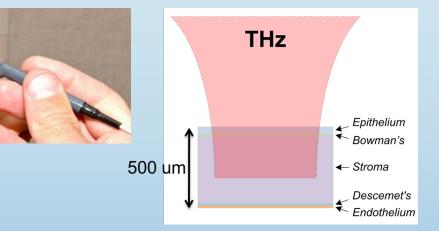

- Corneal hydration sensing:

- Diseases and procedures:

- Corneal Graft surgery

- Fuch's Dystrophy

- Keratoconus

- Glaucoma

- LASIK

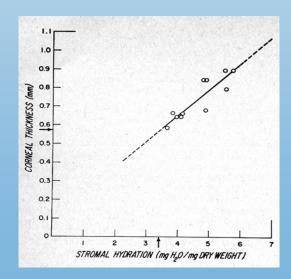

- Current methods based on ultrasonic or optical thickness measurements

- Thickness measurement very accurate (~ 9 um)

- Mapping from thickness to hydration very inaccurate (+/- 5% by volume)

- Physiologic variation confounds measurement

- Listed diseases and procedures need hydration sensitivity in the range of 0.8% - 3% depending on application

- THz imaging results in better than 0.2% sensitivity

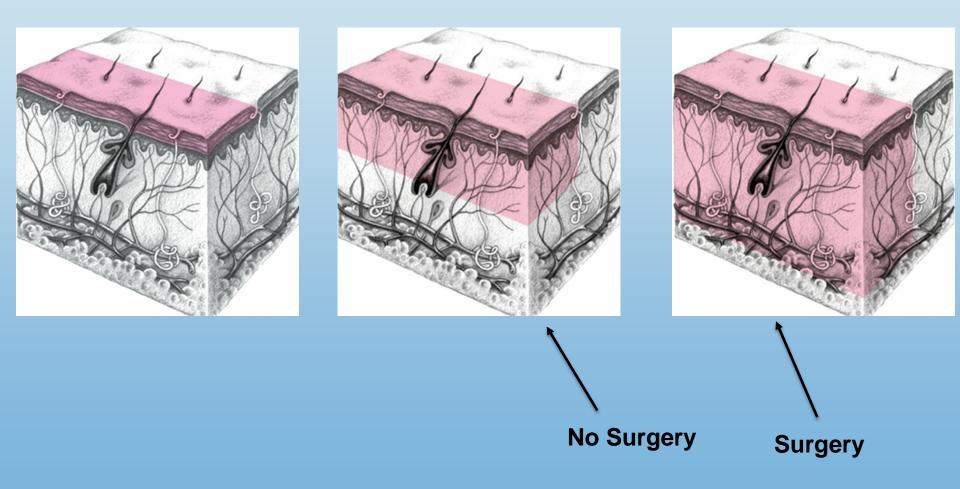

#### Partial (superficial)

**Deep Partial**

#### <u>Full</u>

- Current clinical methods rely on visual and tactile assessment of burned skin

- Current imaging methods lack dynamic range for margin detection

- Laser Doppler Imaging

- Vital Dyes

- PS-OCT

- Thermal Imaging

- THz imaging results in mmresolution detection.

### Challenge

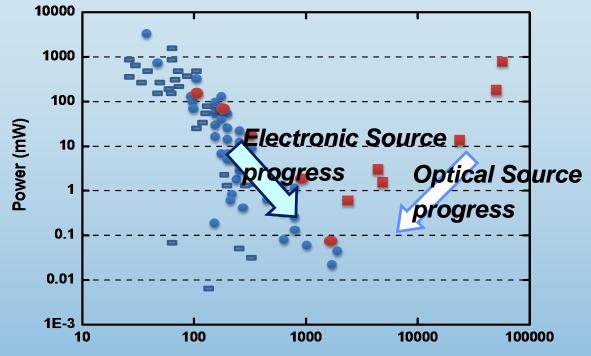

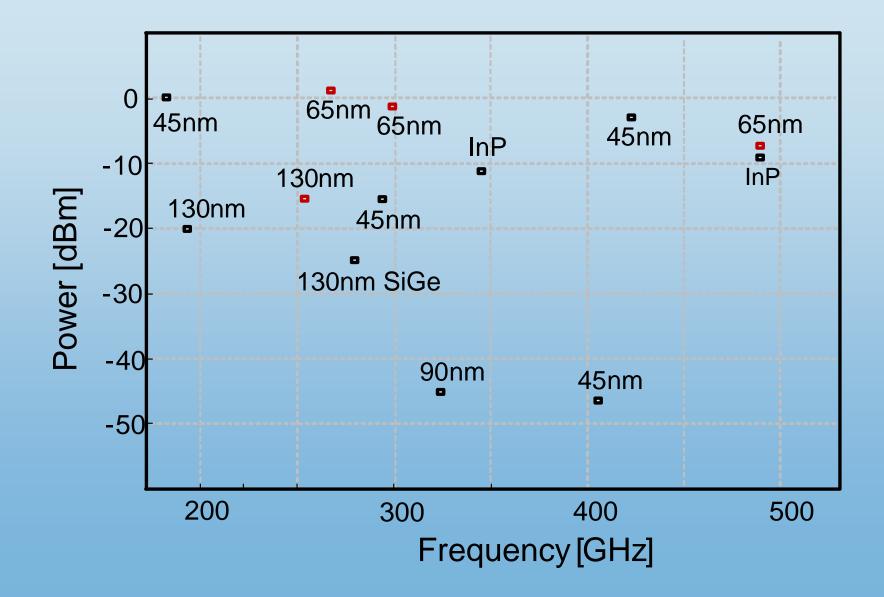

Solid-State THz Sources (CW)

#### **Fundamental Challenges:**

Frequency (GHz)

• Transistors offer no power gain above  $f_{max}$

- Limited power efficiency of devices

- Limited break down voltage

- Quality factor of passives is low

High power signal generation is the main challenge in realizing CMOS THz systems.

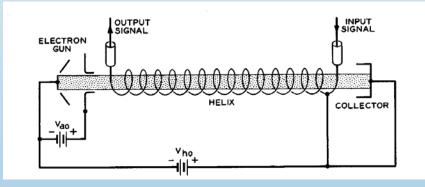

# **Terahertz Electronic Sources**

- Travelling electron beams

- Example: BWO

- Up to 1 mW around 1 THz

- Very bulky and expensive

- Josephson arrays

- Quantum tunneling in superconductors

- Cryogenic temperatures

- < 1µW power levels

- <u>Solid-state devices</u>

- Limited by electron scattering

- InP devices: 100  $\mu$ W to 1 mW around 400 GHz

# **Solid-State Devices for Terahertz**

- Diodes (Gunn, IMPATT, Tunneling, etc.)

- Compound semiconductor transistors (InP HBT, GaN HEMT, etc.)

- ✓ Large breakdown voltages (i.e. GaN > 20 V)

- ✓ High cut-off frequency ( $f_{max}$  ~ 1 THz)

- X Expensive material

- X Not suitable for large scale integration

- CMOS transistors

- Cheap and versatile technology

- X Low supply voltage (~ 1.2 V)

- X Low cut-off frequency ( $f_{max}$  < 0.25 THz)

A CMOS Terahertz solution is highly

desirable but challenging

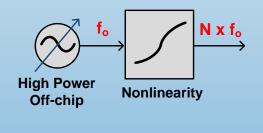

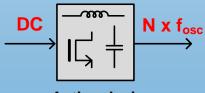

# **Signal Generation Above Cut-off**

- A nonlinear process generates harmonics of the fundamental frequency above  $f_{max}$ .

- Device nonlinearity can be exploited

- Diodes: IMPATT, Gun, Tunneling, Schottky

- Transistors: HBT, HEMT, CMOS

- Two approaches:

- Multiplier : a high power source is normally provided off-chip.

- Harmonic oscillator : The oscillator is implemented on chip

- On-chip implementation is the ultimate solution

Active device

# Outline

- Motivation

- Terahertz Frequency Multipliers

- High Power Terahertz Oscillator Design

- A High Power THz VCO

- THz Radiator Arrays

- Conclusion

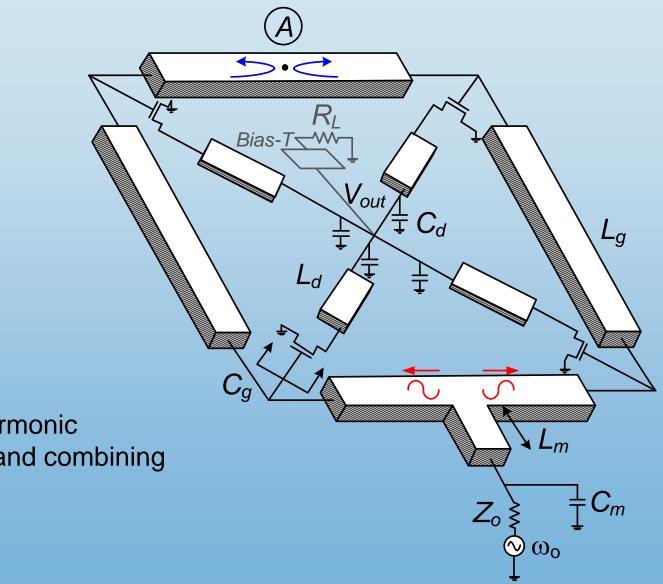

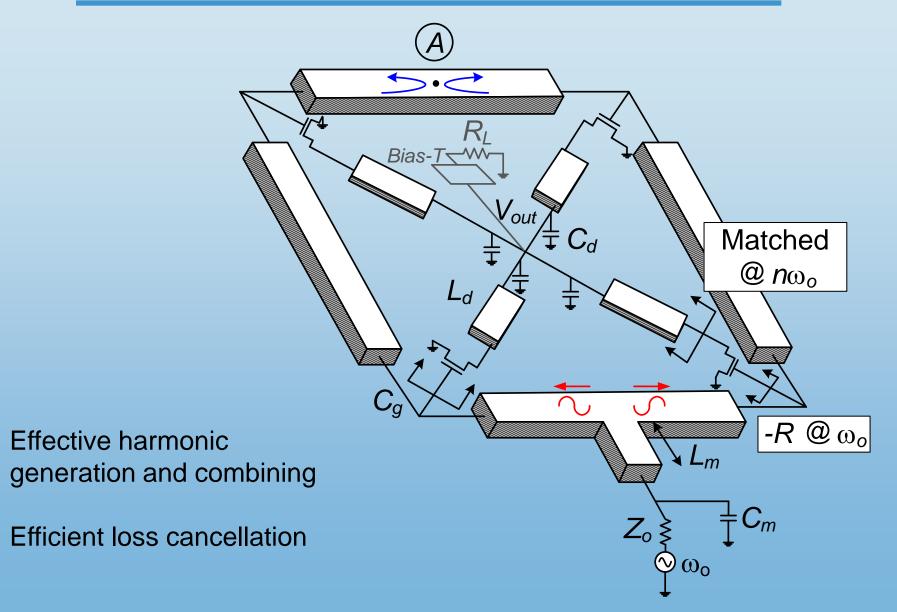

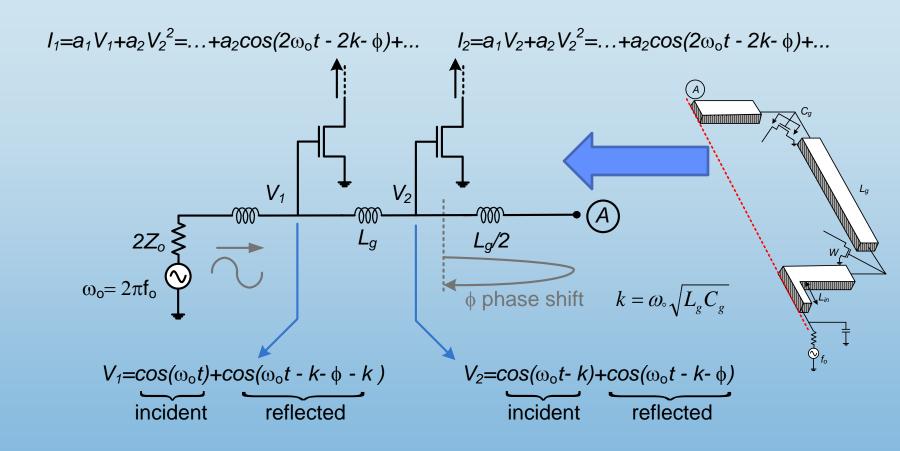

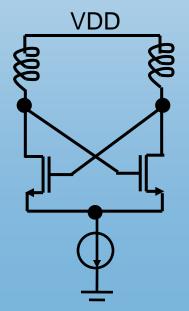

#### **Basic Idea**

• Effective harmonic generation and combining

### **Basic Idea**

# Theory

- The second harmonics add in phase at the output

- The basic principle is independent of frequency

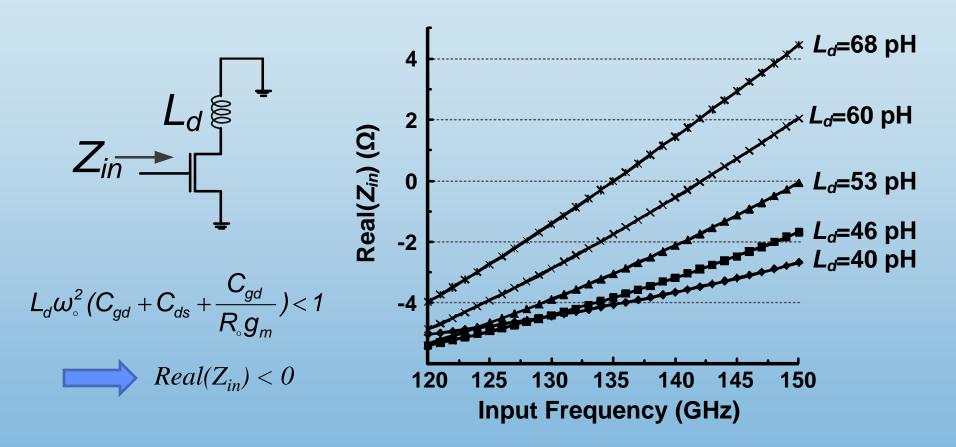

### **Negative Input Impedance**

There is a trade-off between better output matching and higher input voltage swing.

### Implementation

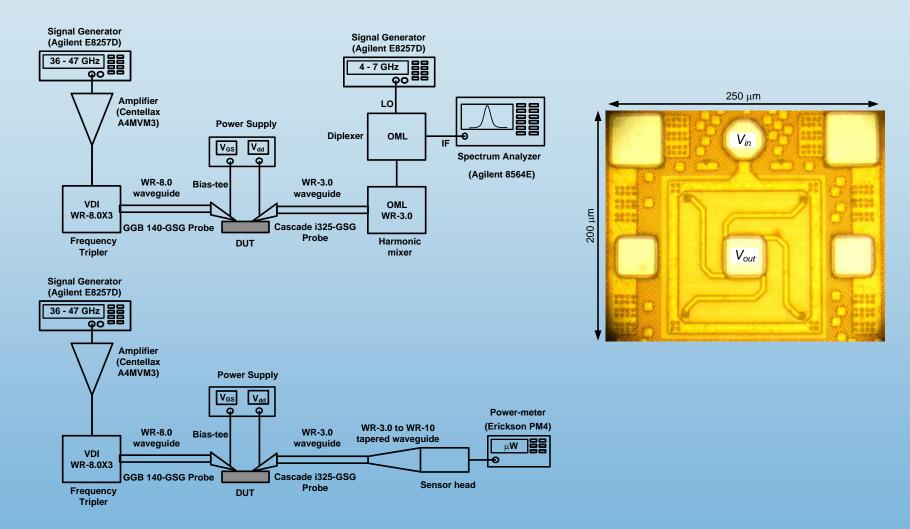

• The power and frequency test setups

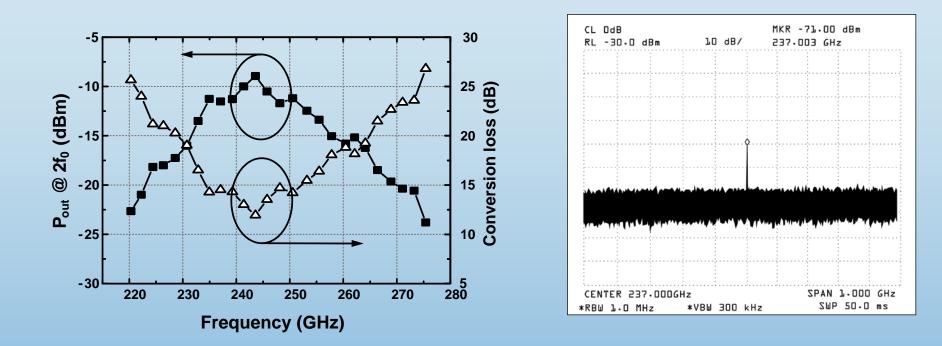

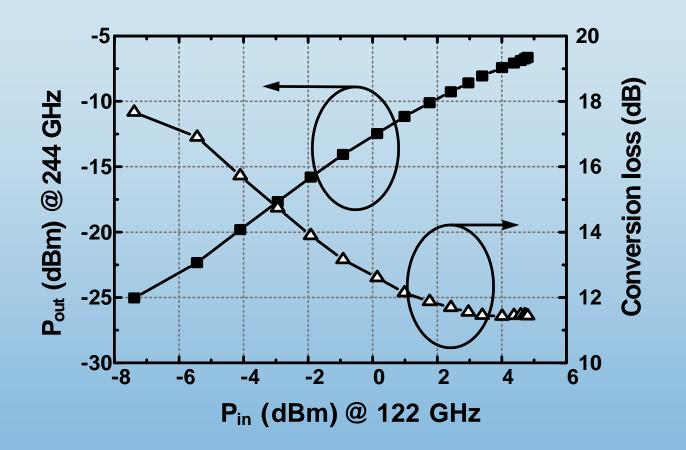

### Results

• In this case the input power is kept at 3dBm

#### Results

- The output power is not saturated

- A maximum of -6.6dBm is achieved at 244GHz

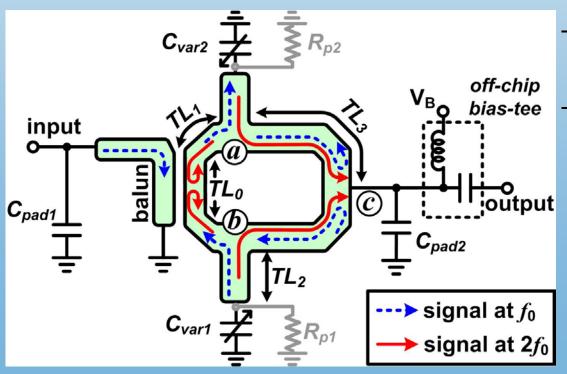

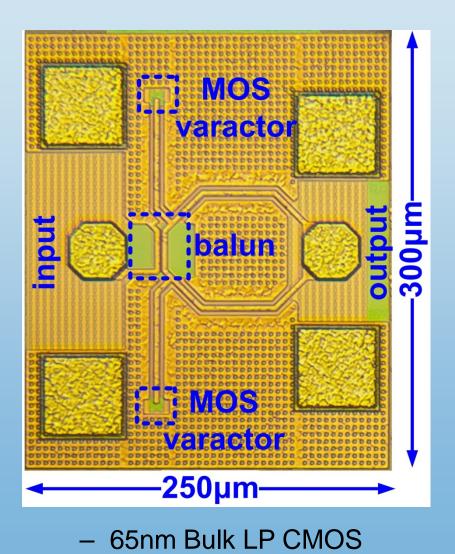

# A 480 GHz Doubler

- Main structure: a compact partially-coupled ring

- Simultaneous matching at fundamental (input) and 2<sup>nd</sup> harmonic (output)

- Pads are part of the input/output matching

- R<sub>p1</sub> and R<sub>p2</sub>: leakage paths for accumulative charge to avoid oxide breakdown

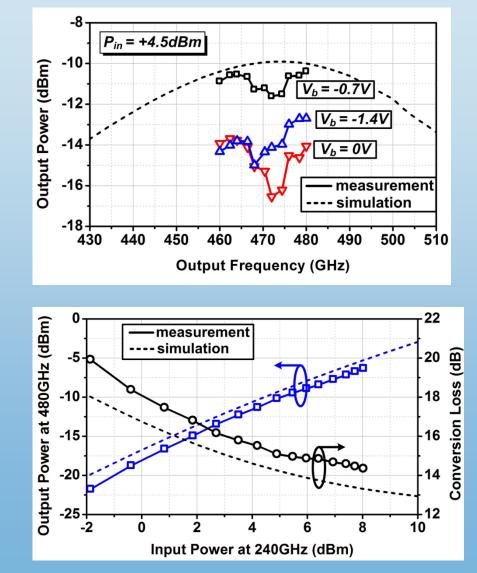

#### **Experimental Results**

# Outline

- Motivation

- Terahertz Frequency Multipliers

- High Power Terahertz Oscillator Design

- A High Power THz VCO

- THz Radiator Arrays

- Conclusion

## **Fundamental Limit?**

- Most of the fundamental oscillators have the oscillation frequency in the order of the half of the f<sub>max</sub> of the transistors. Why not higher?

- What is the maximum oscillation frequency of a circuit topology, considering the quality factor of the passive components?

- For a fixed frequency, what is the topology that results in maximum output power?

## **Fundamental Limit**

- Example: IBM 130 nm CMOS process:

- $f_{max}$ : simulated: 174 GHz

- $f_{max}$ : measured: ~135 GHz

- Regular Cross-Coupled oscillator:

- Maximum achievable frequency (simulation): 120 GHz

- This is with IDEAL inductors!

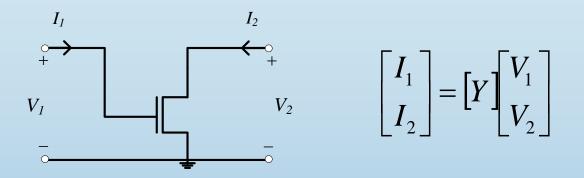

## **Activity Condition**

• Normalized real power flowing out of the device:

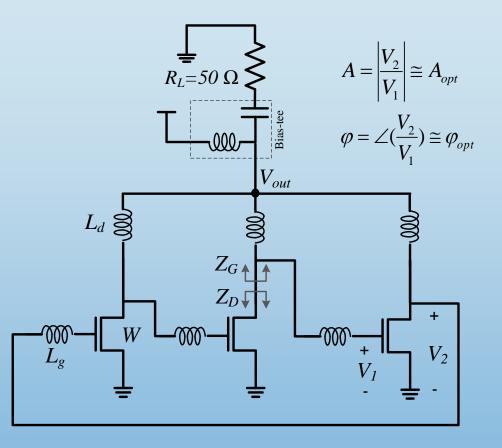

$$\Rightarrow G_{m} = \frac{P_{R}}{|V_{1}||V_{2}|} = -(A^{-1}G_{11} + AG_{22}) - |Y_{12} + Y_{21}^{*}| \cos(\angle(Y_{12} + Y_{21}^{*}) + \varphi))$$

$$G_{11} = real \ (Y_{11})$$

$$G_{22} = real \ (Y_{22}) \qquad A = \left|\frac{V_{2}}{V_{1}}\right| \& \varphi = \angle(\frac{V_{2}}{V_{1}})$$

•  $G_m$  is the maximum conductance that can be placed across the transistor and maintain the oscillation.

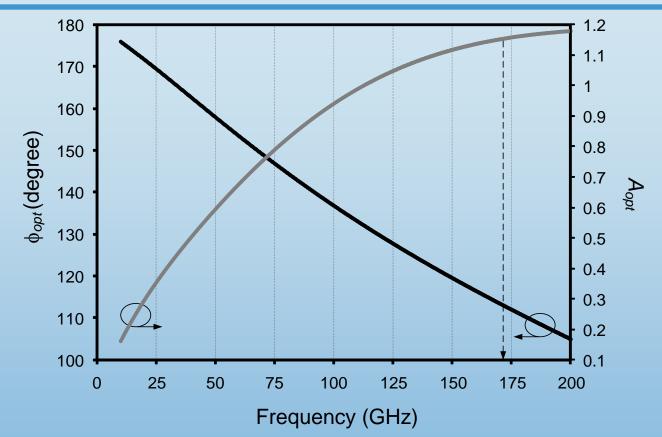

### **Maximum Activity**

Optimum gain and phase conditions for maximum generated power (maximum oscillation frequency)

$$\varphi = \varphi_{opt} = (2k+1)\pi - \angle (Y_{12} + Y_{21}^*)$$

$A = A_{opt} = \sqrt{\frac{G_{11}}{G_{22}}}$

# **Higher Frequency: Harmonics**

- In order to achieve higher frequencies, we need to generate strong harmonics

- This means we should maximize the swing at the fundamental frequency

- It might be better to back off from the maximum possible oscillation frequency to boost the harmonic generation

- We need to maximize " $G_m$ "

## **Optimum Conditions**

- Optimum phase and voltage conditions in a 65nm process

- Target frequency is 450 GHz

# **Triple Push Oscillator**

- The gate inductor helps with both amplitude and phase conditions:

- It resonates with C<sub>gs</sub> to boost the gate-source voltage, resulting in lower A across the device

- It also delays the voltage to increase the phase shift from 120.

### Implementation

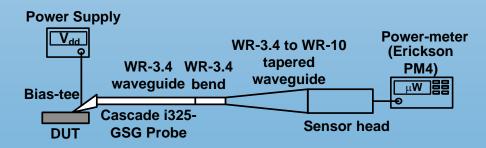

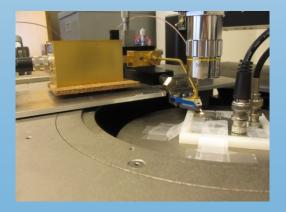

**Power Supply**

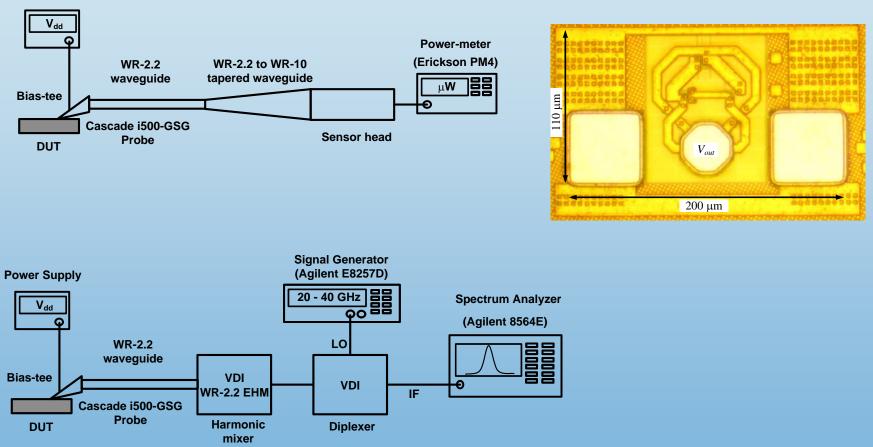

• The power and frequency test setups

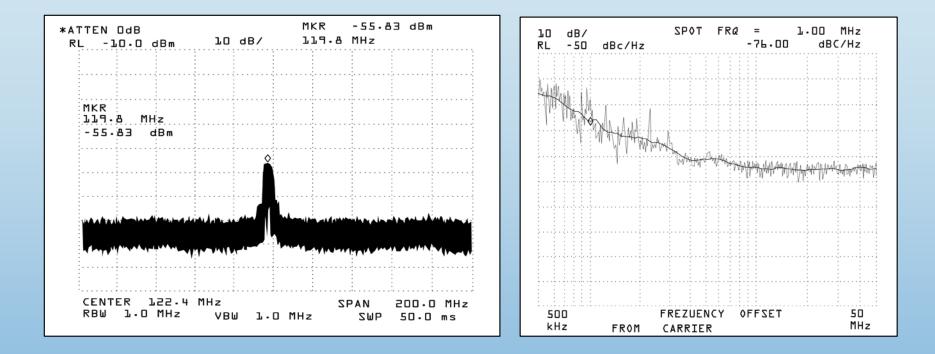

### **Results: Spectrum**

- The second harmonic is 15.5dB lower than the third harmonic

- Output frequency is 482GHz

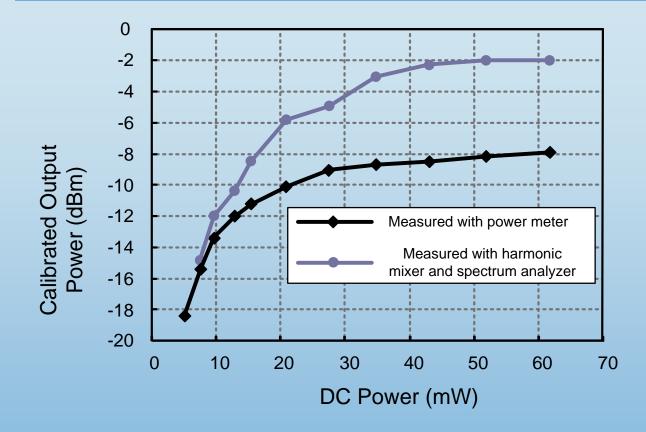

#### **Results: Power**

• Measured output power using both setups

### Outline

- Motivation

- Terahertz Frequency Multipliers

- High Power Terahertz Oscillator Design

- A High Power THz VCO

- THz Radiator Arrays

- Conclusion

#### **Challenge: Terahertz VCO**

- At mm-wave and terahertz frequencies it is challenging to get high tunability with varactors due to dominance of device parasitics

- Varactors are very lossy at mm-wave and are not desirable in mmwave and terahertz signal generation

| Ref.      | Technology    | Fundamental<br>(GHz) | Output frequency<br>(GHz) | Power<br>(dBm) | Tunability |

|-----------|---------------|----------------------|---------------------------|----------------|------------|

| JSSC '06  | 130nm CMOS    | 102GHz               | 102 GHz                   | -25 dBm        | 0.2%       |

| ISSCC 09  | 32nm CMOS SOI | 102GHz               | 102GHz                    | N/A            | 4.2%       |

| ISSCC `08 | 45nm CMOS     | 205GHz               | 410GHz                    | -47 dBm        | -          |

| ISSCC '11 | 45nm CMOS     | 150GHz               | 300GHz                    | -19 dBm        | -          |

| JSSC '11  | 65nm CMOS     | 160GHz               | 480GHz                    | -8 dBm         | -          |

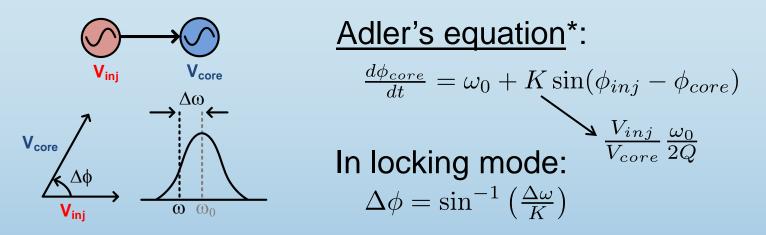

#### **Coupling: Adler's Model**

- Adler's model assumes sinusoidal weak coupling.

- A good coupling model around resonance.

- Two oscillators with close center frequencies will frequency lock.

- Depending on the original frequency difference, a phase lag (lead) is developed between the source and core.

## **Tuning the Locking Frequency**

- <u>Observation</u>: If the locking phase shift is modified, the locking frequency will be different.

- A injection locking scheme enforces the frequency and phase shift.

- We propose a structure with additional degrees of freedom to control the phase shift.

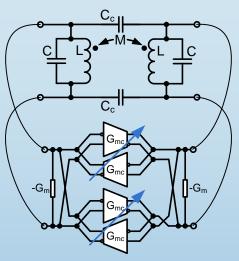

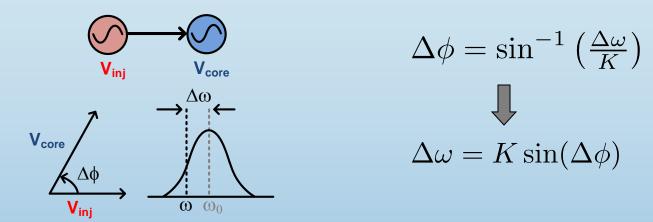

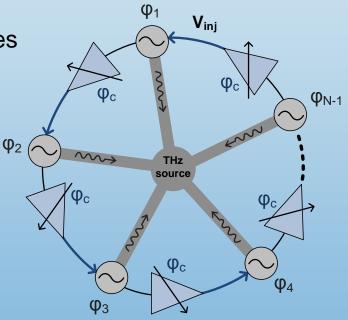

## **Delay Coupled Oscillators**

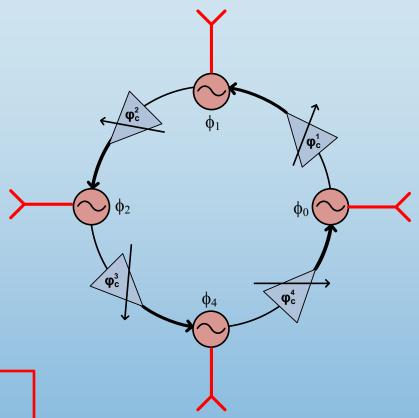

- N core oscillators coupled in a unidirectional ring

- N oscillators and N coupling blocks are similar

- The tuning mechanism is based on tuning the coupling block

- We assume weak coupling close to resonance

Governing dynamic equations

$$\dot{\phi}_i = \omega_0 + K \sin(\phi_{i-1} + \phi_c - \phi_i)$$

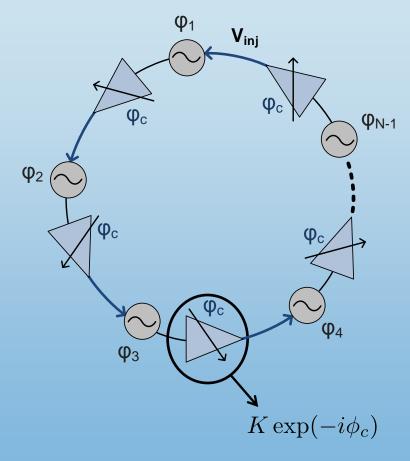

### **Approach to Frequency Tuning**

In a given coupling mode Ψ is fixed

Changing Φ<sub>c</sub> results in change in the locking frequency

$$\dot{\phi}_i = \omega_0 + K \sin(\phi_{i-1} + \phi_c - \phi_i) \qquad \omega = \omega_0 + K \sin(\phi_c - \psi_k^o)$$

#### **A Terahertz Tunable Source**

- Features of the proposed source

- ✓ Efficient harmonic generation

- ✓ Power combining from multiple sources

- Tuning separated from power generation

- ✓ A scalable scheme

- Design steps

- Choose the best harmonic frequency

- Select the number of cores (N)

- Design the coupling and combing blocks

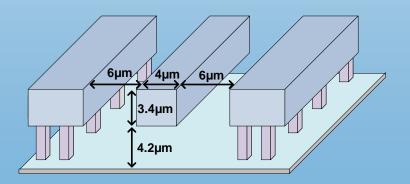

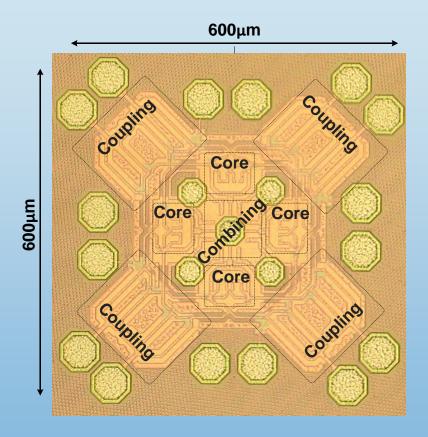

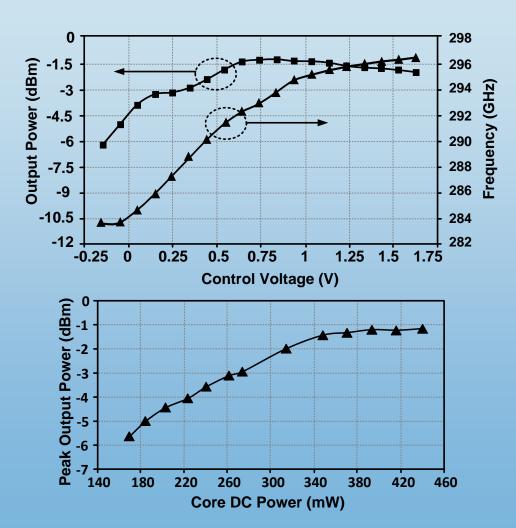

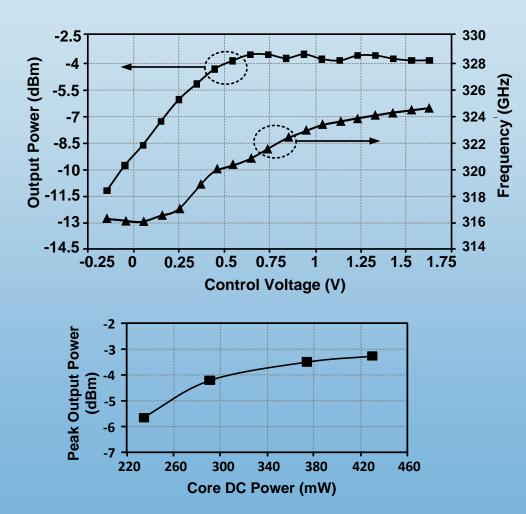

## Silicon Prototype

- Standard 65nm LP bulk CMOS

- Grounded CPW for lines

- Ground shielding between blocks

- Two versions are measured

- A 290 GHz source

- A 320 GHz source

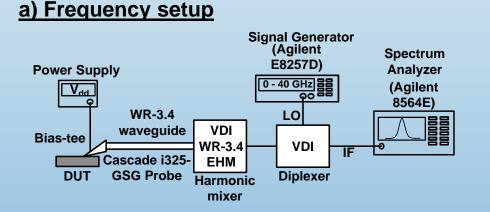

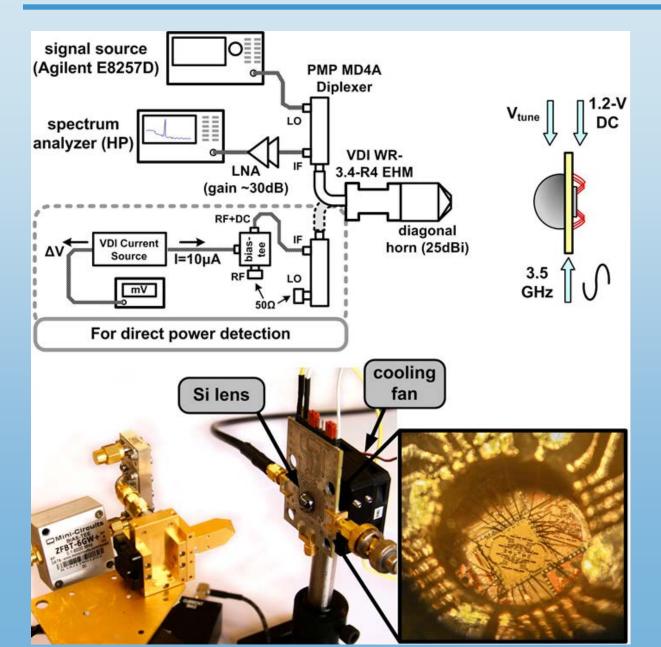

#### **Measurement Setup**

• Two setups for power and frequency.

#### MKR -78.00 dBm ATTEN DdB 10 dB/ 508.0 MHz RL -40.0 dBm MKR 508.0 MHz -78-00 dBm START 200.0 MHz STOP 800.0 MHz RB⊎ 30 kHz VBW 30 kHz S⊎P 1.70 sec

#### b) Power setup

#### The 290 GHz Source

Chip performance

summary

| Center frequency                | 0.29 THz   |  |

|---------------------------------|------------|--|

| Tuning range                    | 13 GHz     |  |

| Peak power                      | 0.76 mW    |  |

| Phase noise<br>(@ 1 MHz offset) | -78 dBc/Hz |  |

| DC power                        | 325 mW     |  |

| Core supply                     | 1.3 V      |  |

| Coupling supply                 | 1.1 V      |  |

#### The 320 GHz Source

Chip performance

summary

| Center frequency                | 0.32 THz   |  |

|---------------------------------|------------|--|

| Tuning range                    | 8.4 GHz    |  |

| Peak power                      | 0.46 mW    |  |

| Phase noise<br>(@ 1 MHz offset) | -77 dBc/Hz |  |

| DC power                        | 339 mW     |  |

| Core supply                     | 1.3 V      |  |

| Coupling supply                 | 1.1 V      |  |

### Outline

- Motivation

- Terahertz Frequency Multipliers

- High Power Terahertz Oscillator Design

- A High Power THz VCO

- THz Radiator Arrays

- Conclusion

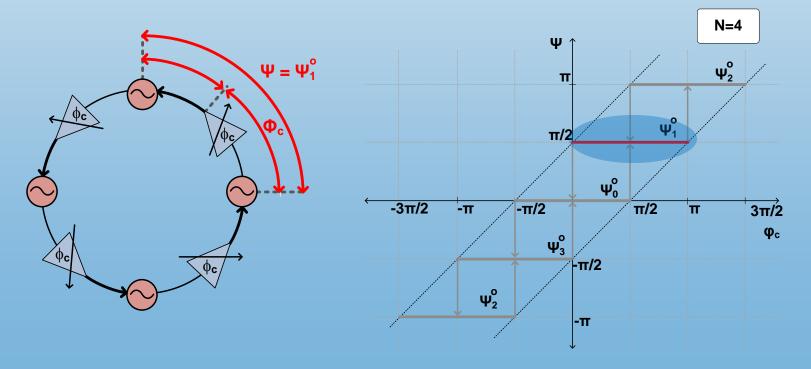

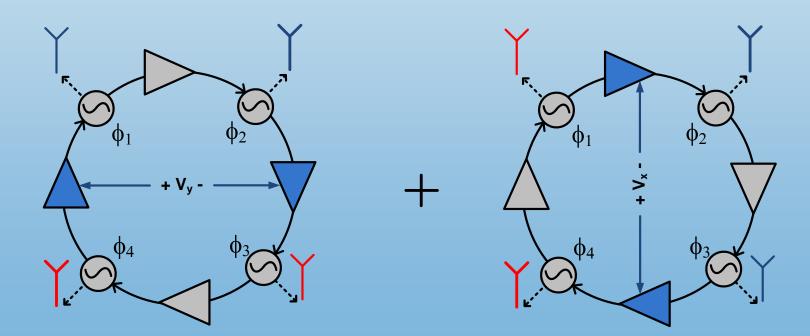

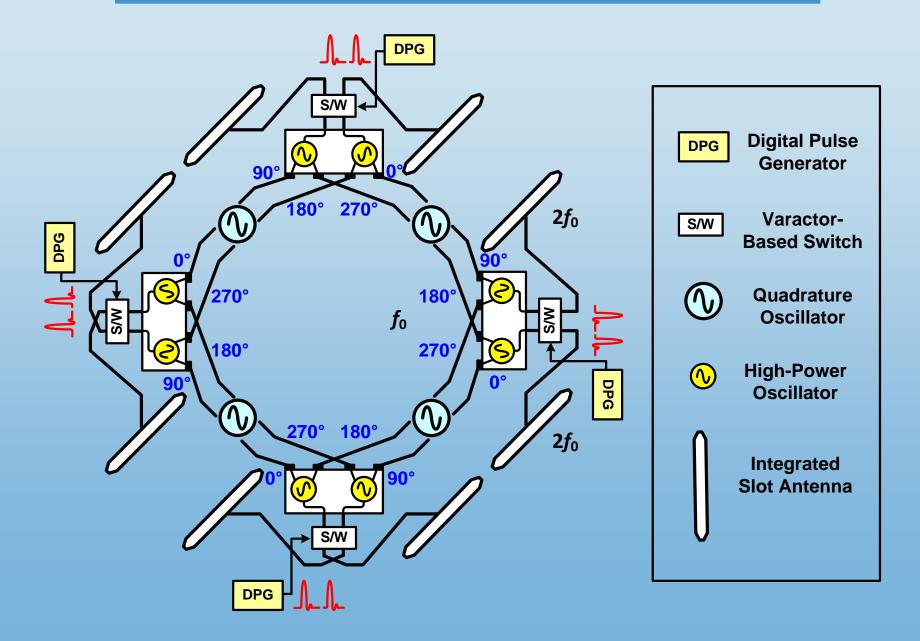

#### A 2x2 Phased Array

- 4 coupled cores radiate separately

- Output power is spatially combined

- Consider two cases

- > Equal change in all  $\Phi_c$ 's:

- ✓ Frequency control

- > Differential change in  $\Phi_c$ 's:

- ✓ Phase control

$$\psi_i^o = \frac{2k\pi}{N} - \frac{1}{N} \sum \phi_c^i + \phi_c^i$$

$$\omega = \omega_0 + K \sin(\frac{1}{N} \sum \phi_c^i - \frac{2k\pi}{N})$$

### **Example of Beam-Forming**

- **V**<sub>v</sub> : Beam steering in y direction

- V<sub>x</sub> : Beam steering in x direction

- Superposition of two differential voltages : 2-D beam forming

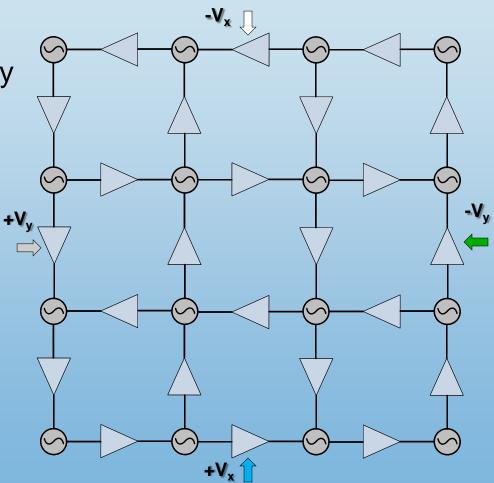

#### **Scalable Architectures**

- Scalability and stability

- Coupling topology

- 2-D beam forming

- Frequency tuning

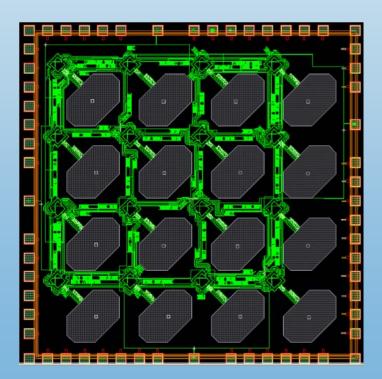

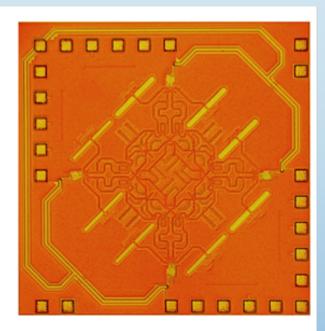

#### A 4x4 Terahertz Phased Array

#### □ Chip fabricated in a CMOS 65nm GP bulk process.

- Simulation results

- Center frequency: 350 GHz

- Tuning range: 8%

- Generated power: 3.2 mW

- Radiated power: 1.4 mW

- EIRP > 100 mW

- 2-D beam forming

- Highly scalable

- □ No global routing

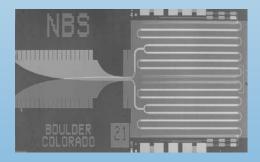

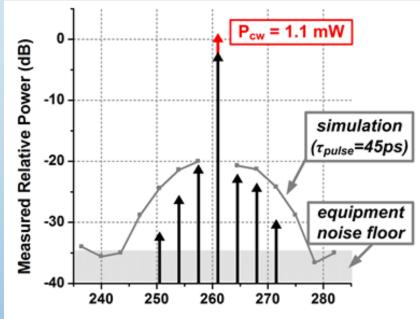

#### **260-GHz Broadband Array**

#### **260-GHz Broadband Array**

#### **260-GHz Broadband Array**

**Radiation Frequency (GHz)**

|                           | ISSCC 2012 [1]         | ISSCC 2012 [2] | VLSI 2011 [3]    | This Work          |

|---------------------------|------------------------|----------------|------------------|--------------------|

| Frequency (GHz)           | 290                    | 280            | 380              | 260                |

| Bandwidth (%)             | 4.5                    | 3.2            | 4                | 9.5                |

| EIRP (dBm)                | N/A                    | 9.4            | -13              | 15.7               |

| <b>Total Output Power</b> | otal Output Power -1.2 |                | N/A              | 0.5                |

| (dBm)                     | -1.2                   | -7.2           | N/A              | 0.5                |

| Phase Noise               | -78dBc/Hz @ 1MHz       | N/A            | N/A              | -78.3dBc/Hz @ 1MHz |

| DC Power (W)              | 0.32                   | 0.81           | 0.36             | 0.8                |

| Technology                | 65nm Bulk CMOS         | 45nm SOI CMOS  | 130m SiGe BiCMOS | 65nm Bulk CMOS     |

#### Comparison

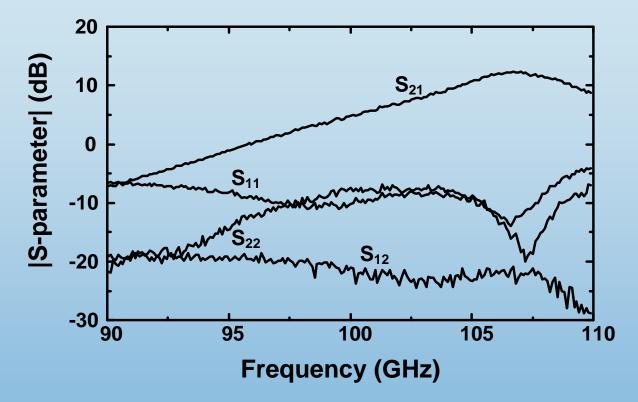

#### **CMOS mm-Wave & THz Amplifiers**

- Signal amplification is challenging in CMOS:

- CMOS scaling is reaching its limit.

- Operation frequency of these systems is close to the maximum oscillation frequency ( $f_{max}$ ) of the transistors.

- Maximum available gain  $(G_{ma})$  of the transistors drops below useful level for most applications.

- PAE drops as the gain drops at high frequencies.

#### We need to boost $G_{ma}$ to its maximum possible value.

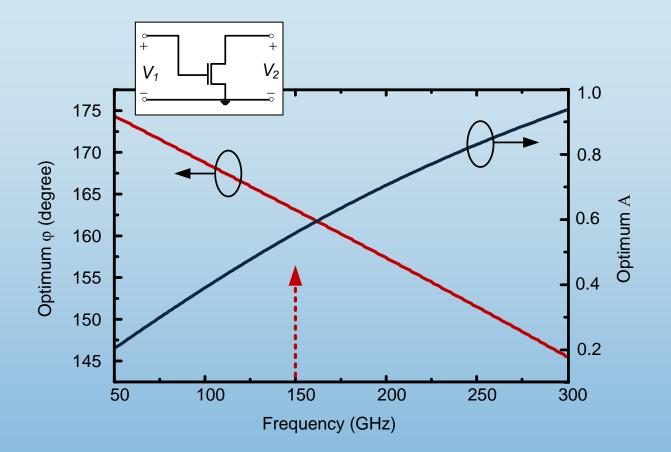

#### **Optimum Conditions**

Assuming most of the input power flows from source to port 1 of the device and most of the output power flows to the load:

$$Gain \cong 1 + \frac{2}{G_{11}} \{ -(G_{11} + A^2 G_{22}) - A | Y_{12} + Y_{21}^* | \cos(\angle (Y_{12} + Y_{21}^*) + \varphi)) \}$$

$$A_{opt} = \frac{|Y_{12} + Y_{21}^*|}{2G_{22}} \qquad \varphi_{opt} = (2k+1)\pi - \angle (Y_{12} + Y_{21}^*)$$

Gain is maximized by providing optimum voltage gain and phase conditions for the device.

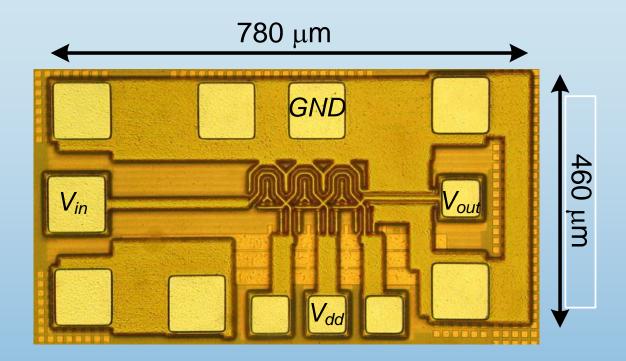

#### **Chip Photo**

- Inductors are implemented using microstrip transmission lines.

- Capacitors are implemented using metal finger capacitors or the capacitance pads.

#### **S-Parameter Measurement**

- Power gain of 12.5 dB is achieved at 107 GHz.

- Input and output reflection coefficients are -13 dB and -19 dB, respectively.

- DC power consumption is 31 mW.

### Outline

- Motivation

- Terahertz Frequency Multipliers

- High Power Terahertz Oscillator Design

- A High Power THz VCO

- THz Radiator Arrays

- Conclusion

## Summary

- It is critical to have a good device understanding to squeeze out the maximum power/gain

- E/M modeling is critical

- Built-in self test is highly desirable

- RF engineers need to learn more microwave/device physics

- For some applications CMOS is not sufficient and compound semiconductors (especially GaN) show great potential.

# The Next Frontier for Circuit Designers: CMOS THz Systems

#### $\overset{}{\longrightarrow}$

Ehsan Afshari Cornell University (http://unic.ece.cornell.edu)

November 2012