Rohit Bhasin

Senior Technical Sales Engineer

Digital Verification and Design Validation Solutions

#### Agilent Technologies

"Overview of Significant Changes in Computer Architecture and Tackling the Challenges of High Speed Digital Interfaces"

...with a Focus on PCI and Memory

# Agenda

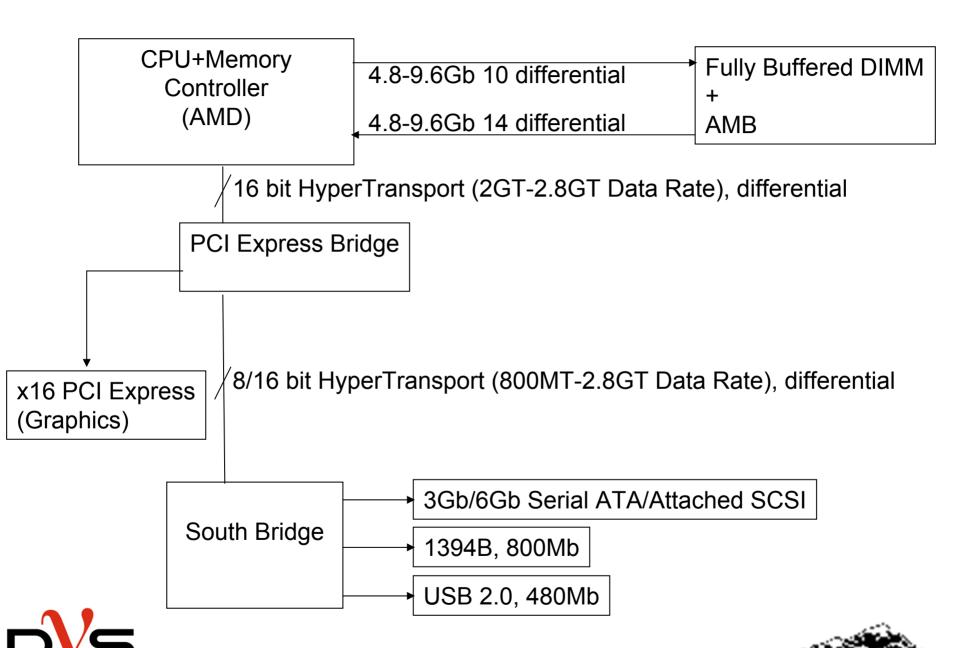

- Changes in chipsets

- Intro to current/new interfaces

- Commonalties in interconnects (serial/parallel)

- Tool lifecycle

- PCI Express (including new tools)

- Fully Buffered DIMM (including new tools)

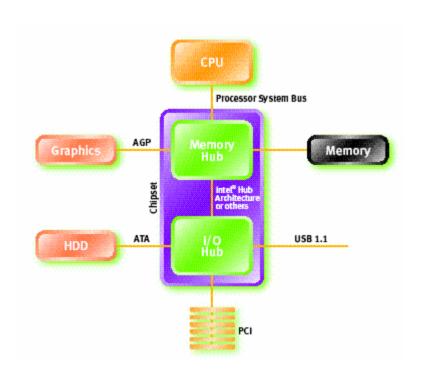

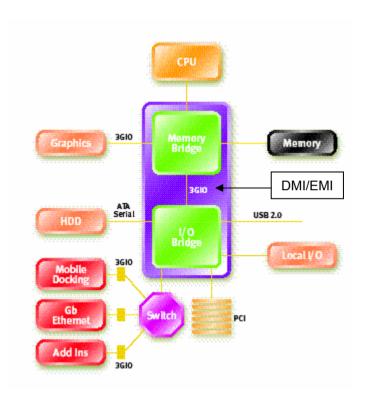

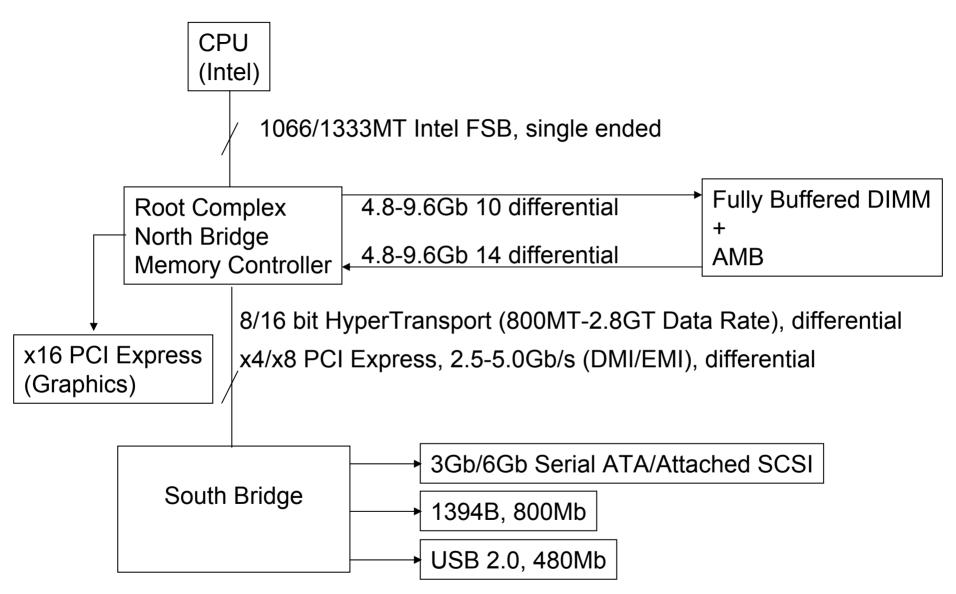

## Computer System Topologies

Mid 90's

**Circa 2002**

enabling digital innovation

#### Digital Technologies in the Bay Area

- Serial ATA/Attached SCSI

- •Fully Buffered DIMM

- PCI Express

- •PCI-X 2.0

- Hypertransport

- •Intel FSB

- •DDR I/II/III

- •USB 2.0/Firewire 1394B

- •Infiniband 1x, 4x, 12x

- •FibreChannel 4Gb/s, 6/8Gb/s, 10Gb/s

- •1Gb/s, XAUI 10Gb/s Ethernet over copper

- Advanced TCA

- •SPI 4.2

- Serial Rapid I/O

- Digital Video Interface

- •High Definition Multimedia Interface

10 GIGABIT ETHERNET ALLIANCE

#### Transitions and Commonalities in Interconnect Technology

#### **High Speed Serial**

- Differential Signaling

- Embedded Clock, CDR

- Spread Spectrum, EMI Reduction

- Reduced Pin/Signal Count

- Packet Based Transactions

- Improved Quality of Service

#### High Speed Parallel

- Differential (e.g. FBDIMM, HyperTransport)

- Single Ended (e.g. DDR2, DDR3, Legacy Intel FSB)

- Clk rates increased (multi-gigabit)

- Reduced slot count (e.g. PCI-X, DDR3)

- Improved Quality of Service, ECC

- Reduced Pin/Signal Count

## Lifecycle Tools for Multi-Gigabit Designs

| Design Simulation                                         |                                         | Device and Board                                                         |                  | System                                              | Mfg.            |

|-----------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------|------------------|-----------------------------------------------------|-----------------|

| Link to<br>Model<br>Database                              | Devices & Interconnect Characterization | Prototype<br>Characterization<br>& Validation                            | Bring-Up<br>Test | System<br>Integration<br>& Functional<br>Validation | Chipset<br>Test |

|                                                           | Physic                                  | cal Layer Link Layer                                                     |                  |                                                     |                 |

| Passive Interconnect Measurements - Impedance, Crosstalk, |                                         | Active Live Signal Measurements - Voltage, Jitter, BER, Timing, Packets, |                  |                                                     |                 |

| Device Characterization & Modeling Services               |                                         | Serial/Parallel BERT                                                     |                  |                                                     |                 |

| a wodeling Services                                       |                                         | Pulse Generator                                                          |                  |                                                     |                 |

| ADS )                                                     | Physical Layer<br>Test System           | Logic Analysis System & Probes                                           |                  |                                                     |                 |

| SPICE/IBIS                                                |                                         | Sampling Scope, jitter capable                                           |                  |                                                     |                 |

|                                                           |                                         | 13 GHz Infiniium Real Time Scope                                         |                  |                                                     |                 |

| IConnect                                                  | Sampling Scope W/TDR Network Analyzer   | Robust scope Physical Layer Probing System                               |                  |                                                     |                 |

| WALE                                                      |                                         | Parametric Fixtures (FBD, PCI-E)                                         |                  |                                                     |                 |

|                                                           |                                         |                                                                          |                  |                                                     |                 |

# PCI Express Validation Methodologies

Rohit Bhasin Agilent Technologies

> Presented at PCI-SIG Developers Conference June 2004

## PCI Express Debug Challenges

## PCI Express Validation Steps

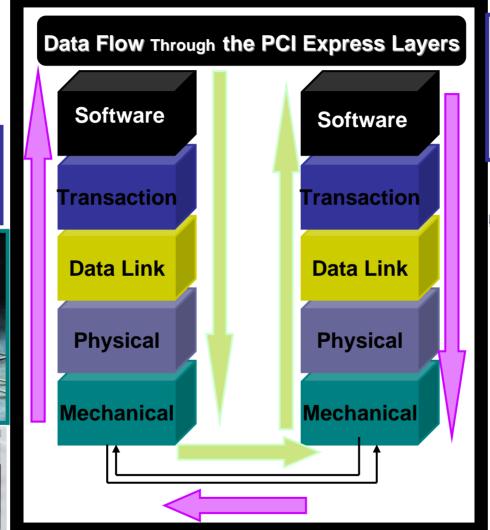

Signal Integrity - Verify the 2.5/5.0 Gb design

- Eye Measurements

- Capture waveforms

- Measurement on parameters (jitter analysis, mask test, etc.)

- Board and Component characterization

- BERT

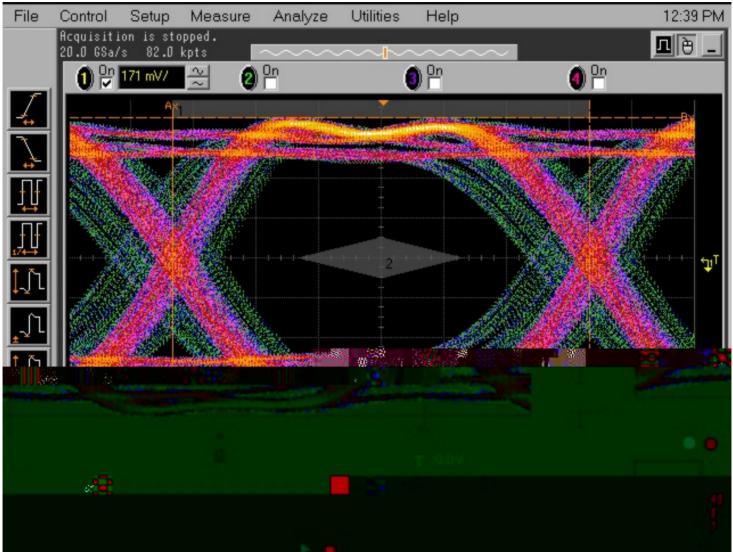

## Serial Data Analysis Toolkit

- Clock recovery and serial data analysis for highspeed serial data signals

- Masks for PCI Express, Serial ATA/Attached SCSI, Fibre Channel, and XAUI

- Real-time eye diagram display

- Time interval error (TIE) jitter measurement

- First-order or second-order PLL clock recovery, and PCI Express clock recovery (provided by PCI-SIG)

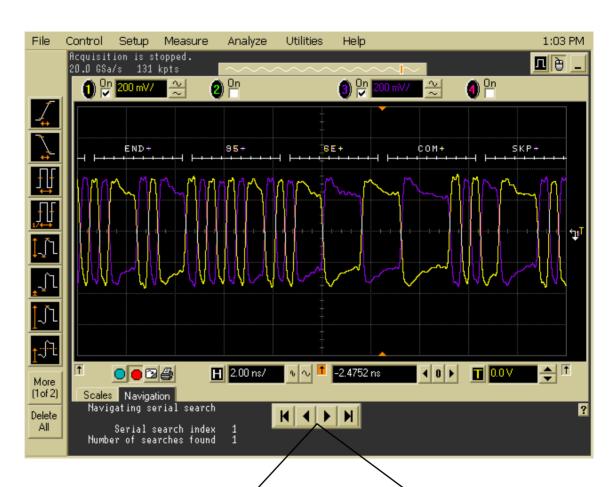

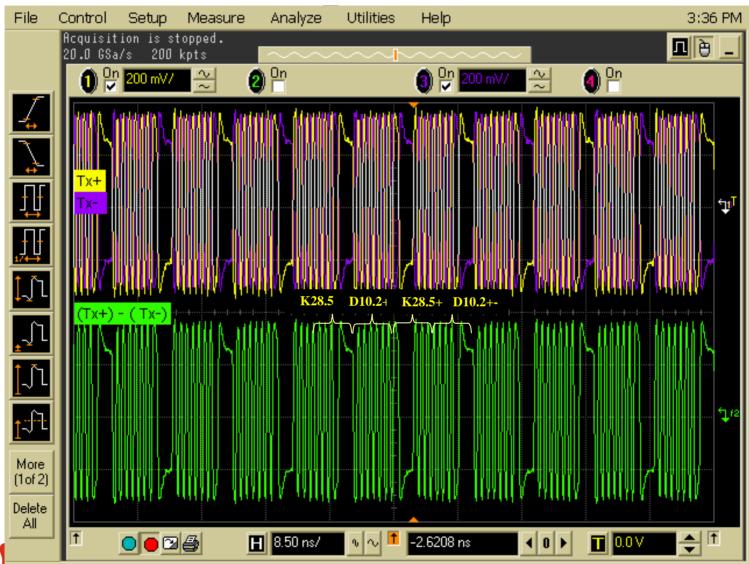

## An example using the Serial Data Tool

# Features and Capabilities

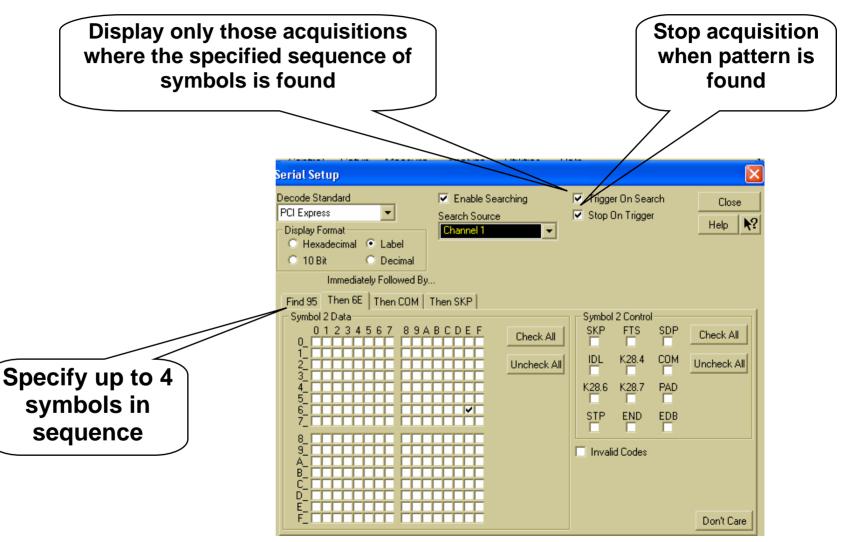

- 8b/10b decoding

- 8b/10b search

- 8b/10b trigger

- Real time eye mask violation unfolding

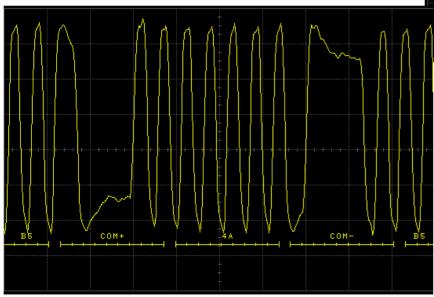

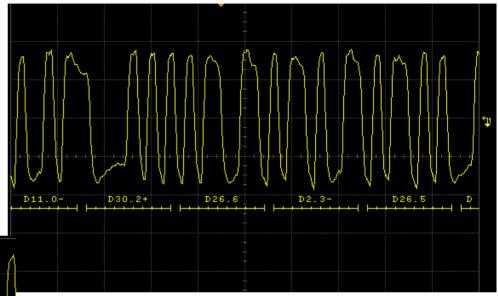

# 8b/10b Decoding

Symbols in the serial data stream can be decoded and displayed as hex or decimal values, or as labels

# Search and trigger

# Search Navigation

Navigate to all the instances of the specified sequence of symbols using the arrow keys

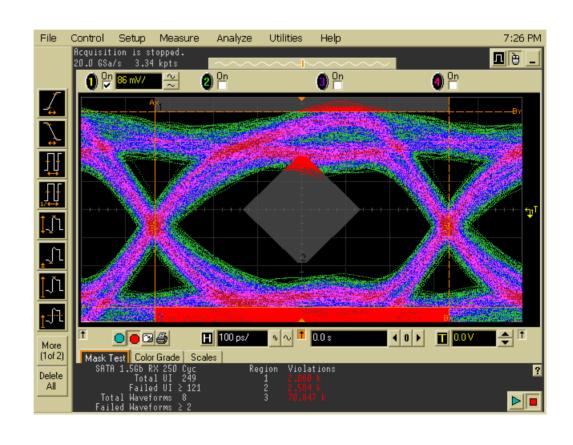

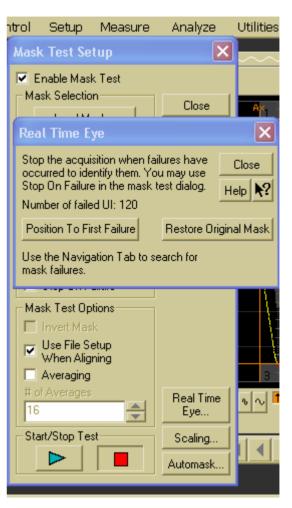

# Locating mask violations and failures

The real-time eye combined with the PCI Express mask test indicates there were multiple violations. But how do you gain insight into the individual violations by looking at the composite eye?

# Locating mask violations

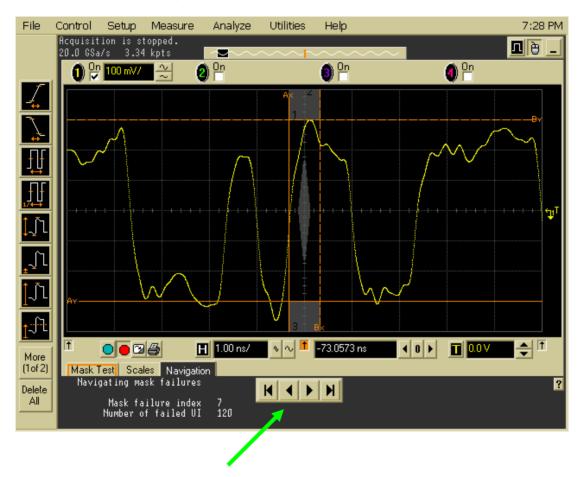

Using the controls, we can instruct the scope to go to the first violation in the serial data stream.

# Locating mask violations

You can use the arrow keys to view each violation individually.

# PCI Express Compliance Test Setup (add-in card)

## PCI Express TS-1 Compliance Test

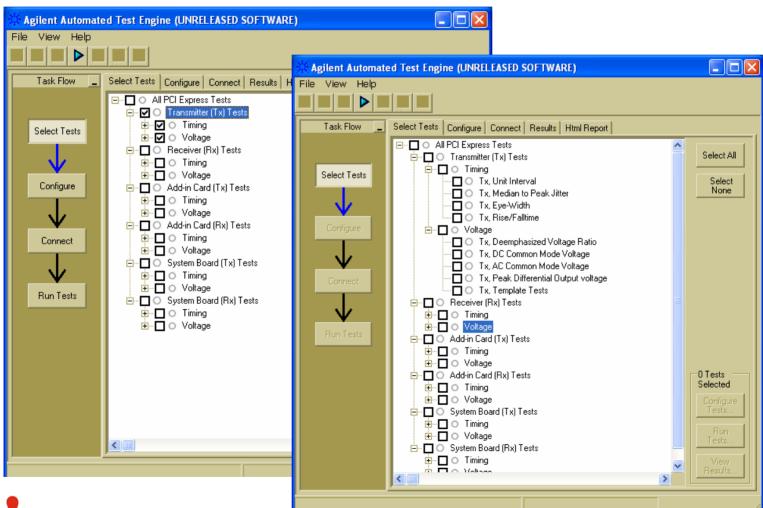

# PCI Express Compliance and Validation Tool Suite

## PCI Express Compliance Report Showing Marginal Performance Analysis

**Pass Test Name**

Spec Range

**PCI Express Compliance Report**

Overall Result: FAIL (3 of 35 Tests Failed)

Test Configuration Details

Test Date Jan 27, 2004, 21:04:30

Instrument ID Agilent Technologies, 54855A, No Serial, A.03.18,001, EZJ, SDA

Probe ID 1134A

Serial Number Jan 27, 2004, 21:04:30

Calibration Status All Passed

#### **Summary of Results**

Margin Thresholds

Warning <=3%

Critical <=

# PCI Express Validation Steps

Signal Integrity - Verify the 2.5/5.0 Gb design

Probing

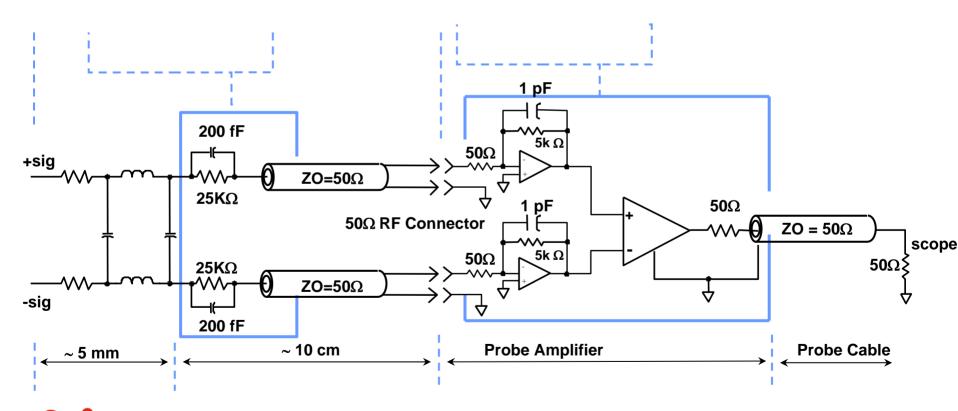

## **New Probe Architectures**

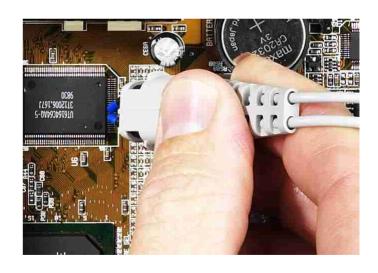

## Making Good Connections (Gen 1)

### Flexibility Probe Systems

- Browser probe head

- Solder-in probe head

- Socketed probe head

- SMA probe head

- Differential and single-ended

**Probing in confined spaces**

## **Browser Probe**

- 6 GHz BW

- Most versatile for hand-held probing

- Z-Axis compression enhances connection

- Adjustable tip spans

- Ergonomic sleeve

- Replaceable damping resistor tips

- Can be used with probe stand holder

# Solder-in Probe (Gen 1)

- 8 GHz BW

- Use for high bandwidth connection

- Least space requirement

- Replaceable damping resistors (8 mil)

## Socketed Probe

- 7 GHz BW

- Semi-permanent attachment

- Move between multiple test points

- Adapter for standard headers

- Standard axial lead resistors (20 mil)

- Same resistors support Logic Analyzer Flying Lead Set

## Differential SMA Probe

- 50-Ohm Input Impedance

- 7 GHz BW

- Span-adjustable semi-rigid coax

- High common-mode rejection

- Cable loss compensation

- Cost effective adapter for existing probe amp

- Can apply DC offset bias

# 12 Ghz Active Probes (Gen 2)

| Probe Amplifiers         |            |  |

|--------------------------|------------|--|

| Specified Bandwidth      | 12 GHz     |  |

| Characterized Probe Tips | Yes        |  |

| Noise Referred to Input  | 2.5 mV rms |  |

| Attenuation              | 3.45:1     |  |

| Diff Dynamic Range       | 3.3 V p-p  |  |

| DC Offset Range          | +/- 16 V   |  |

| Maximum Voltage          | +/- 30 V   |  |

Offers excellent bandwidth, characterized performance for various probe tips, low noise, low attenuation, good dynamic range and small size

enabling digital innovation

## 12 GHz Differential SMA Adapter Probe Head

**12 GHz Differential Solder-in Probe Head:** 210 fF input capacitance, 50 kOhm input resistance, 4" reach, 2 mm probe head size at taper, 0.2-3.3 mm lead span

#### 12 GHz Differential Browser:

210 fF input C, 50 kOhm input R, 0.2-3.3 mm lead span

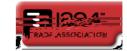

- Logic Layer PCI-E probing

- DLLP and TLP debug

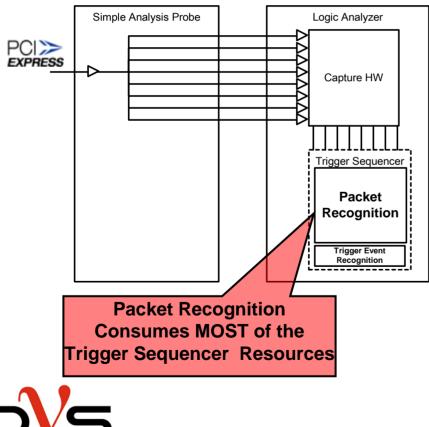

### Tools for PCI-Express Logic Layer debug

Packet Analysis Probe

**Logic Analyzer**

Config./OS

Software

Transaction

**Data Link**

**Physical**

**Mechanical**

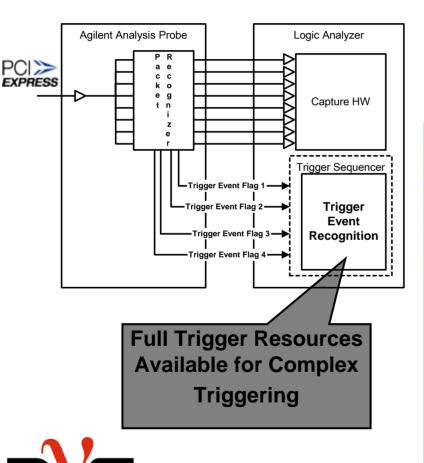

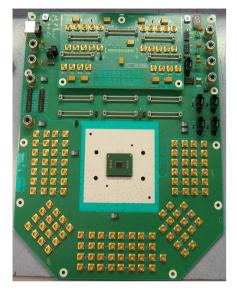

## PCI Express Packet Analysis Probe

## Digital Validation for PCI Express

## - Logic Analysis Value Proposition

- Probing

- Non Intrusive passive observation of data flow

- Validation of Add-in Cards Chip-to-Chip Architectures

- Packet Analysis and Display

- Dedicated Packet Triggering in LA

- Dedicated FPGA Hardware Pattern Recognizers in Probe

- Software Decode Tool runs on LA

- Full System Validation

- Cross-Bus Analysis (Time Correlated)

- Cross-triggering correlation between scope and analyzer

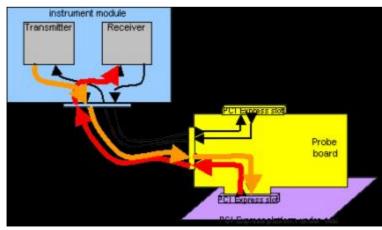

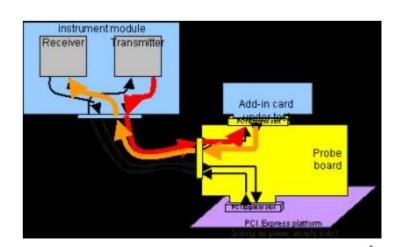

# Logic Analysis PCI Express Connection

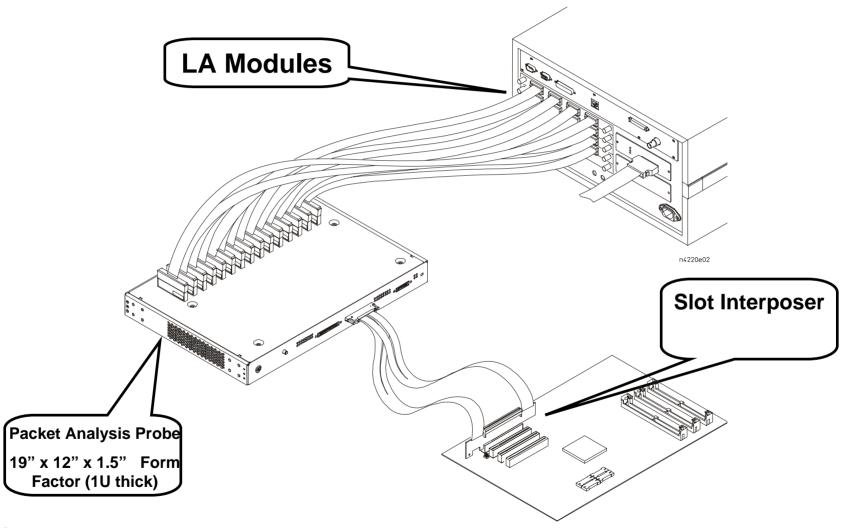

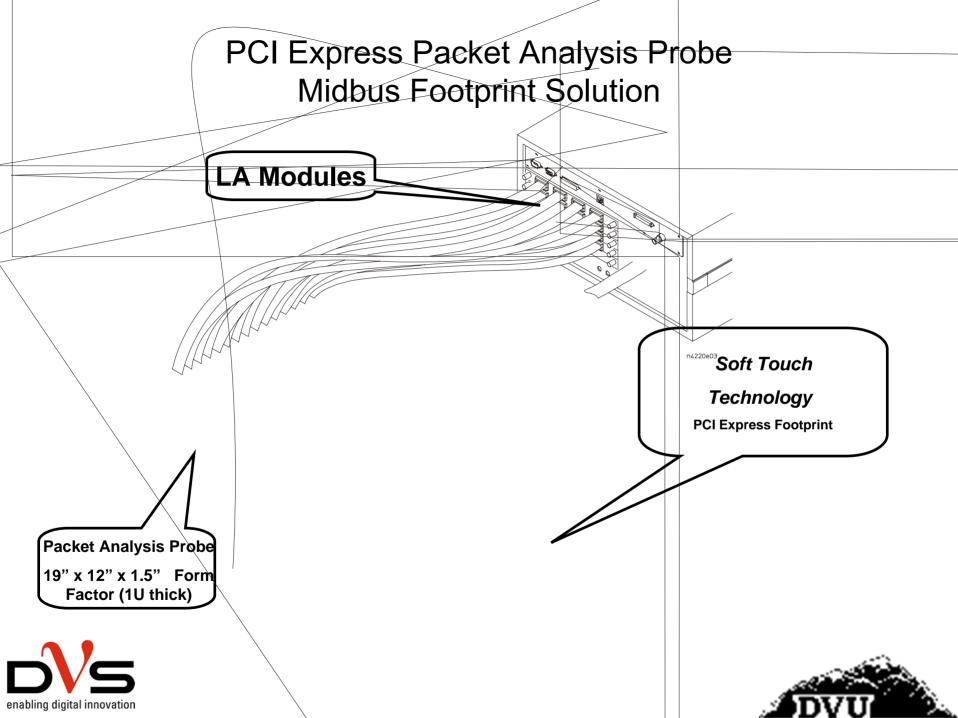

#### PCI Express Packet Analysis Probe Slot Interposer Solution

# Connect: Low Intrusion is a must PCI

- Types of connection

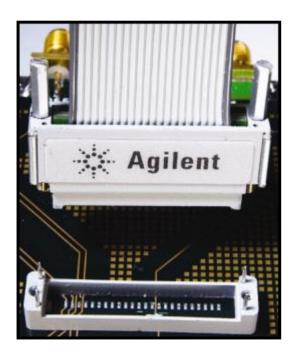

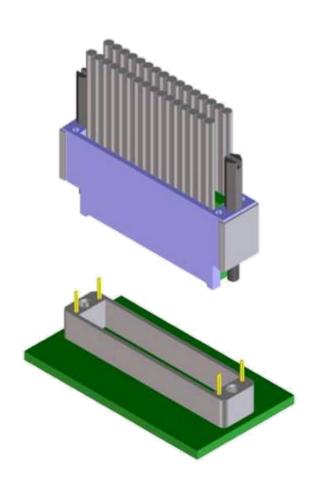

- Chip-to-Chip Link PCI Express FOOTPRINT (Soft Touch TECHNOLOGY)

- Card Edge

- Slot connector/interposer

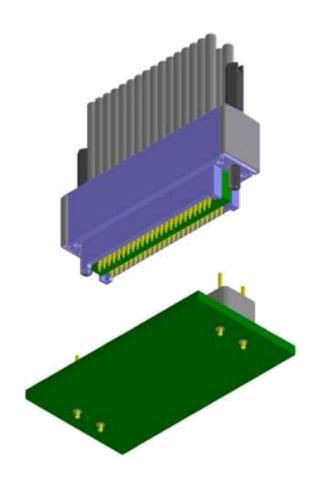

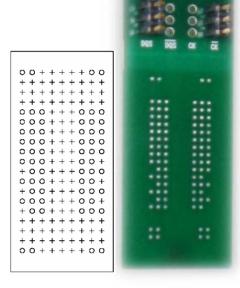

# Midbus Probe

# Mid-Bus Footprint Routing

## Mid-Bus Connector Layout

|              |             |                       |                  |        |         |           |            |      |        |               |                | _    |

|--------------|-------------|-----------------------|------------------|--------|---------|-----------|------------|------|--------|---------------|----------------|------|

|              | one d       | irectio               | n of x           | 16:    | other   | directi   | on of      | x16: | both ( | direction     | ons of         | x8:  |

|              |             |                       | 0                |        |         |           | 0          |      |        |               | 0              |      |

|              |             | 1                     |                  |        |         | 1         |            |      |        | 0             |                |      |

| Additional   |             |                       | 2                |        |         |           | 2          |      |        |               | 1              |      |

| , idditional |             | 3                     |                  |        |         | 3         |            |      |        | 1             |                |      |

| x16          |             | _                     | 4                |        |         | _         | 4          |      |        | _             | 2              |      |

| XIO          |             | 5                     | 6                |        |         | 5         | 6          |      |        | 2             | 3              |      |

| Layouts      |             | 7                     | U                |        |         | 7         | U          |      |        | 3             | 3              |      |

|              |             | ·                     | 8                |        |         | ,         | 8          |      |        | 3             | 4              |      |

| Supported    |             | 9                     | Ŭ                |        |         | 9         | ŭ          |      |        | 4             |                |      |

| Supported    |             |                       | 10               |        |         |           | 10         |      |        |               | 5              |      |

|              |             | 11                    |                  |        |         | 11        |            |      |        | 5             |                |      |

|              |             |                       | 12               |        |         |           | 12         |      |        |               | 6              |      |

|              |             | 13                    |                  |        |         | 13        |            |      |        | 6             |                |      |

|              |             |                       | 14               |        |         | 4-        | 14         |      |        | _             | 7              |      |

|              |             | 15                    |                  |        |         | 15        |            |      |        | 7             |                |      |

|              |             |                       |                  |        |         |           |            |      |        |               |                |      |

|              | hoth /      | direction             | on of S          | ) v/1· | hoth (  | lirooti   | on of 2    | v2.  | hoth ( | direction     | on of 2        | v1·  |

|              | וווטטנוו    | anecn                 |                  | λ4.    | וווטטוו | mecn      | אוט ווע    | ΧΖ.  |        | มแบบแ         | JII OI 2       | X I. |

|              |             |                       | $\cap$           |        |         |           | 0          |      |        |               |                |      |

|              |             | 0                     | 0                |        |         | 0         | 0          |      |        |               | 0              |      |

|              |             | 0                     | 0                |        |         | 0         | 0          |      |        | 0             |                |      |

| Additional   |             | 0                     |                  |        |         | 0         |            |      |        |               | 0              |      |

| Additional   |             |                       |                  |        |         |           |            |      |        | 0             | 0              |      |

|              |             |                       | 1                |        |         |           | 1          |      |        | 0             | 0<br>nc        |      |

|              |             | 1 2                   | 1                |        |         | 1         | 1          |      |        | 0<br>nc       | 0<br>nc        |      |

| .ayouts      |             | 1                     | 1 2 3            |        |         | 1         | 1<br>nc    |      |        | 0<br>nc       | nc nc          |      |

| .ayouts      | •           | 1 2 3                 | 1 2              |        |         | 1 nc      | 1<br>nc    |      |        | nc nc         | 0<br>nc        |      |

|              | •           | 1 2                   | 1 2 3            |        |         | 1<br>nc   | 1 nc nc    |      |        | 0<br>nc<br>nc | nc nc nc       |      |

| .ayouts      | •           | 1 2 3                 | 1 2 3            |        |         | 1 nc nc   | 1<br>nc    |      |        | nc nc         | nc nc          |      |

| .ayouts      | <b>&gt;</b> | 1 2 3                 | 1<br>2<br>3<br>0 |        |         | 1 nc      | 1 nc nc 1  |      |        | nc nc         | nc nc nc       |      |

| .ayouts      | <b>&gt;</b> | 1 2 3                 | 1 2 3            |        |         | 1 nc nc   | 1 nc nc    |      |        | nc nc         | nc nc nc       |      |

| .ayouts      | •           | 1<br>2<br>3<br>0<br>1 | 1<br>2<br>3<br>0 |        |         | 1 nc nc 1 | 1 nc nc 1  |      |        | o nc nc o nc  | nc nc nc       |      |

| .ayouts      | •           | 1<br>2<br>3<br>0<br>1 | 1 2 3 0 1 2      |        |         | 1 nc nc 1 | 1 nc nc nc |      |        | o nc nc o nc  | nc nc nc nc nc |      |

Signal Pair

Polarity can be reversed

Entire Link Lane assignment can be reversed

## Connect: Flying Lead Set

# Logic Analysis PCI Express Validation Steps

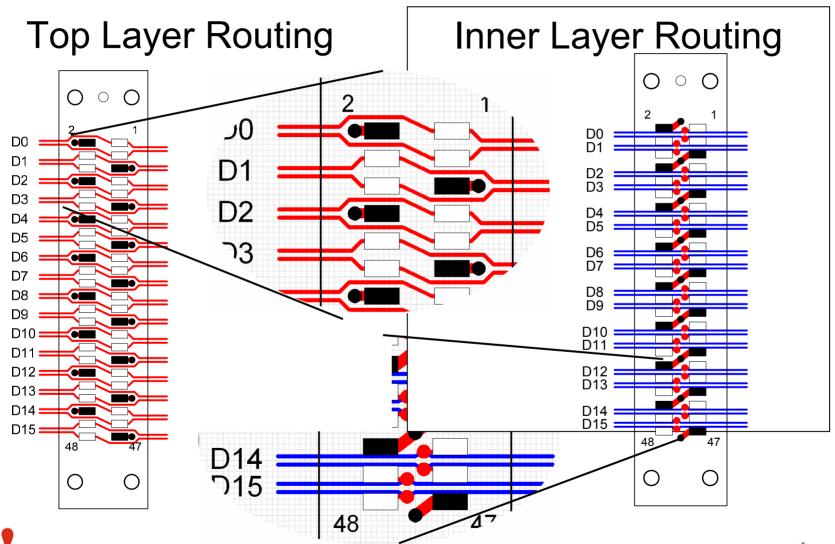

# Acquire: PCI Express Traditional LA

Traditional Serial Analysis Probes

enabling digital innovation

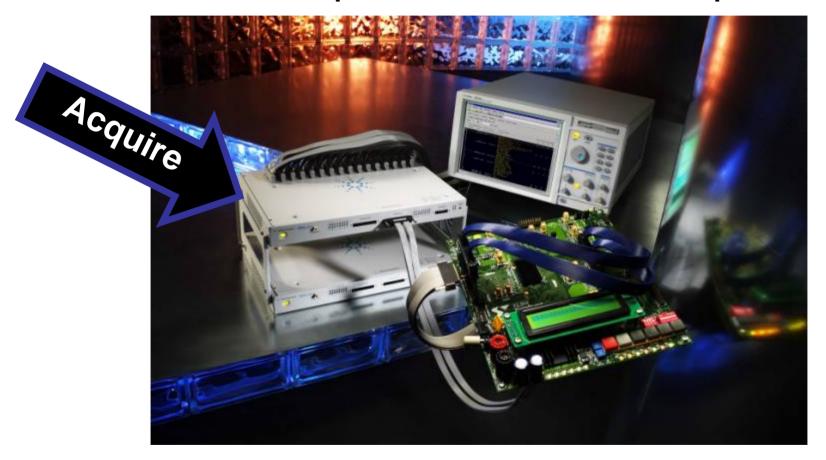

# Acquire: PCI Express Packet Recognition

PCI Express Packet Analysis Probe

enabling digital innovation

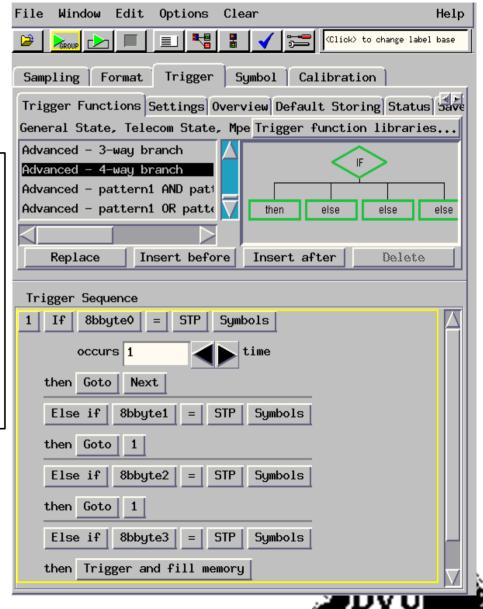

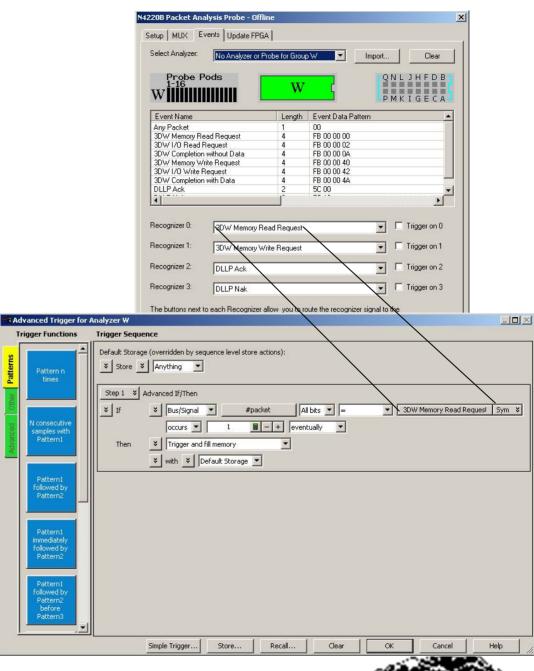

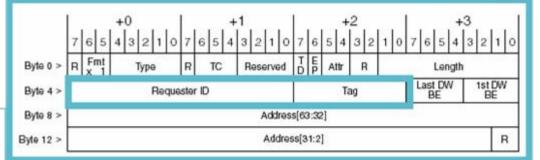

### PCI Express Packet Recognition

- Enhanced Trigger Capability Through Packet Recognition

- 8 Header Recognizers will exist in the Analysis Probe (4 Tx/4 Rx)

- Implemented in h/w, includes GUI

- 24 Bytes in each Header Recognizer (Recognition into Data Portion)

- Recognizers send simple event notification back to Logic Analyzer

- Full, Robust Logic Analyzer Sequencing will be available on event notification bits.

| Recognizer 0: | 3DW Memory Read Request  | ▼ Trigger on 0   |

|---------------|--------------------------|------------------|

| Recognizer 1: | 3DW Memory Write Request | ▼ Trigger on 1   |

| Recognizer 2: | DLLP Ack                 | ▼ ☐ Trigger on 2 |

| Recognizer 3: | DLLP Nak                 | ▼ ☐ Trigger on 3 |

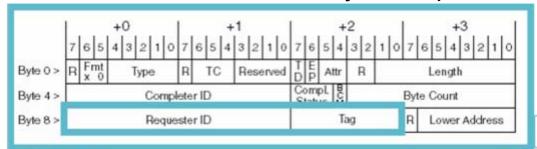

# Logic layer Validation Challenges

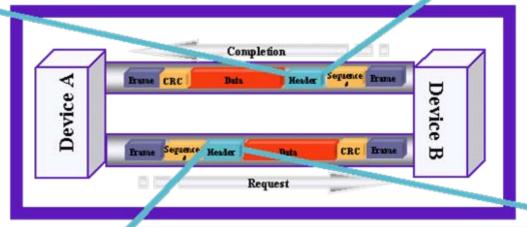

"Read" & "Write" Cycles replaced by Packets

**Completion Header Format**

Requester Header Format For 64-bit addressing of memory

# Validation Steps

### Defining a Packet

# Logic Analysis PCI Express Validation Steps

# Display: Packet Decode

| ose for press ESC | Iools Markers Run/Stop Listing Window Help        | ensumana and in |     |     |     |     |      | Scenii I |     |     |     |     | _     |       | 20000 |

|-------------------|---------------------------------------------------|-----------------|-----|-----|-----|-----|------|----------|-----|-----|-----|-----|-------|-------|-------|

| bee manned        | Packet Decode                                     | Bad CRC         |     |     |     |     | Lane | Data     |     |     |     |     |       |       | Ch    |

| -10               |                                                   | 00              | 4 A | 4.4 | 4.6 | A.P | 4A   | 4.8      | 44  | AP  | 4A  | 4.8 | D10.2 | D10.2 | D10.  |

| -9                |                                                   | 00              | 4.4 | 44  | 4.4 | 4A  | 4 A  | 41       | 48  | 4.4 | 4 A | 41  | D10.2 | D10.2 | D10.  |

| -8                |                                                   | 00              | 4 A | 4.1 | 48  | 4A  | 4A   | 41       | 4.E | 4.8 |     | 41  |       | D10.2 |       |

| -7                |                                                   | 00              | 44  | 4.8 | AP  | 4A  | 4.8  | 44       | 4.8 | 4.8 | 44  | 44  |       | D10.2 |       |

| -6                |                                                   | 00              | 4.4 | 41  | 4.4 | 4.4 | 4.4  | 41       | 4.4 | 44  | 4.4 | 41  |       | D10.2 |       |

| -5                |                                                   | 00              | 4A  | 44  | 44  | 44  | 4.4  | 4.k      | 44  |     |     | 44  |       | D10.2 |       |

| -4                |                                                   | 00              | BC  | BC  | BC  | BC  | BC   | BC       | BC  | BC  | BC  | BC  |       | K28.5 |       |

| -3                |                                                   | 00              | 10  | 10  | 10  | 10  | 10   | 10       | 10  | 10  | 10  | 10  |       | K28.0 | _     |

| -2                |                                                   | 00              | 10  | 10  | 10  | 10  | 10   | 10       | 10  | 10  | 10  | 10  |       | K28.0 |       |

| -1                | A                                                 | 00              | 1C  | 10  | 10  | 10  | 10   | 10       | 10  | 10  | 10  | 10  |       | K28.0 |       |

| 0.1               | Start TLP = STP ******************                | 00              | I B | 00. | UU. | UU  | 00   | .00      | UU  | 00  | 00  | 00  | K27.7 | D00.0 | DOO.  |

| 0.1               | Reserved = 0 Hex<br>TLP Sequence Number = 000 Hex |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.3               | Reserved1 = 0 Hex                                 |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.4               | Fmt = 3DW header, no data                         |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.5               | Type - Memory Read Request                        |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.6               | Reserved2 = 0 Hex                                 |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.7               | TC - TCO                                          |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.8               | Reserved3 = 0 Hex                                 |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.9               | TD = TLP Digest Not Present                       |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.10              | EP = TLP Not Poisoned                             |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.11              | Attributes = Default Ordering, Defaul             |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.12              | Reserved4 = 0 Hex                                 |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.13              | Length = 000 Hex                                  |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.14              | Requester ID = 0000 Hex                           |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.15              | Tag = 00 Hex                                      |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.16              | Last DW Byte Enable = O Hex                       |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.17              | First DW Byte Enable = 0 Hex                      |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.18              | Address[31:2] = 0000 0000 Hex                     |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.19              | Reserved5 = 0 Hex                                 |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 0.20              | LCRC = c779 bbd1 Hex (GOOD)                       |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

|                   | End TLP - END                                     |                 |     |     |     | FD  |      | F7       | F7  | F7  |     | F7  |       | D27.5 |       |

| 0.00              | Start TLP = STP ******************                | 00              | FB  | 00  | 00  | 01  | .00  | 00       | 00  | 00  | 00  | 00  | K27.7 | D00.0 | D00.  |

| 2.1               | Reserved = 0 Hex                                  |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 2.2               | TLP Sequence Number = 000 Hex                     |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 2.3               | Reserved1 = 0 Hex                                 |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 2.4               | Fmt = 3DV header, no data                         |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 2.5               | Type = Memory Read Request-Locked                 |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 2.6               | Reserved2 = 0 Hex<br>TC = TCO                     |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 2.8               | Reserved3 = 0 Hex                                 |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 2.9               | TD = TLP Digest Not Present                       |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

| 2.10              | EP = TLP Not Poisoned                             |                 |     |     |     |     |      |          |     |     |     |     |       |       |       |

# Packet Decode / Display (TLP)

| K/D          | Time                    | Packet Decode                                                                                                                                                                                                                                                                                        | Data0    | Data1    | Data2    |

|--------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|

| Binary       | Absolute                | Text                                                                                                                                                                                                                                                                                                 | Hex      | Hex      | Hex      |

| 1000         | 0 s                     | Start TLP                                                                                                                                                                                                                                                                                            | FB       | 00       | 00       |

| 0000         | 20.000 ns               | Reserved = 00 Hex Packet Sequence Number = 00 Hex Reserved = 0 Binary Global Format = 00 Binary (3DW header, no data) Type = 04 Hex (Configuration Read Type 0) Reserved = 0 Binary TC = 000 Binary Reserved = 00 Hex Attr = 00 Binary Reserved = 00 Binary Length = 000 Hex Requester ID = 0000 Hex | 00       | 00       | 00       |

| 0000         | 40.000 ns               | Tag = 00 Hex                                                                                                                                                                                                                                                                                         | 00       | 00       | 00       |

| 0000         | 60.000 ns               | Last DW BE = 0 Hex First DW BE = 0 Hex Bus Number = 00 Hex Device Number = 00 Hex Function Number = 0 Hex Reserved = 0 Hex Ext. Reg Address = 0 Hex Register Address = 00 Hex TLP Digest = 0 Binary EP = 0 Binary 32b CRC: 0x00000000                                                                | 00       | 00       | 00       |

| 0001<br>1000 | 80,000 ns<br>100,000 ns | End<br>Start TLP                                                                                                                                                                                                                                                                                     | 00<br>FB | 00<br>00 | 00<br>00 |

### Packet Decode / Display (DLLP)

|        | - 1       |                                          | - 1   | I (I  | -1    |

|--------|-----------|------------------------------------------|-------|-------|-------|

| K/D    | Time      | Packet Decode                            | Data0 | Data1 | Data2 |

| Binary | Absolute  | Text                                     | Hex   | Hex   | Hex   |

| 1000   | 10.340 us | Start DLLP                               | 5C    | 10    | 00    |

|        |           | Type = 1 Hex (Nak)                       |       |       |       |

|        |           | Must be zero = 0 Hex                     |       |       |       |

|        |           | Reserved = 00 Hex                        |       |       |       |

|        |           | Reserved = 00 Hex                        |       |       |       |

| 0001   | 10.360 us | End                                      | 01    | 00    | 00    |

|        |           | AckNak_Seq_Num = 01 Hex                  |       |       |       |

|        |           | 16b CRC: 0x0000                          |       |       |       |

| 1000   | 10.380 us | Start DLLP                               | 50    | 20    | 00    |

|        |           | Type = 2 Hex (PM)                        |       |       |       |

|        |           | PM = 0 Hex (PM_Enter_L1)                 |       |       |       |

|        |           | Reserved = 00 Hex                        |       |       |       |

|        |           | Reserved = 00 Hex                        |       |       |       |

| 0001   | 10.400 us | End                                      | 00    | 00    | 00    |

|        |           | Reserved = 00 Hex                        |       |       |       |

|        |           | 16b CRC: 0x0000                          |       |       |       |

| 1000   | 10.420 us | Start DLLP                               | 5C    | 21    | 00    |

|        |           | Type = 2 Hex (PM)                        |       |       |       |

|        |           | PM = 1 Hex (PM_Enter_L2)                 |       |       |       |

|        |           | Reserved = 00 Hex                        |       |       |       |

|        |           | Reserved = 00 Hex                        |       |       |       |

| 0001   | 10.440 us | End                                      | 00    | 00    | 00    |

|        |           | Reserved = 00 Hex                        |       |       |       |

|        |           | 16b CRC: 0x0000                          |       |       |       |

| 1000   | 10.460 us | Start DLLP                               | 50    | 22    | 00    |

|        |           | Type = 2 Hex (PM)                        |       |       |       |

|        |           | PM = 2 Hex (PM_Active_State_Request_L0s) |       |       |       |

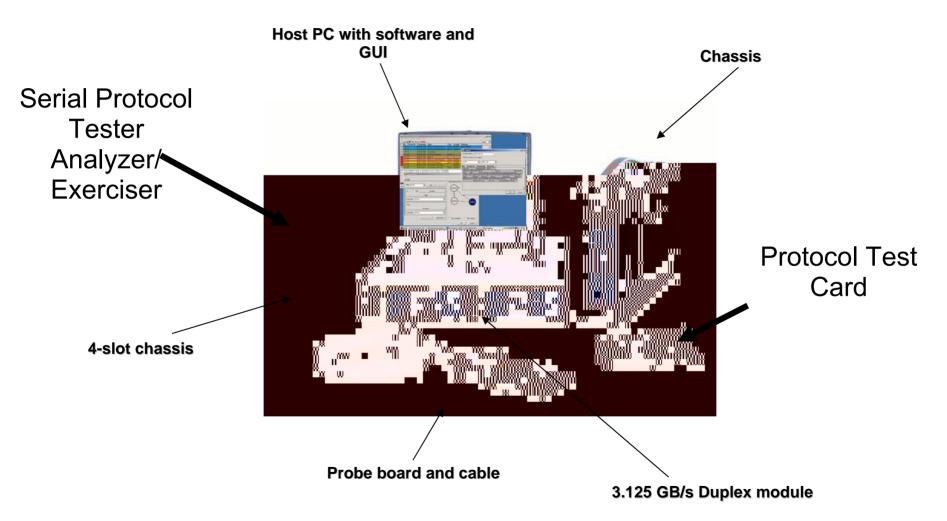

### Protocol Verification Challenges

Protocol Variations / Maximum Load

- Maintain system stability over different configurations

- What happens if the link is fully populated with packets?

- Does my system still work if an add-in card is inserted that implements the protocol differently?

- How can I tell if my design is protocol compliant?

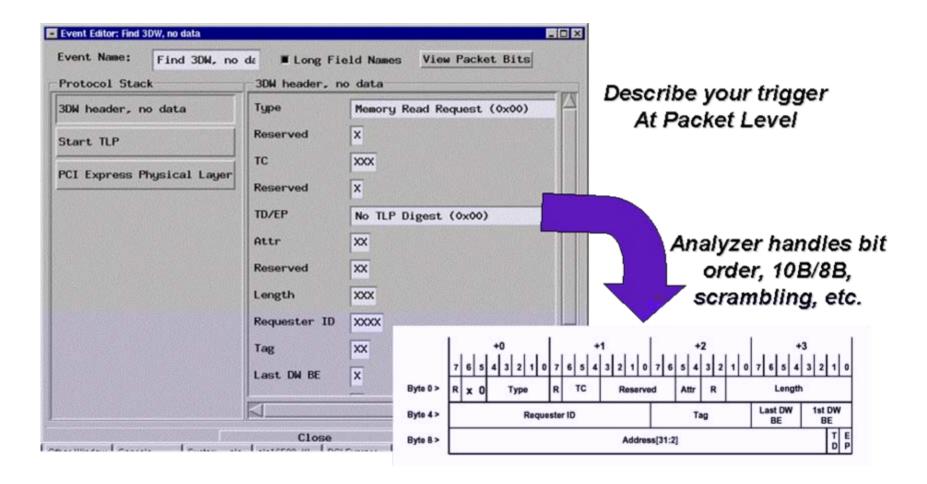

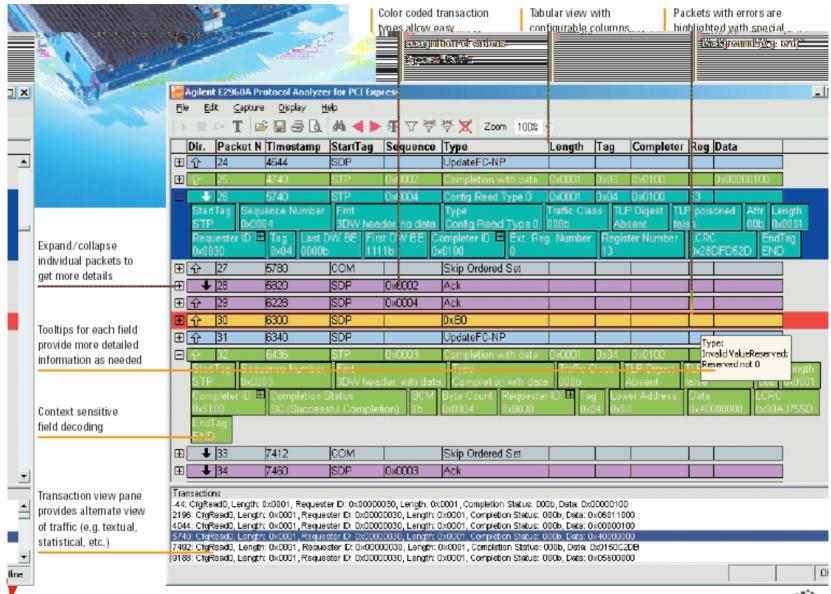

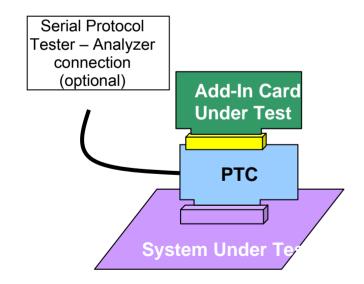

#### Serial Protocol Tester and Protocol Test Card

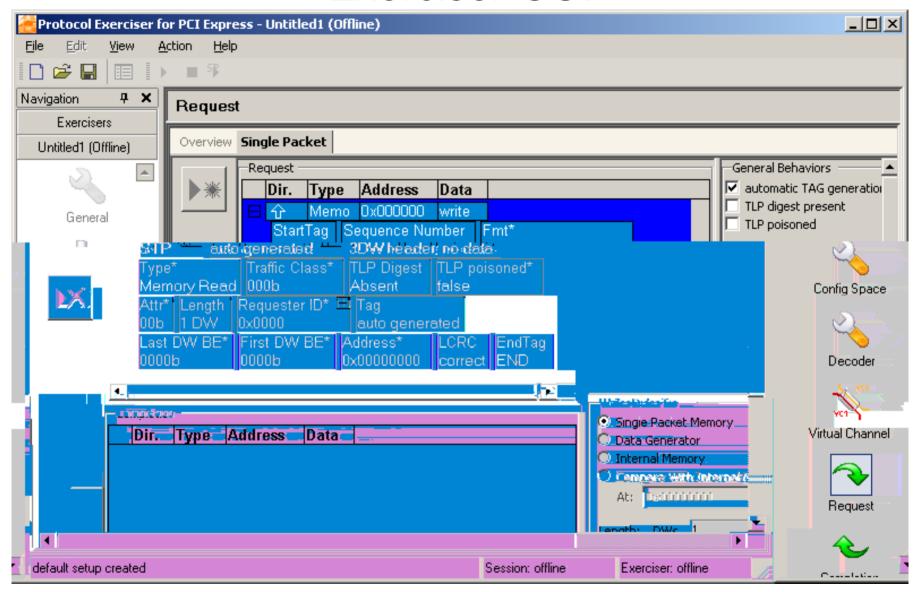

### **GUI Protocol Analyzer**

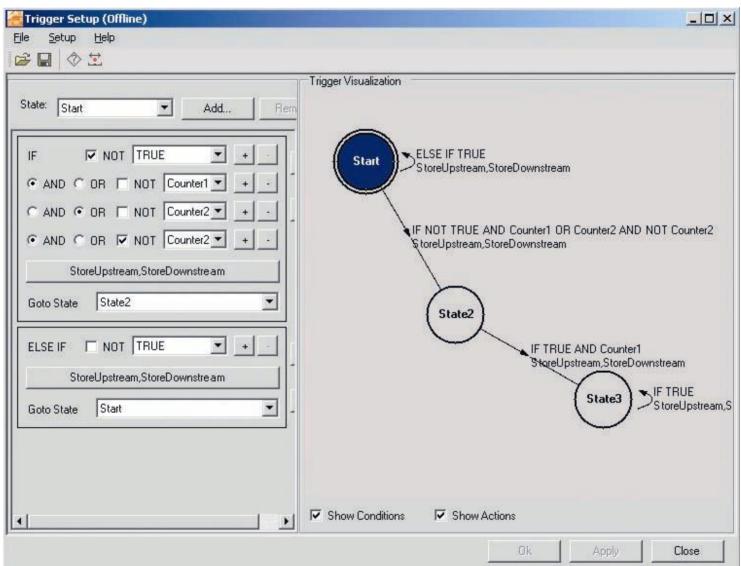

### Protocol Analyzer Trigger Setup

#### **Exerciser GUI**

# Protocol Test Card for PCI Express Compliance Testing

Collaboration and joint development with Intel

- Cost-effective compliance solution

- Easy-to-use

- GUI/push-button solution

- Pre-programmed tests

No programming effort

- Pass/Failed report

- Improves design quality, compliance and accelerates time to market

# PTC GUI - main view

| <b>X</b> -₩ Aç | gilent E2969               | A Protocol Test Car | d for PCI Express - Compliance Test Suite                                                    |  |  |  |  |  |  |

|----------------|----------------------------|---------------------|----------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| <u>F</u> ile   | <u>V</u> iew <u>T</u> ests | s <u>H</u> elp      |                                                                                              |  |  |  |  |  |  |

|                |                            |                     |                                                                                              |  |  |  |  |  |  |

| Execut         | te Status                  | Name                | Description                                                                                  |  |  |  |  |  |  |

| <b>F</b>       | PASSED                     | DLL.5.3#2           | Discard TLP on bad LCRC, send NAK                                                            |  |  |  |  |  |  |

| П              | n/a                        | DLL.5.2#15          | If a normal TLP (one with END framing symbol) is                                             |  |  |  |  |  |  |

| П              | n/a                        | DLL.5.3#3.1         | received and its LCRC doesn't match calculated CRC, discard the TLP, free any storage        |  |  |  |  |  |  |

|                | n/a                        | DLL.5.2#2           | associated with it, schedule a NAK DLLP for transmission if one is not already scheduled and |  |  |  |  |  |  |

| П              | n/a                        | DLL.5.3#3.2         | report an error associated with the Port.                                                    |  |  |  |  |  |  |

|                | n/a                        | DLL.5.2#1           | Retransmit TLP on NAK                                                                        |  |  |  |  |  |  |

|                | n/a                        | DLL.5.2#1.2         | Retransmit TLP until REPLAY_NUM overflow                                                     |  |  |  |  |  |  |

|                | n/a                        | DLL.5.2#10          | Ensure correct TLP order in replay                                                           |  |  |  |  |  |  |

|                | n/a                        | DLL.5.2#1.2         | Start REPLAY upon REPLAY_TIMER expiring                                                      |  |  |  |  |  |  |

|                | n/a                        | DLL.4.1#2           | All reserved fields must be 0                                                                |  |  |  |  |  |  |

|                | n/a                        | DLL.5.2#16          | DLLP with undefined encoding shall be dropped                                                |  |  |  |  |  |  |

|                | n/o                        | DIT 5 2417          | Danast away an uwang agguanga ny in ACV                                                      |  |  |  |  |  |  |

# Fully Buffered DIMM Overview

**PHY and Logic Probing Overview**

Rohit Bhasin

Senior Technical Sales Engineer

Digital Verification and Design Validation Solutions

Agilent Technologies

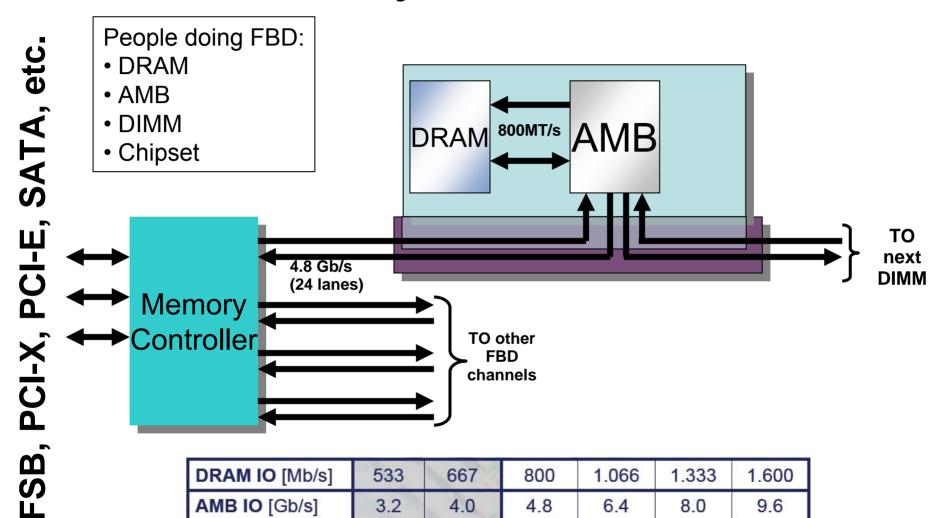

# What is Fully Buffered DIMM?

# **Routing Comparison**

#### Direct DDR2 Registered DIMMs:

1 Channel, 2 Routing Layers with 3rd layer

required for power

Serpentine routing is complicated and uses up a lot of board area

Fewer signals and no trace length matching minimizes board are

#### FB-DIMMs:

2 Channels, 2 Routing Layers (includes power delivery)

FB-DIMM: Fewer Layers, Less Routing Area Dayele

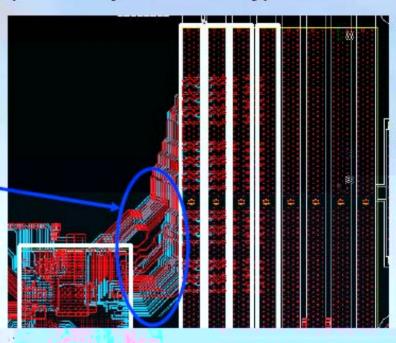

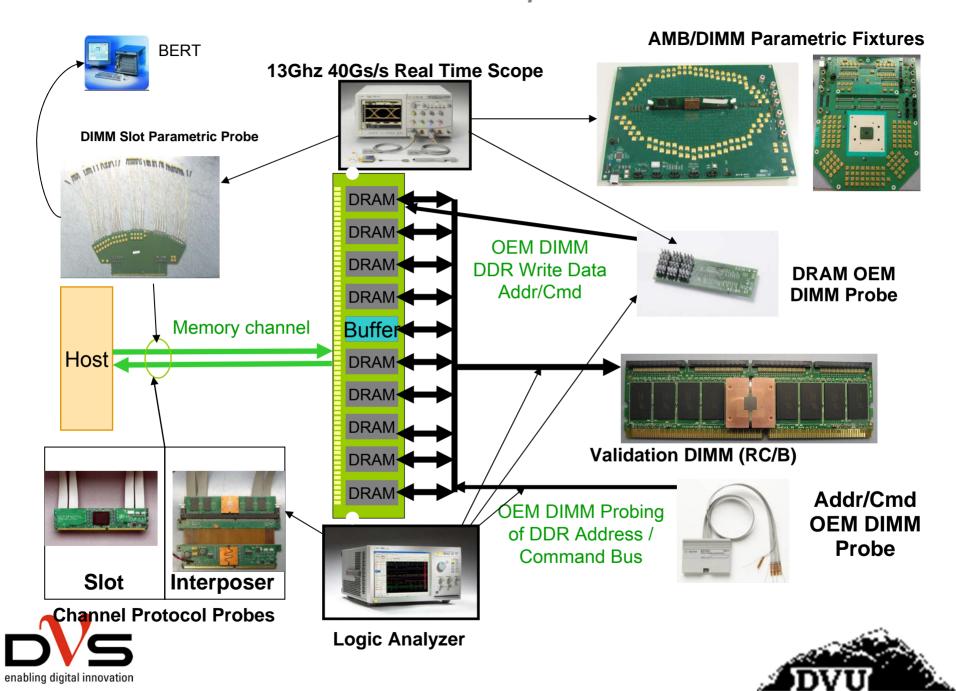

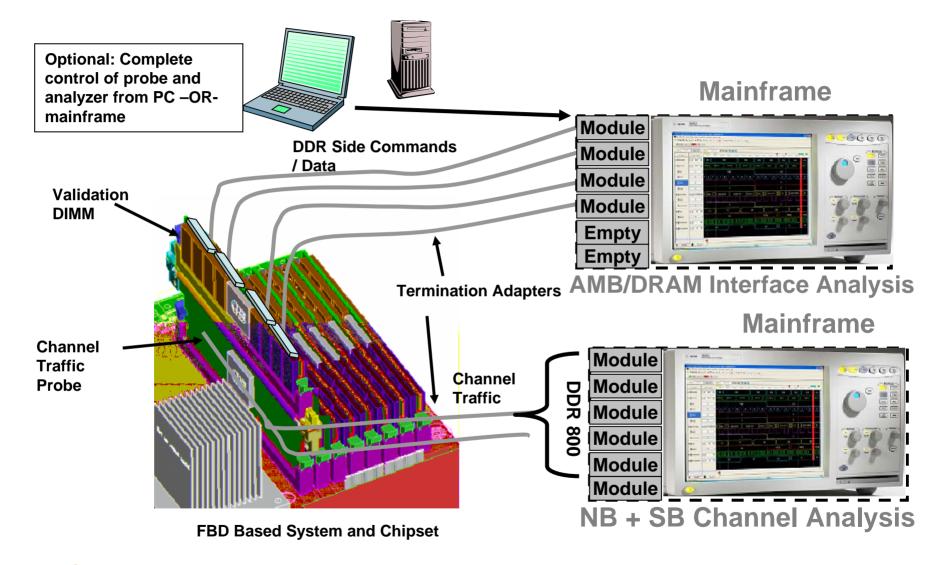

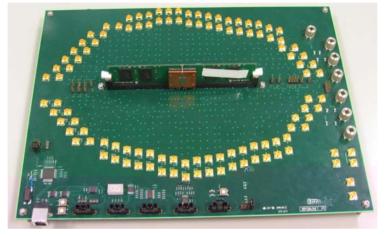

#### FBD Measurement Points and Validation Components

### High Speed Channel Probes

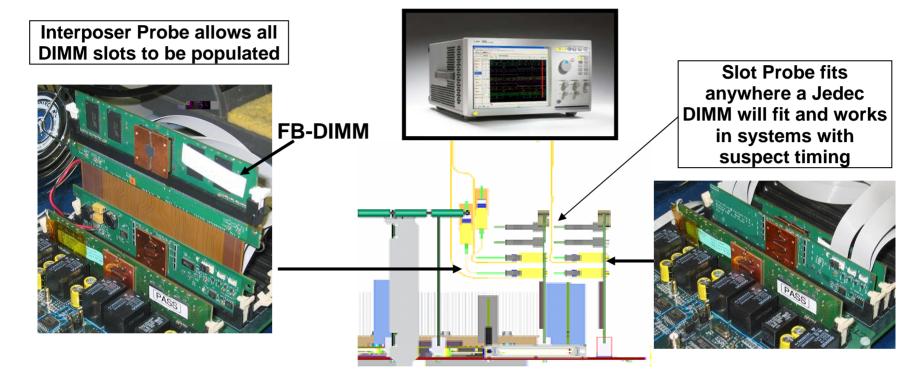

#### **Interposer Channel Probe**

- Does not consume a slot

- Adjustable orientation of interposed DIMM for maximum installation flexibility

- Supports probing of 2 channels in adjacent slots

- Full SB/NB protocol analysis

#### Slot Channel Probe

- Same size as standard FB DIMM to fit in crowded systems

- High Speed channel layout identical to standard DIMM for operation in marginal systems

- Full SB/NB protocol analysis

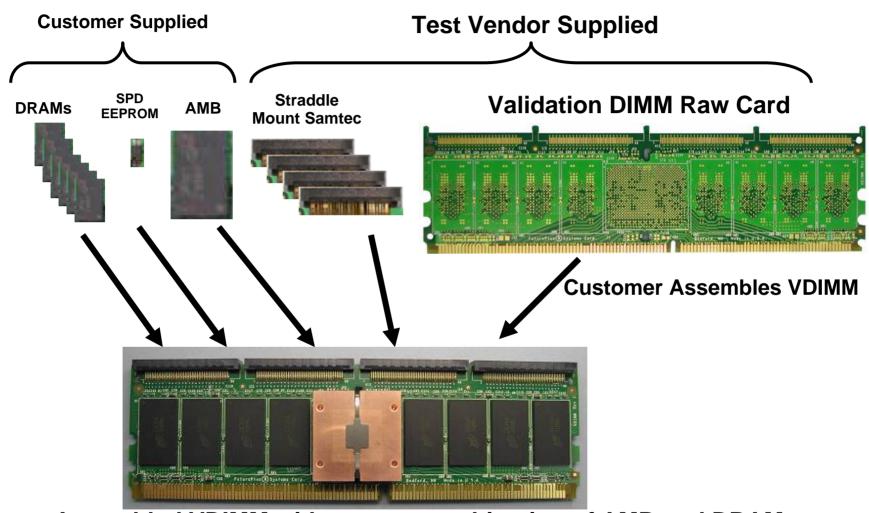

### Complete Pre-AMB Probing

#### **Logic Analyzer Probing for Instrumented DIMMs**

- RC/B Validation DIMM

- Fast connection to all post-register signals (Addr/Cmd/DQ)

- Support to DDR800+ Speeds

- Supports all Jedec AMBs and x8 DRAMS

- RC/A,C,D,G,H,I support planned if demand warrants

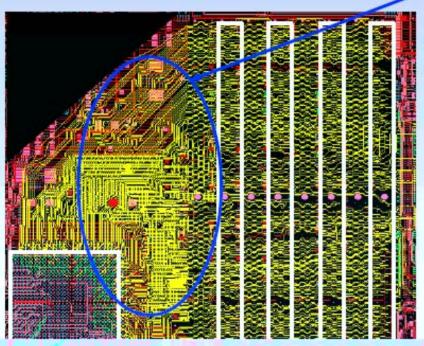

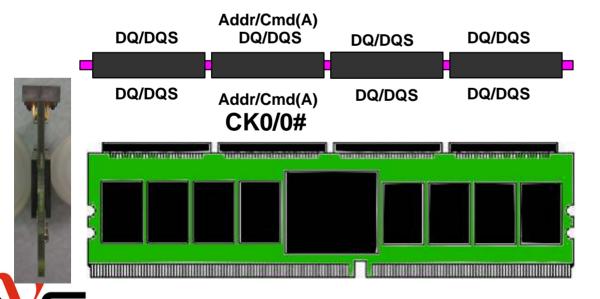

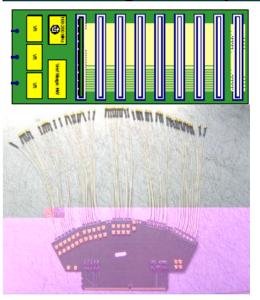

# Validation DIMM (Pre-AMB)

- Functional and signal integrity validation of addr/cmd and data

- Adds 2 layers to DIMM reference design for embedded probing resistors to eliminate stub loading from for routing to logic analysis connectors.

- Validation DIMM for each raw card type

- Straddle mount connector topology minimizes loading and allows probing of adjacent slots and system with limited vertical clearance.

- Supports all DDR2 DRAMs and AMB components

enabling digital innovation

| Signals  | Count |

|----------|-------|

| CK0/CK0# | 1     |

| Addr/Cmd | 28    |

| DQ       | 72    |

| DQS      | 18    |

| DQS#     | 17    |

| TOTAL    | 136   |

# VDIMM Configuration (Pre-AMB)

#### Looking at Channel & AMB/DRAM traffic concurrently

# Complete Post-AMB Probing

#### **Logic Analyzer Probing for OEM DIMMS**

- RPACK Probe

- Probing of FBD Addr/Cmd Bus to DDR1067

- Supports all FBD Raw Cards

- Supports DDR1/DDR2 DIMM and SODIMM

- DDR2 Probe

- Probes DDR2 BGA packages

- DQ/DQS/CK for x4 and x8

DDR2 DRAMs

- Supports all FBD Raw Cards

- Supports DIMM, SODIMM and embedded DDR2

- Scope probing may be possible

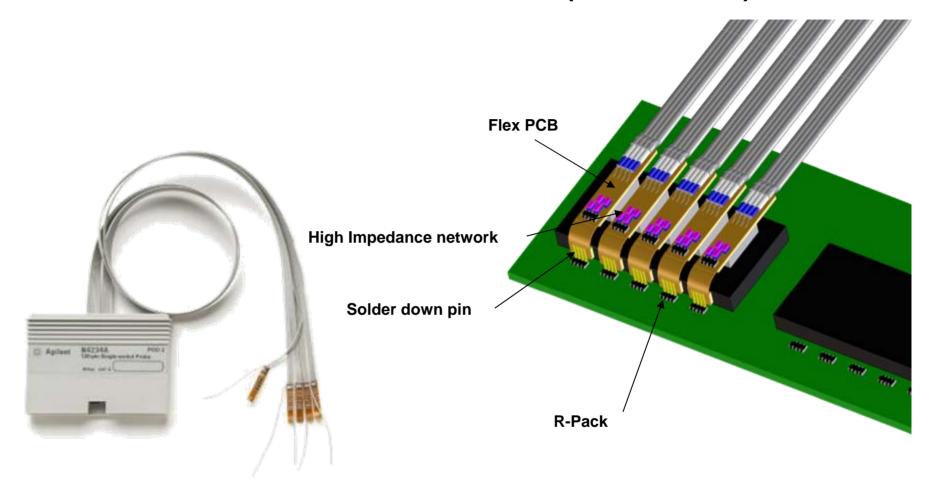

# OEM DIMM Probe (RPACK)

# **OEM DIMM Probe (DRAM)**

- 0.8mm micro-BGA probe of DQ/DQS using flying lead probes

- Embedded tip resistors isolate probe from bus

- Functional and signal integrity validation (EyeScan/scope)

- Supports DDR2 common footprint (x4/x8)

## Complete Pre and Post-AMB Probing

#### Logic Analyzer Probing for Instrumented and OEM DIMMS

#### RC/B Validation DIMM

- RC/B based most commonly used DIMM

- Uses actual RC/B layout for accurate results

- Compact design minimizes loading

- Straddle mount analyzer connections for zero increase in DIMM thickness

- Right angle probes fits in tight server systems

#### **RPACK Probe**

- Probing of FBD Addr/Cmd Bus to

DDR1067

- Supports all FBD Raw Cards

- Supports DDR1/DDR2 DIMM and

SODIMM

#### DDR2 Probe

- Probes DDR2 BGA packages

- DQ/DQS/CK for x4 and x8 DDR2 DRAMs

- Supports all FBD Raw Cards

- Supports DIMM, SODIMM and embedded DDR2

- Analog scope connection with high bandwidth probes

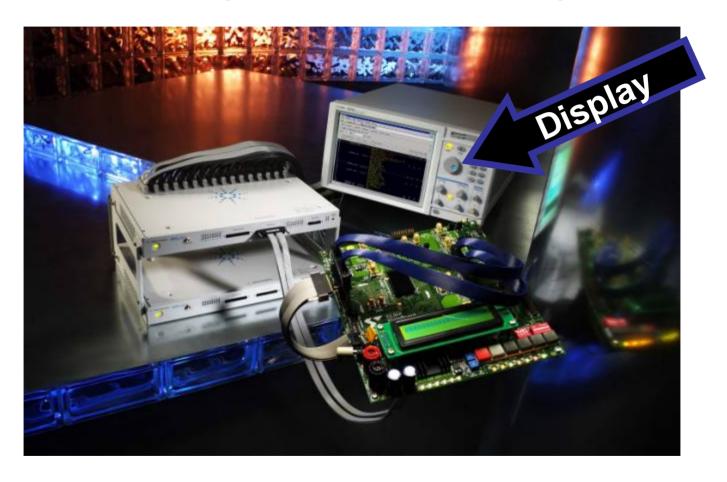

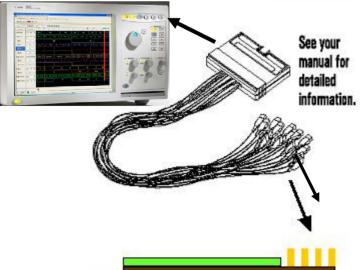

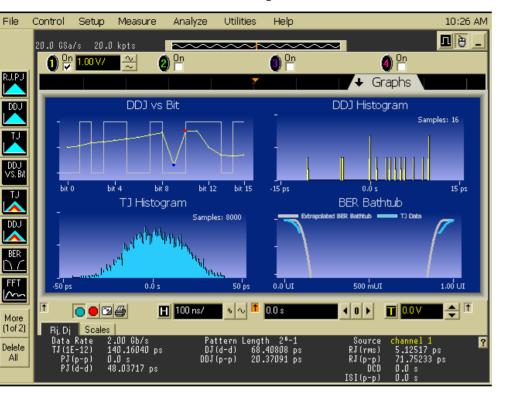

## FBD Requires Bandwidth

Recommended - 13 Ghz Real Time Scope with very high bandwidth probes or FBD parametric fixtures provide bandwidth required for 4.8Gb FBD measurements

### Comprehensive Data Analysis

- Complete Jitter Analysis

- RJ/DJ (ISI,DCD, Periodic jitter) separation

- Jitter histograms

- Spectral analysis

- Traceable to individual bits

- Bathtub BER analysis

- FBD Mask and Compliance Test

- Real Time Eye

- Eye unfolding identifies failure pattern

- Fixture control and compliance test suite integration

# Graduated Physical Layer Parametric Test

**AMB Parametric Test**

- AMB Die and Package focus

- Jedec Tx/Rx, BERT, Return Loss, etc.

- Package modeling

**DIMM Parametric Test**

- Adds DIMM and connector to test environment

- DIMM and connector impact on Channel specification

- Supports all Raw Cards

- Simplifies failure analysis

Characterized with

S-parameters for

de-embedding fixture impact

N4238A Slot Parametric Probe

- Adds MB and second connector to test environment

- System channel SI performance

- Supports any FBD channel

- Simplifies failure analysis

CTC test scripts work across all fixtures

## Anyone awake?

Summary and take aways...

- Serial Links ramping up to 5-6Gb (per lane), probably higher

- Parallel signaling ramping up to 9.6Gb (e.g. FBD)

- Equipment out there to help you design any interface you want! Scope, LA's can also be used as a general purpose debug tool (for proprietary interfaces)

- Probing is KEY (both at PHY and logic/protocol layers, don't think you can use a conventional probe to look at multi-gigabit signaling

- Use the automated tools that are available to help you validate your interfaces (i.e. Automated mask testing on scope, predefined DDR IA's, etc)