Minimizing EMI & Noise Coupling Among Circuit Regions In Circuit Boards

Valuable concepts that PCB Designers can use immediately for "partitioning" in layout topologies

W. MICHAEL KING Systems Design Advisor

www.SystemsEMC.com

# The "Process" has a name: PARTITIONING

#### $\leftarrow \text{OR} \rightarrow$

"How to have 'lively & opinionated' discussions with *everyone* in the company about *'what goes where'* on a circuit board!"

# **Examples: Purposes of Partitioning**

- → Separation of High-Amplitude from Low-Amplitude (e.g. "sensitive" signals or circuit regions) for optimal functionality

- → Containment of specifically unique Spectral Regions

- → Protection of analogue circuits from digital spectra intrusion (S/N Ratios)

- $\rightarrow$  Exclusion of EMI Emission from interface interconnecting cables

- → Rejection of extraneously applied fields or currents (susceptibility-immunity factors) from functional intrusion

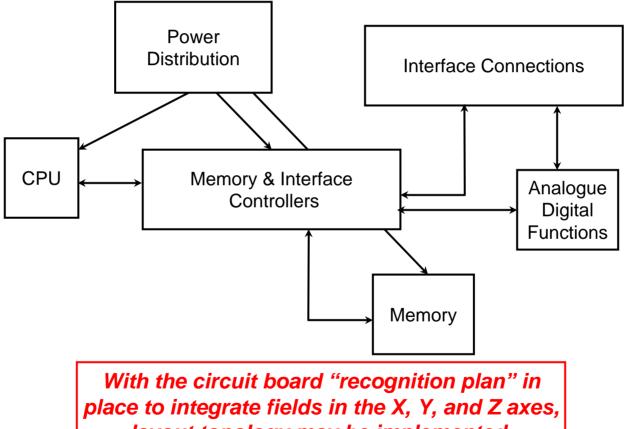

# Partitioning Initially Requires A Recognition Plan

- → Recognition plan is a subset part of the system-product "Common-mode Architecture"

- → "Common-mode Architecture" is a derivative of the systemproduct electrical / functional block architecture

- → System-product functionality is identified initially in "block" structures

- → "Block" structures set the pattern approach initially for X-Y Axes topology, followed by Z-Axis implementations.

- → Inspection: What are the "threat" SOURCES and HOW will they couple to VICTIM "receivers"?

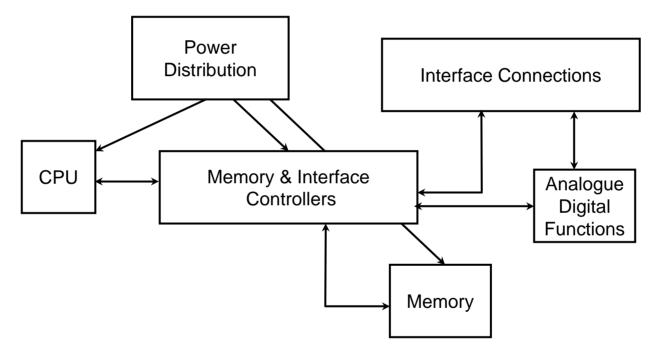

# Electrical "Block" Architecture Initiates The "Evaluation" Process →

# Is this enough?

Task: Identification of "Threat Sources" and "Victim Receivers" GOAL: EMC (Self-compatibility)

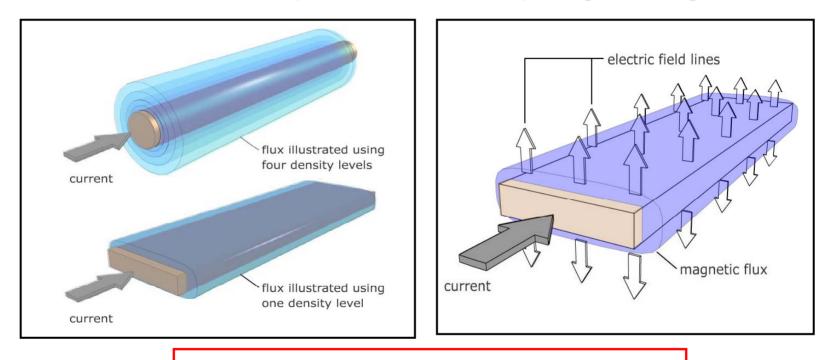

#### Typical Prevalent Recognitions Might be Limited to Flux and Capacitance Coupling of Signals

#### What About Peak Transition Current Cross-Conduction POWER Surges?

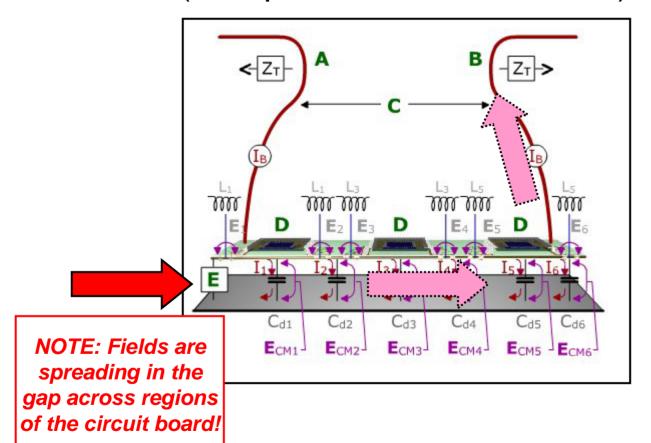

Inspection of "Threat" Sources: Recognition of Predominant Common-mode Losses & Potentials in the X & Y Axes

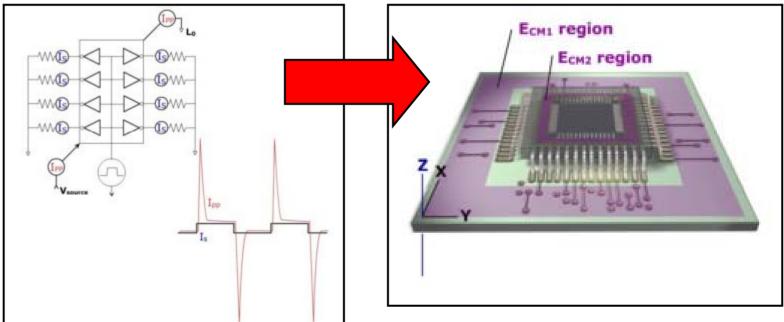

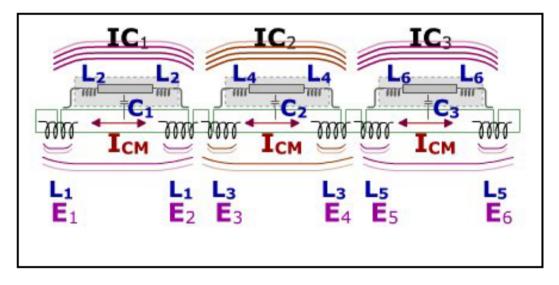

Peak-Current Cross-Conduction Surges With Circuit Devices...... .....Excites Common-mode Fields and Loss Potentials From Patterned Layout Inductance Surrounding Devices

# Patterned Layout Inductance: A "Phased Array" Effect\_\_\_\_

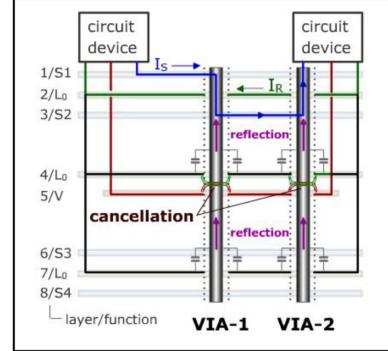

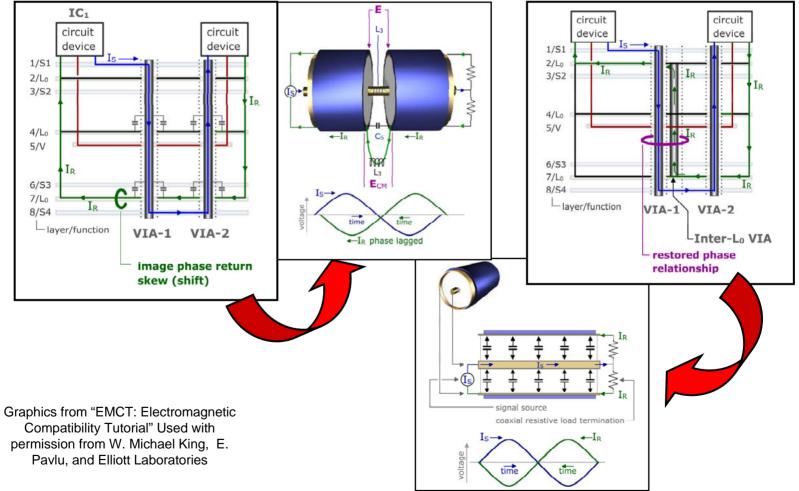

#### Peak-Current Cross-Conduction With Circuit Devices → Surges Across "Via" Apertures (at each rise and fall time).

#### The "Patterned Layout Inductance" - Formation Sequence -IRF TEM Есмс Есм Есмв Есма IRF IRF .....but as Apertures **RF** Common-mode (escapes) are added, the Current in a contiguous cumulative losses plane has comparatively progressively increase. low loss..... Blind Vias will dramatically **KEY DESIGN CONSIDERATION:** reduce "patterned layout" WEB TO APERTURE SIZE RATIO - VIA HOLE DENSITY! inductance!

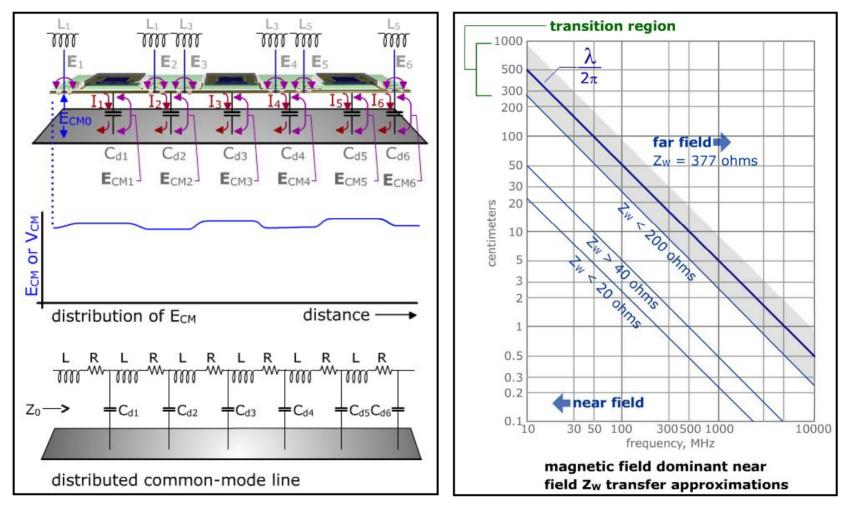

Distributed Common-mode Sequence

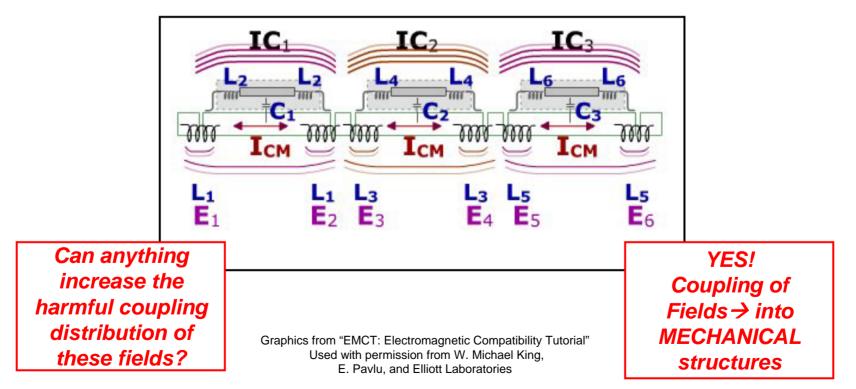

Examination of "Common-Mode Fields" From Excitation Of Patterned Layout Inductance Across 3 Axes

### What Happens When HEAT Sinks Are Added?!

#### Increased Fields and Coupling Probabilities Happen.....

.....Unless the CURRENTS CAUSING the FIELDS are CAPTURED back to IMAGE Return Planes

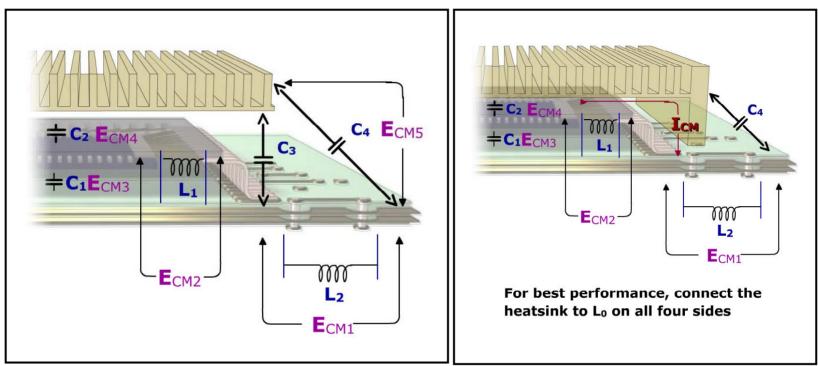

# Common-Mode Coupling (Transfer Impedance) Across Partitions: HEAT SINKS!

RF Common-mode current results in EM fields that couple to, then across, heat sinks in LOW RF Transfer Impedances.....

.....for which the solution is to "terminate" both the "source" and "victim" heat sinks to the L0 Planes

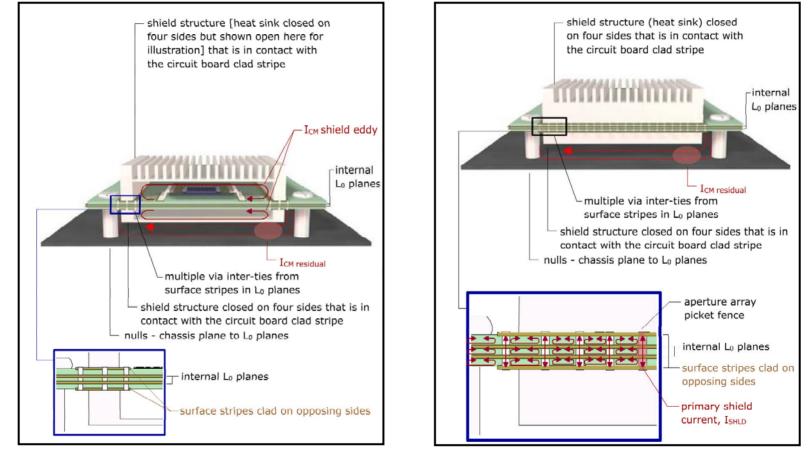

# Termination of Heat Sinks Can Significantly Localize Even Multi-GHz Fields

## Termination of Heat Sinks Can Provide Significant Regional Partitioning Performance Values (>50dB)

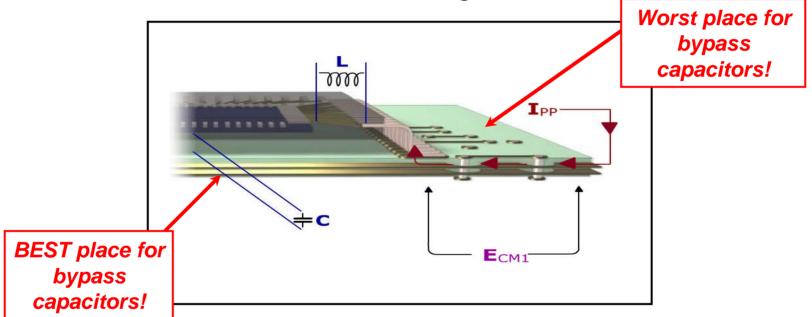

#### Process: A Quick Litany Regarding Ohm's Law

- Q: Where does current return? A: To the source.

- Q: Through what path?

A: The lowest impedance path.

Q: In an A.C. "dynamic system", where is the lowest impedance path?

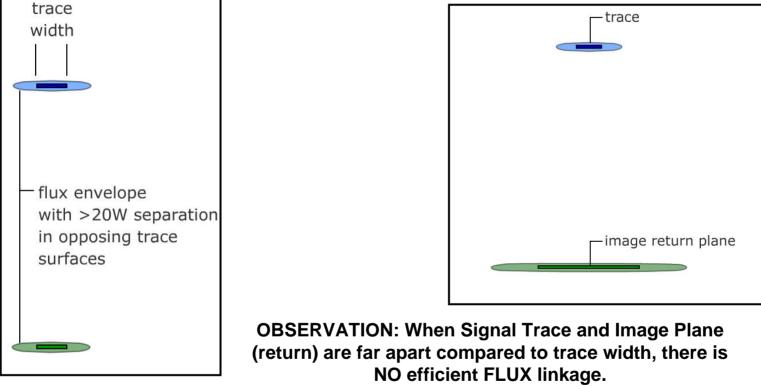

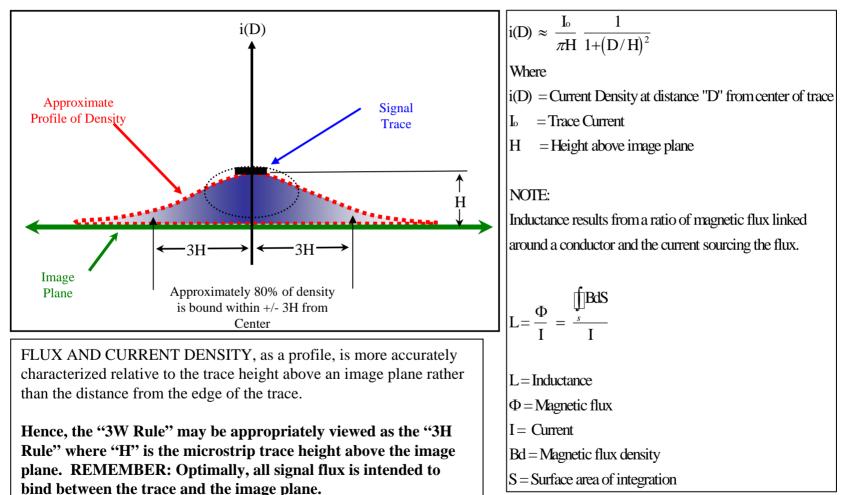

A: Where the source flux phase and image counter-phase link to cancel inductance!

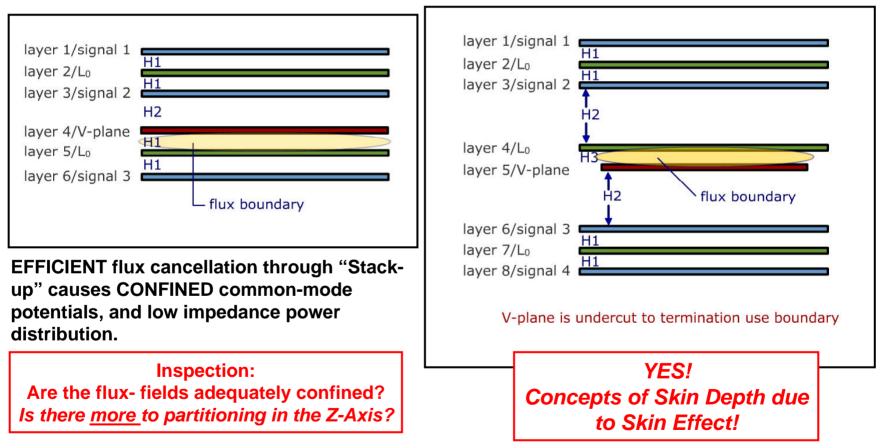

# Inspection of "Threat" Sources: Recognition of Z-Axis $\rightarrow$ Within Circuit Board

**Z-Axis Signal Routing**

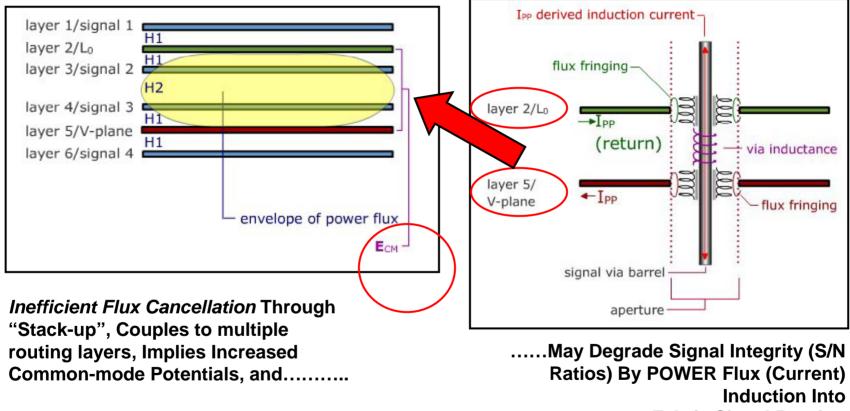

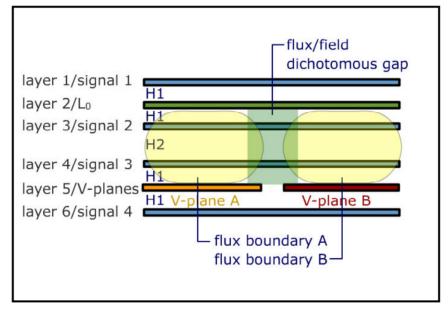

# Inspection of "Threat" Sources: Recognition of Z-Axis Field Intrusions →Within Circuit Board

Split V-planes absent defined power images will intrude power coupling into 3 of 4 signal routing layers, and provide no uniform imaging. This will also highly distort signal quality in two routing layers.

# Inspection FLUX Formations as Z-Axis Fields Within Circuit Board

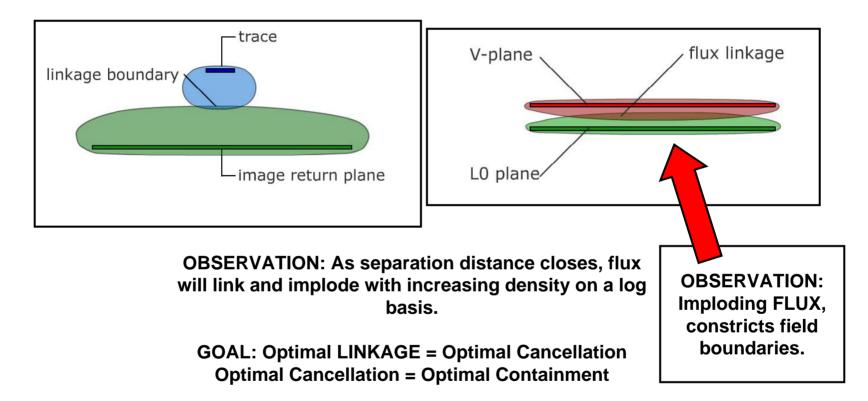

Without LINKAGE there can be no CANCELLATION of inductance

## Inspection of FLUX Formations as Z-Axis Fields Within Circuit Board

# Inspection of FLUX LINKAGE Distribution as Z-Axis Fields Within Circuit Board

# Inspection of EFFICIENT FLUX CANCELLATION in the Z-Axis Fields Within Circuit Boards

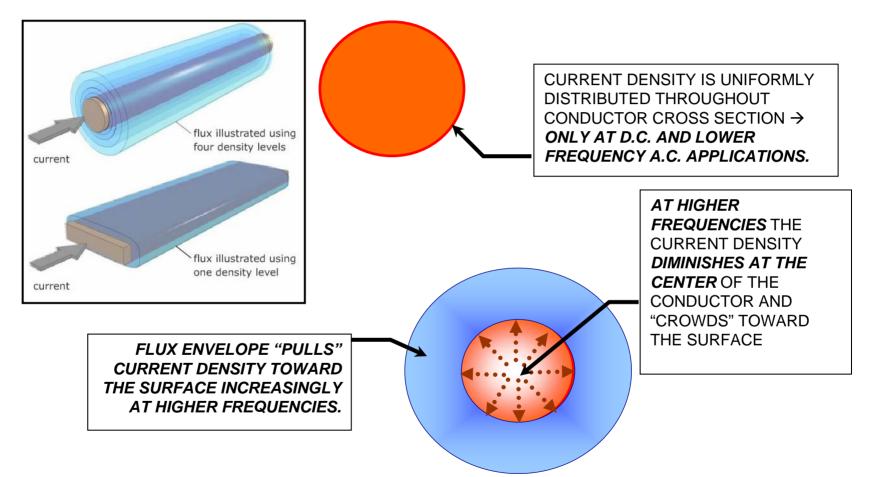

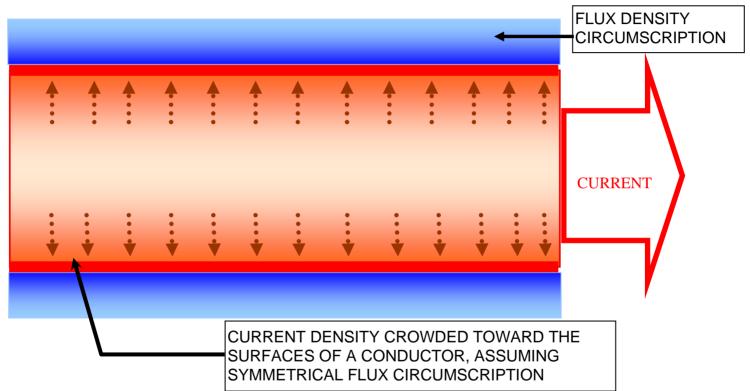

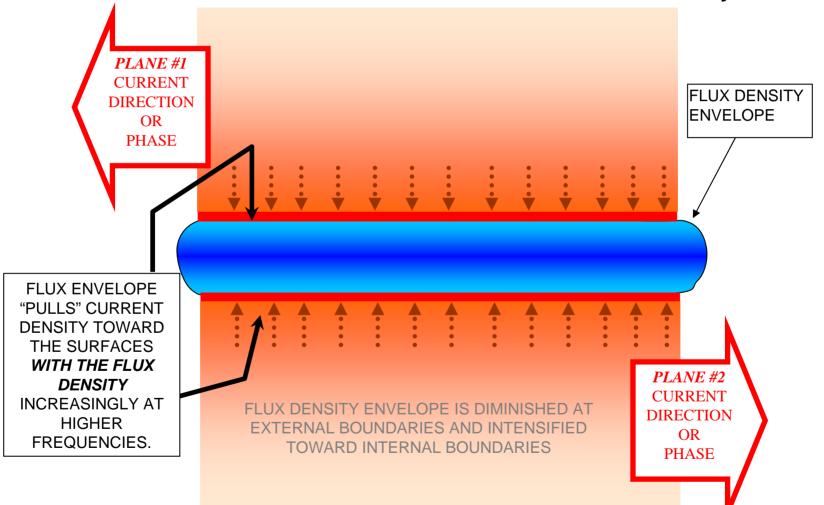

## SKIN EFFECT – SKIN DEPTH Within Conductors: Current Density Distribution

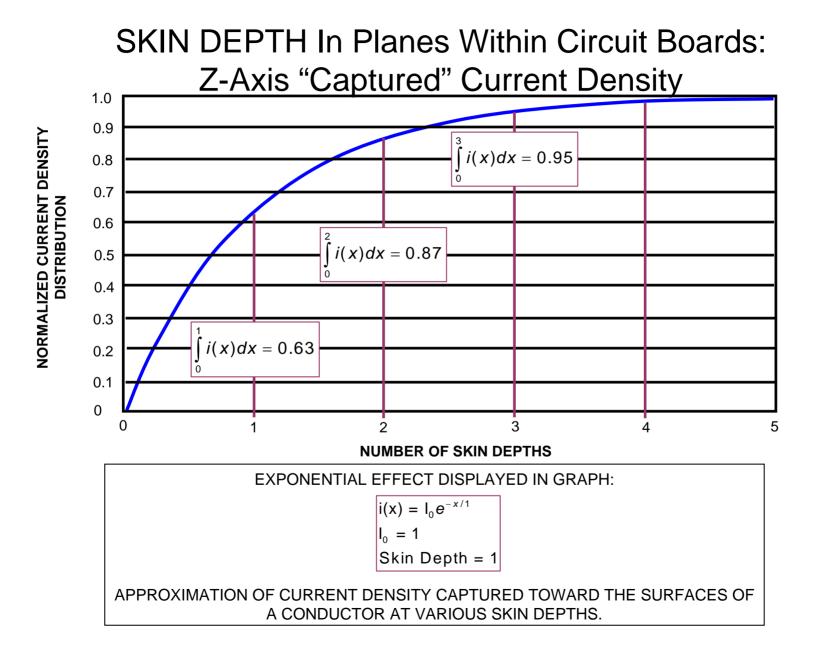

### SKIN EFFECT – SKIN DEPTH In Planes Within Circuit Boards: Z-Axis Current Density

To emphasize the formation of skin effect, the *higher* the frequency, the *smaller* the skin depth – and - the *more conductive* and/or the *more permeable* the material (at higher frequency), the *smaller* the skin depth. Given that observation in terms of skin effect, the smallest skin depths occur with most conductive materials with higher permeability (assuming that the permeability is evident as a characteristic of the material at high frequency) and at the highest frequencies.

#### SKIN EFFECT – SKIN DEPTH In Planes Within Circuit Boards: Z-Axis Current Density

## Frequency Relationship of SKIN DEPTH In Planes Within Circuit Boards: Z-Axis "Captured" Current Density

| Frequency<br>MHz | Skin Depth<br>Mils (inch) | 5 Depths<br>Mils (inch) |

|------------------|---------------------------|-------------------------|

| 1                | 3                         | 15                      |

| 10               | 0.8                       | 4                       |

| 100              | 0.26                      | 1.3                     |

| 1000             | 0.08                      | 0.4                     |

EXAMPLES OF SKIN DEPTHS FOR ANNEALED COPPER AT SPECIFIC FREQUENCIES.

| Skin<br>Depths | Percent<br>Capture* |

|----------------|---------------------|

| 1              | 63                  |

| 2              | 87                  |

| 3              | 95                  |

| 4              | 97                  |

| 5              | 99                  |

APPROXIMATION OF CURRENT DENSITY CAPTURED TOWARD THE SURFACES OF A CONDUCTOR AT VARIOUS SKIN DEPTHS.

### Skin Depth VALUE Calculation

The value of skin depth is yielded by

$\delta = \sqrt{\frac{2}{\mu_r \sigma_r \omega}}$  (in meters since the values of  $\mu_r$  and  $\sigma_r$  are expressed with relationship to meters)

where,  $\omega = 2\pi f$  where f is in Hertz

For reference, the conductivity of annealed copper is given as the symbol  $\sigma$ , where

$\sigma = 5.82 \text{ x} 10^7 \text{ mhos/meter for copper}$

with the relative values for other metals assigned the symbol  $\sigma_r$  .

$\sigma_r$  is a numerical value that results by applying the factor indicated by that designated for  $\sigma_r$  to the value of the reference,

The permeability of free space is given the symbol  $\mu$ , where

$\mu = 4\pi \ge 10^{-7}$  Henrys/meter for free space

with the relative values of other materials assigned the symbol  $\,\mu_r$  .

$\mu_r$  is a numerical value that results by applying the factor indicated by that designated for  $\mu_r$  to the value of the reference.

# REVIEW of Current Density and Flux Distribution as Z-Axis Fields Within Circuit Board

# Efficient Flux Cancellation in Z-Axis – Within Circuit Board

- $\rightarrow$  Power Impedance Is Dynamically Reduced.

- → Common-mode Potentials Reduced Proportionately

- $\rightarrow$  Power Flux Cancels in Small Loop Formations.

- $\rightarrow$  Signal Integrity is Defended.

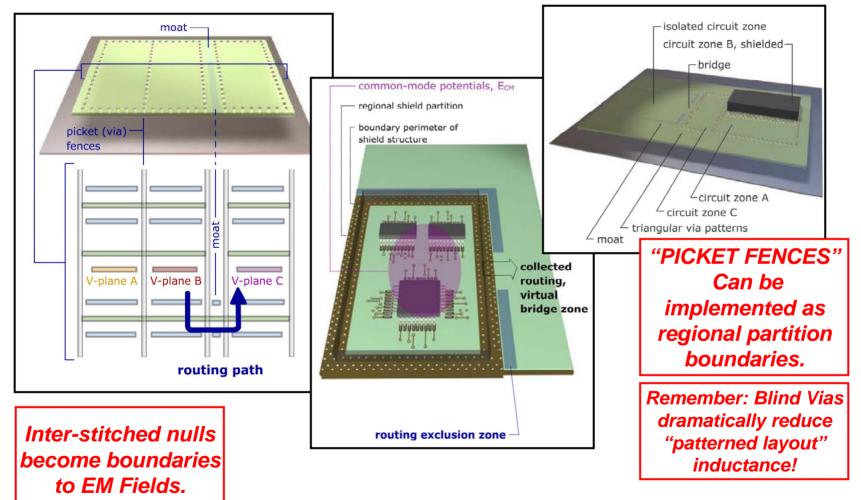

# Inter-Stitched L0 Vias May be Needed To Cause Efficient Flux Cancellation Across the Z-Axis in Circuit Boards

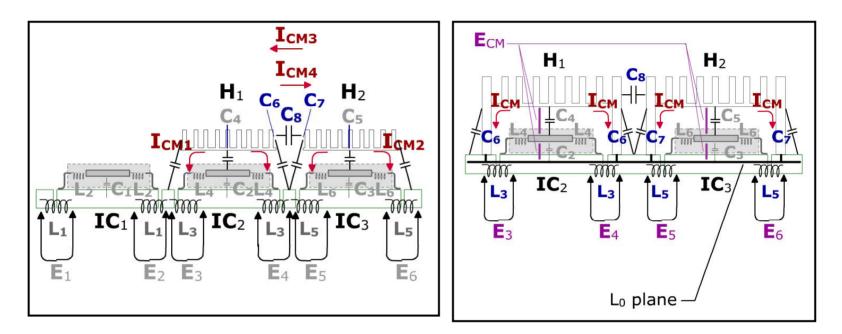

# Review of "Common-Mode Fields" From Excitation Of Patterned Layout Inductance – 3 Axes

After Topology and "Patterned Layout Inductance", Coupling across regions through Heat Sinks, Stack-up and Skin Depth Boundaries,

Are there other considerations?

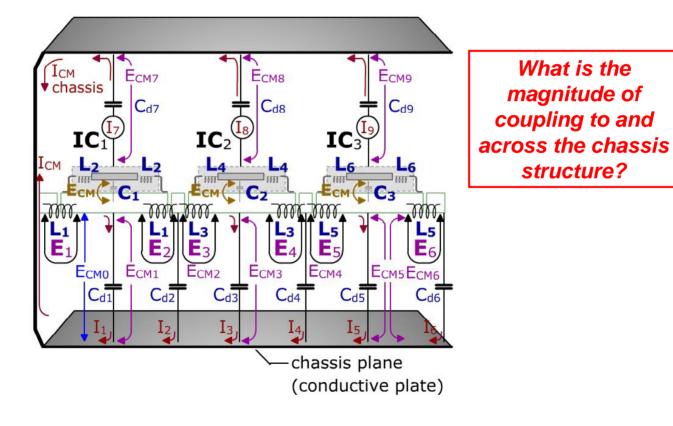

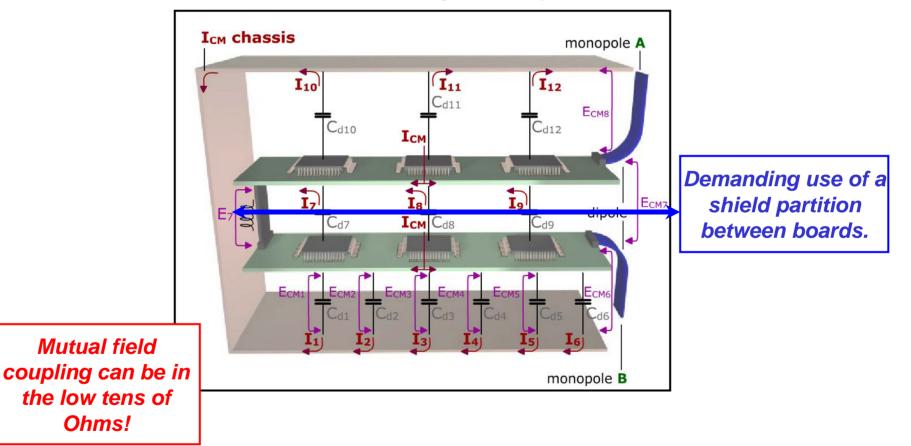

# Coupling Through Field Transfers to Case & Chassis Structures!

## Examination of Common-Mode Field Transfer IMPEDANCES to Conductive Chassis Structures

Implications of Common-Mode Transfers & Excitations in 3 Axes With Cables (Multiple Antenna Structures)

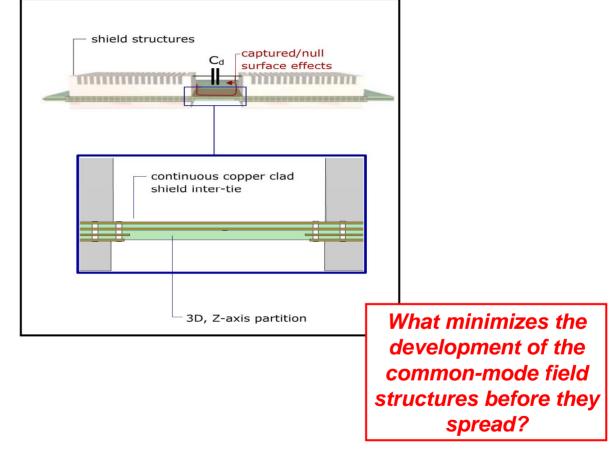

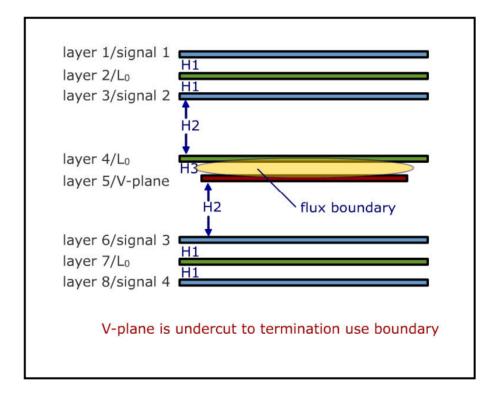

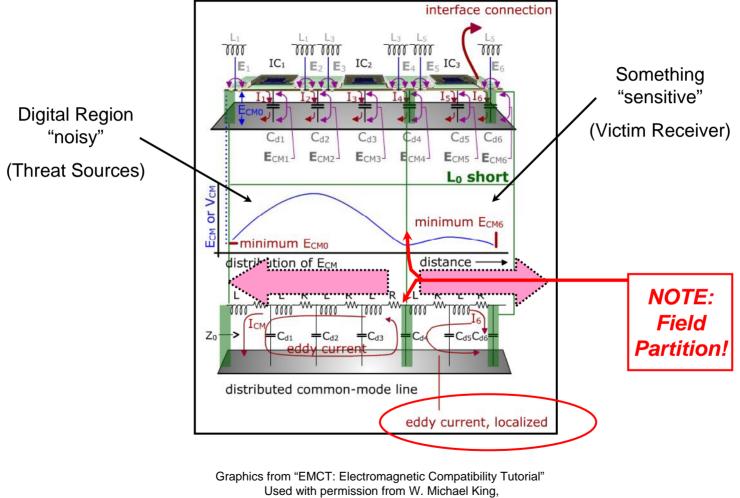

# Partitioning With NULLS In the Z-Axis Can Defend S/N Ratios and EMC

E. Pavlu, and Elliott Laboratories

# Close-Proximity Paralleled Boards Will Mutually Couple!

# What (Else) Can Influence EMI Partitioning in Planes?

#### HINT s

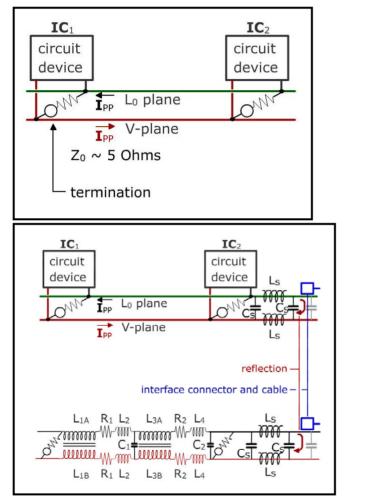

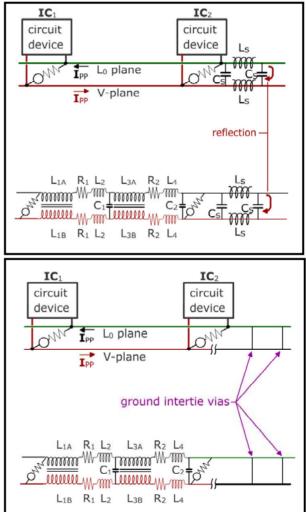

Remember: V-Planes with an image plane are Z-Axis Transmission Lines

Are they appropriately "end-terminated?"

"End-terminated" in planes can mean "edgeterminated!"

What optimally determines the use of "edge termination?"

# Undercut V-planes can Defend S/N Ratios and EMI in Interface Cables

# REVIEW of Electrical "Block" Architecture

layout topology may be implemented.

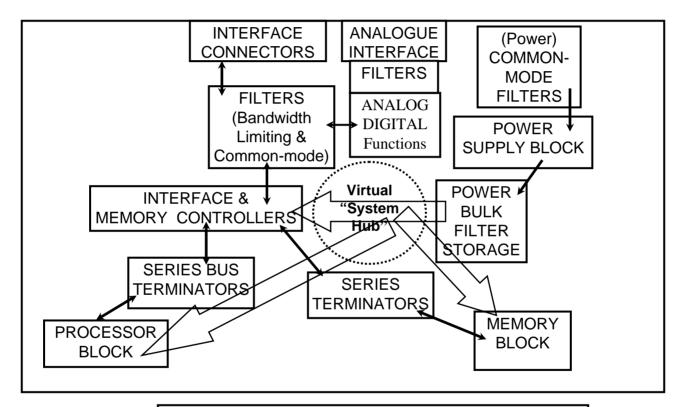

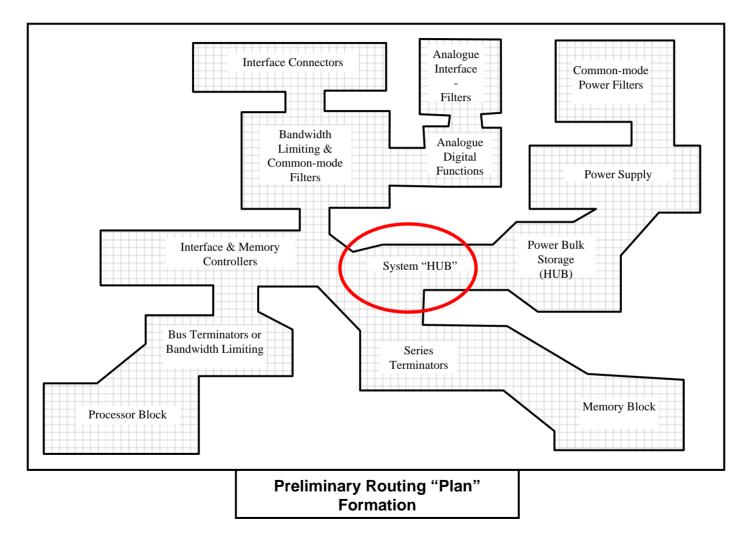

# Implied Common-mode Architecture Derivative of Electrical "Block" Diagram

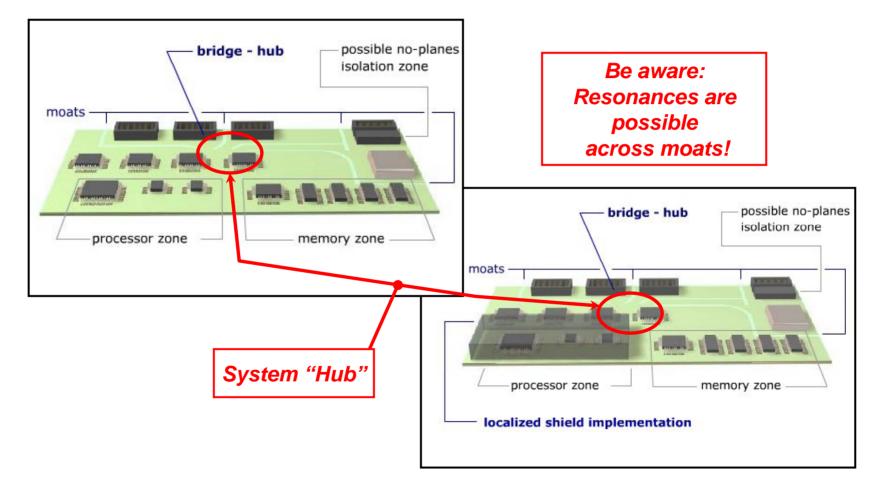

"MAP" of Architectural Topology With Function and HUB, Initially Limited to X-Y Axes

# **Resultant Architectural Routing Plan**

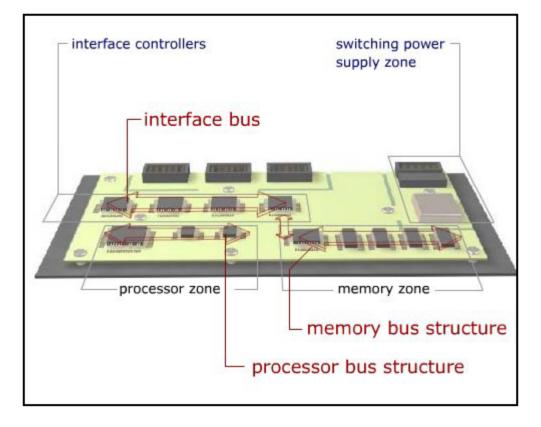

# Implied Topology of Circuit Board With Chassis Plane

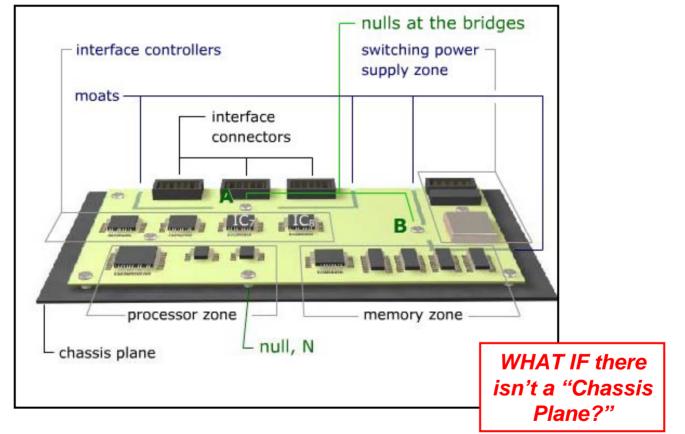

# Implied Topology of Circuit Board With NULLS to Chassis Plane

#### Implied Topology of Circuit Board With Inter-Stitched L0 Vias As Regional *NULL Partition Boundaries*

# Implied Partitioning Topology of Circuit Board Without Chassis Plane

# Original "Recognition Plan" – Modified → Becomes "Summary"

- → **PARTITIONING** recognition plan is a subset part of the system-product "Common-mode Architecture"

- → "Common-mode Architecture" is a derivative of the system-product electrical / functional block architecture

- → System-product functionality is identified initially in "block" structures

- → "Block" structures set the pattern approach initially for X-Y Axes topology, followed by Z-Axis implementations for PARTITIONING CONCEPTS

- → Separation of High-Amplitude from Low-Amplitude (e.g. "sensitive" signals or circuit regions) for optimal functionality is a criteria set for **PARTITIONING**

- → Containment of specifically unique Spectral Regions requires 3-Axes Views

- → Protection of analogue circuits from digital spectra intrusions (S/N Ratios) and Exclusion of EMI Emission from interface – interconnecting cables must include examination of field transfer involvements "through" STRUCTURE & chassis coupling

- → Rejection of extraneously applied fields or currents (susceptibility-immunity factors) from functional intrusion will follow the partitioning concept in proportion to the approach.

#### Author Information:

W. Michael King is a systems design advisor who has been active in the development of over 1,000 system-product designs in a 46 year career. He serves an international client base as an independent design advisor.

Many terms used for PC Board Layout, such as the "3-W Rule", the "V-plane Undercut Rule", and "ground stitching nulls", were all originated by Mr. King. His full biography may be seen through his web site: www.SystemsEMC.com.

Mr. King's published original research changed the state the art on the subjects of the ESD dynamic waveform continuum and responses of cardiac pacemakers to electromagnetic fields. He has authored contributing feature articles to EDN Magazine, Design News Magazine, University of Oxford (England) CPD Newsletter, and Elliott Laboratories Compliance Advisory Service Newsletters as well as other publications.

Significantly, he is the author of *EMCT: High Speed Design Tutorial* (ISBN 0-7381-3340-X) which is the source of some of the graphics used in this presentation. EMCT is available through Elliott Laboratories, co-branded with the IEEE Standards Information Network.

Contact: W. Michael King Phone: 714-545-2519 E/mail: michael@systemsemc.com (or systems-emc.com)