Joshua Friedrich – Senior Technical Staff Member, IBM Server & Technology Group June 6, 2012

# POWER<sup>™</sup> Processor Design & Methodology Directions

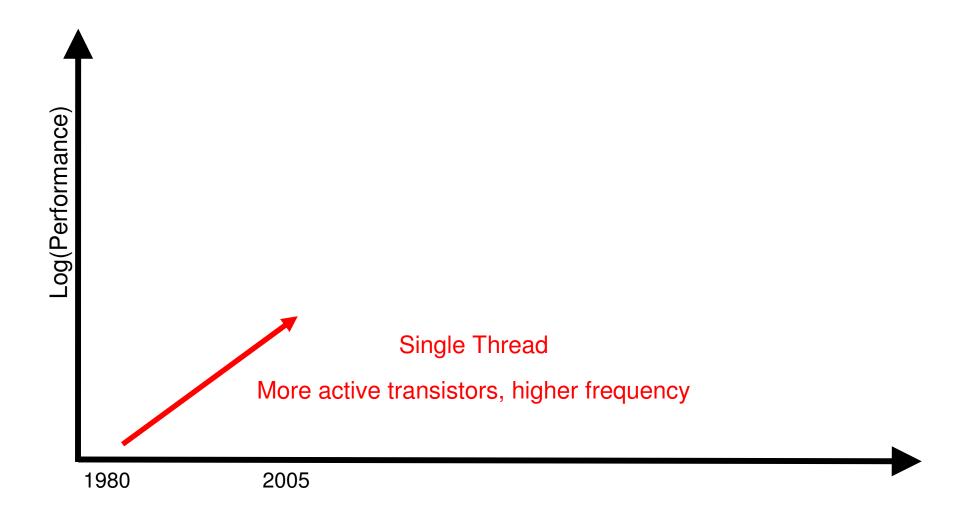

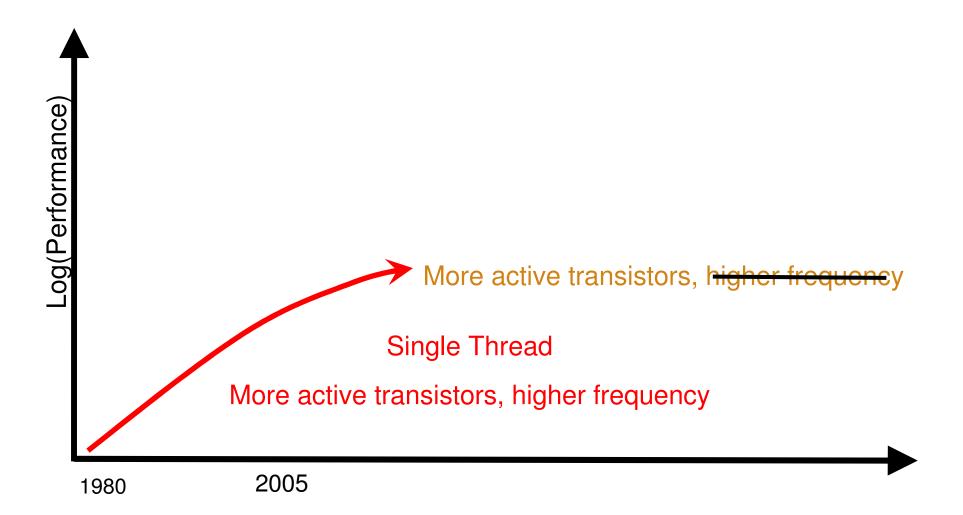

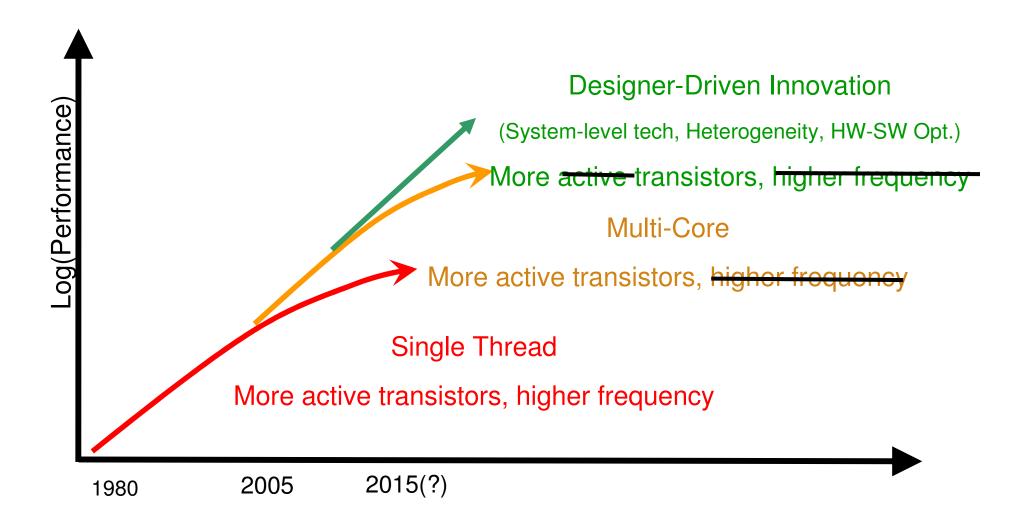

#### CMOS Microprocessor Trends, The First ~25 Years (Good old days)

## **Characteristics of Single Thread Era**

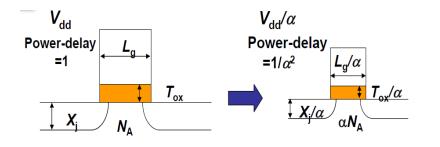

## **Dennard Scaling**

## **Optical Scaling / Node Migration**

## Exponential Frequency Growth

## Expanding uArch Complexity

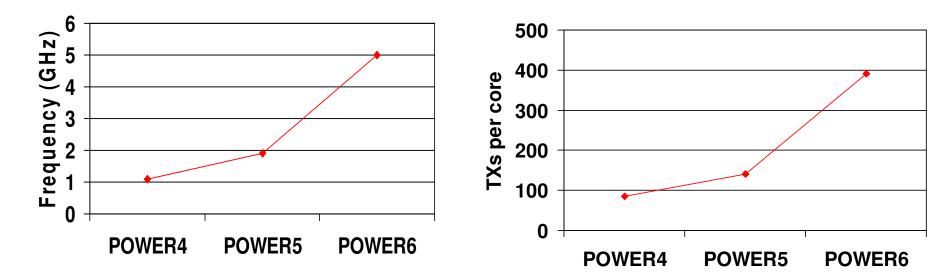

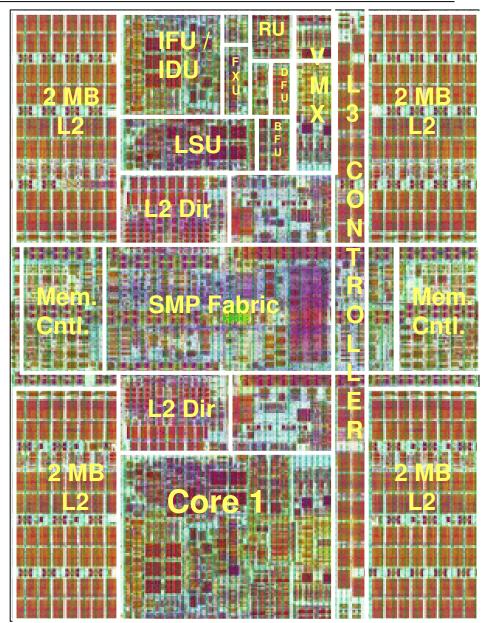

## Single Thread Era Icon: POWER6

- 5+ GHz operation, >790M transistors, 341mm<sup>2</sup> die

- 65nm SOI with 10 levels of Cu interconnect

- 2 superscalar, SMT cores with 7 instruction dispatch & 9 execution units

- 8 MB Level-2 cache + support for 32MB L3

- 2 memory controllers, Two-tier SMP Fabric

- Same pipeline depth & power at 2x frequency versus POWER5

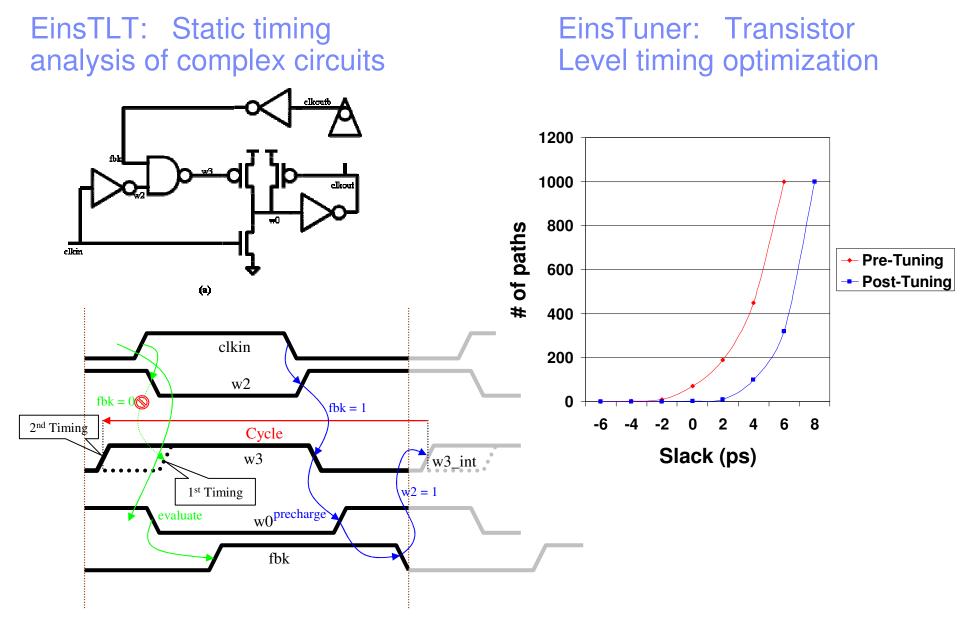

## Single Thread Era EDA: Transistor Analysis & Optimization

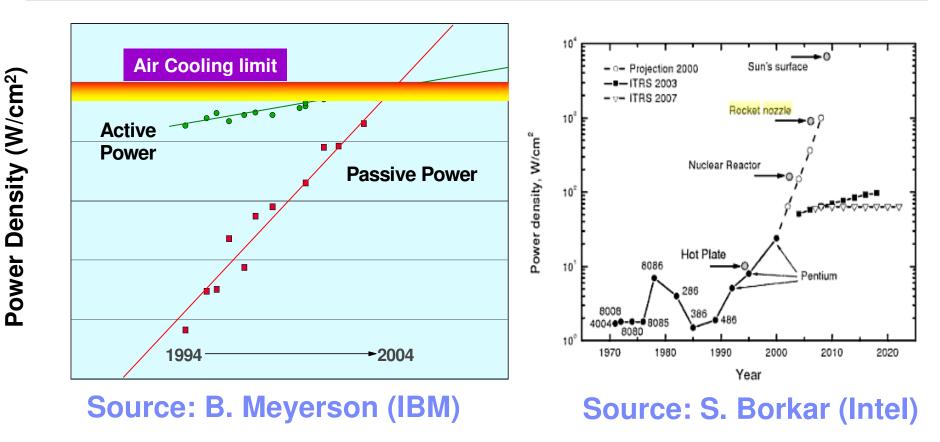

## End of an Era: The Power Wall

Inability to scale Tox & lower voltage resulted in a power wall for single thread performance

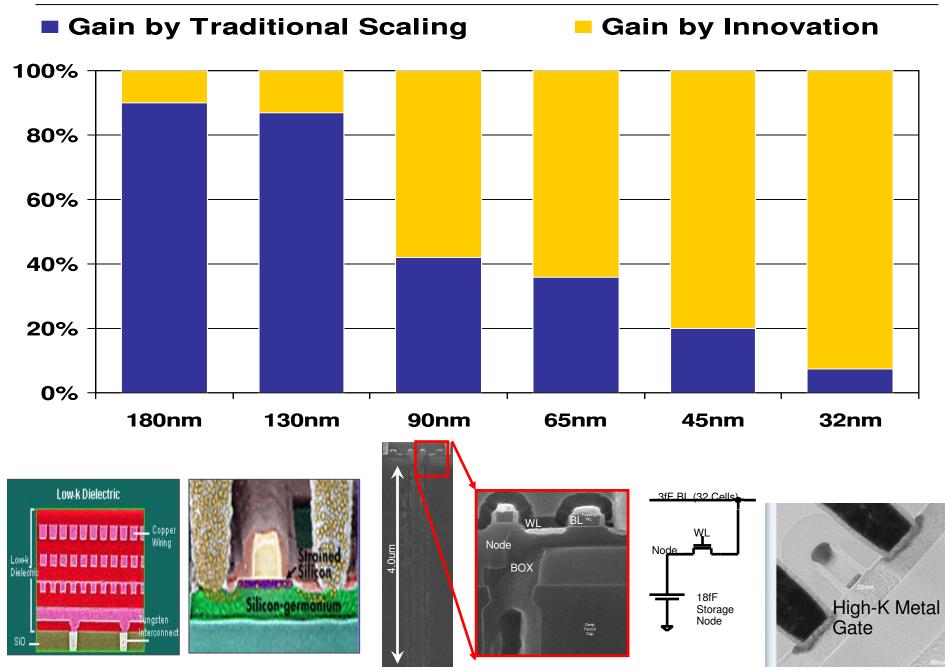

## **CMOS Scaling Continued**

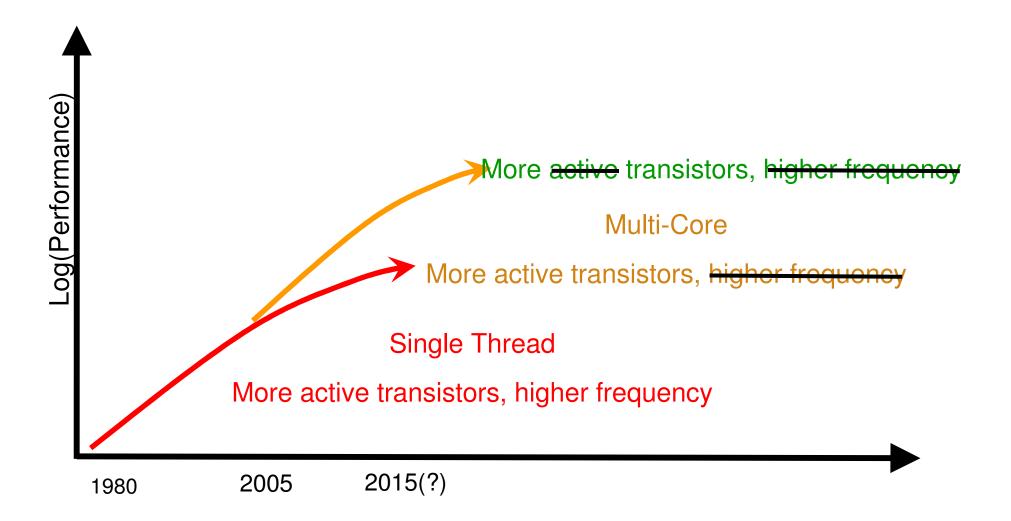

## **Microprocessor Trends**

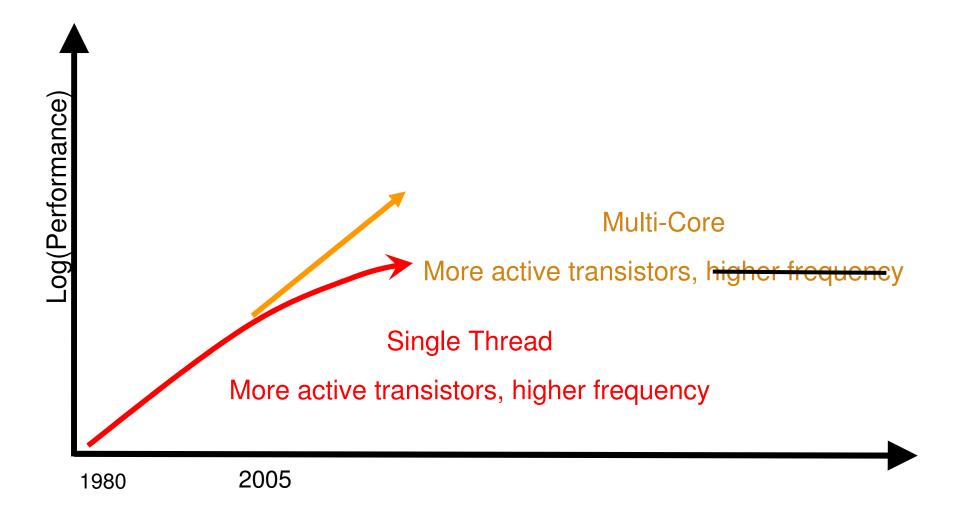

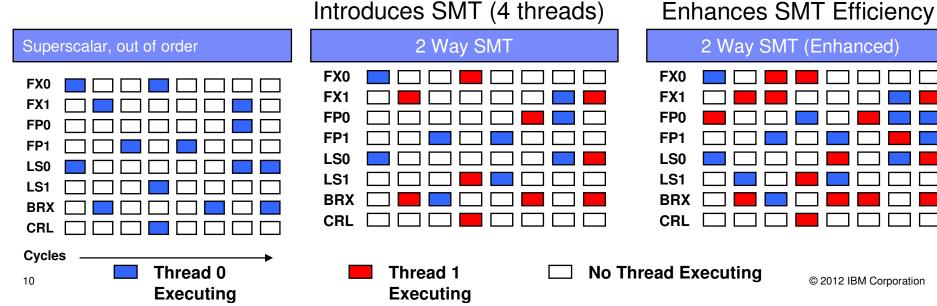

## POWER Processors Began the Multi-Core / Multi-Thread Era

Power 6

2007

Dual Core – 4 threads

Power 4 2001 Introduces Dual core

Power 5 2004 Dual Core Introduces SMT (4 threads)

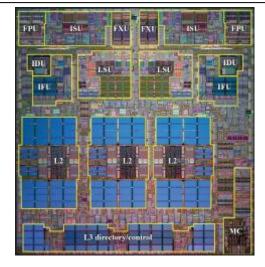

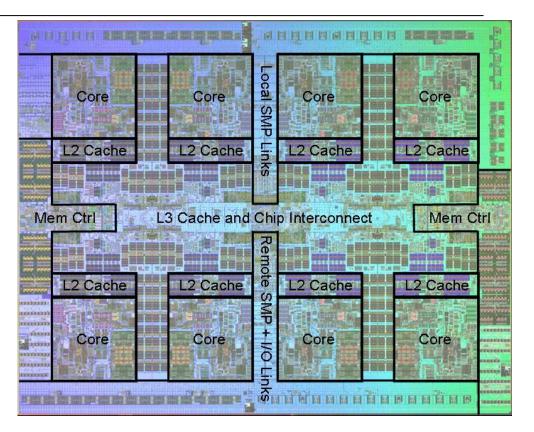

## **POWER7 Processor Chip**

- 567mm<sup>2</sup>, 45nm SOI w/ eDRAM

- 1.2B transistors

Equivalent function of 2.7B (eDRAM)

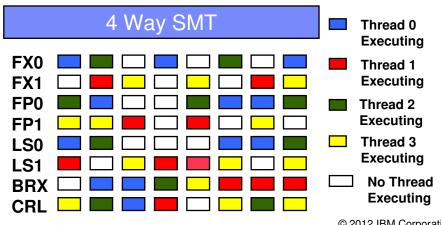

- Eight processor cores w/ 4 way SMT

32 threads / chip

- 32MB on chip eDRAM shared L3

- Dual DDR3 Memory Controllers w/ 100GB/s sustained Memory bandwidth

- Scalability up to 32 Sockets

- 360GB/s SMP bandwidth/chip

- 20,000 coherent operations in flight

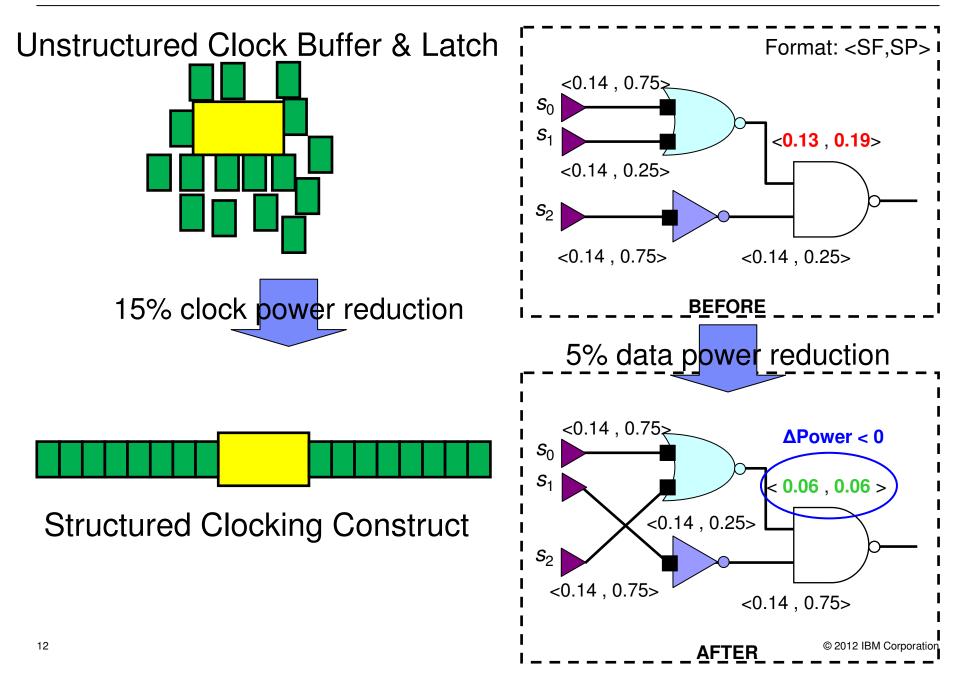

## Multi-core Era EDA: Power Analysis & Reduction

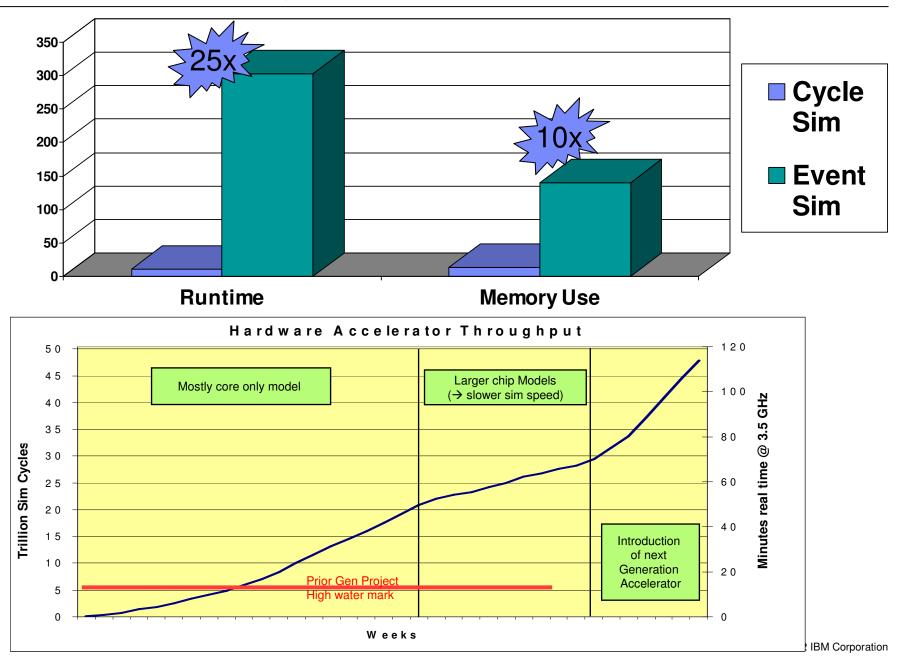

## Multi-core Era EDA: Cycle Simulation

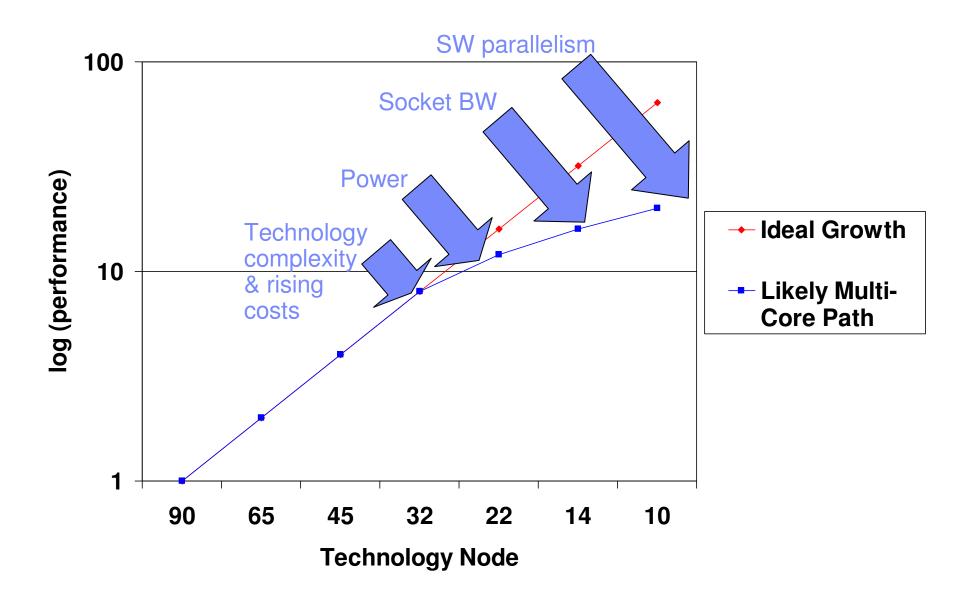

## Multi-Core Era Limiters`

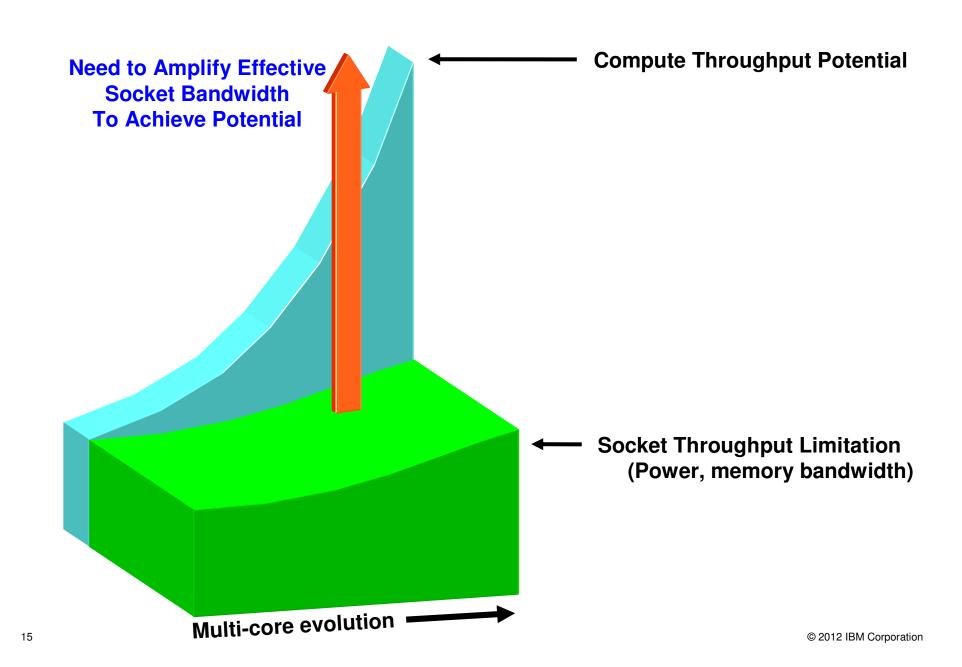

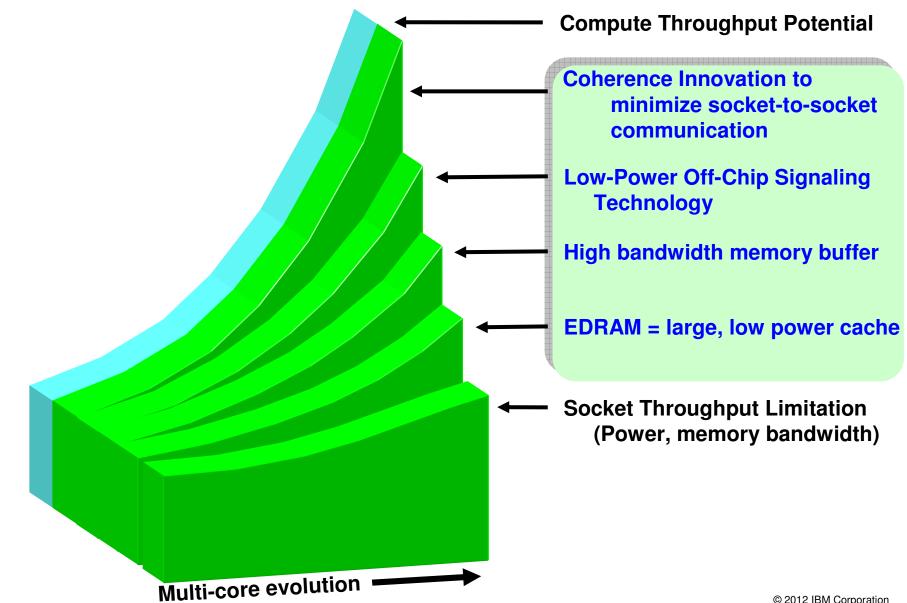

## POWER's Multi-Core Advantage

## POWER Architecture & Technology Will Extend Multi-Core Gains

## Microprocessor Trends

## Microprocessor Trends: The Next Era

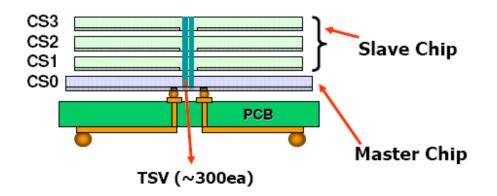

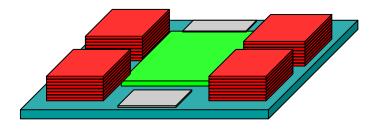

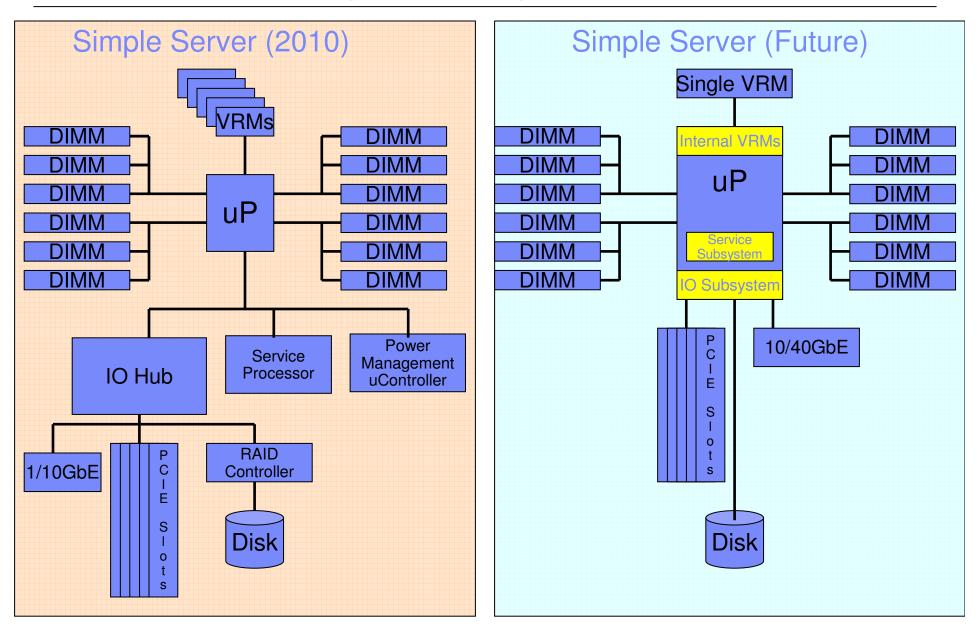

## Innovation Era: System Level Technologies

#### 3D Stacking with Through Silicon Vias

#### Single Processor–Memory Socket

**Silicon Photonics**

#### **FPGA Accelerators**

#### Flash Memory / SSD

## Innovation Era: Heterogeneous Integration

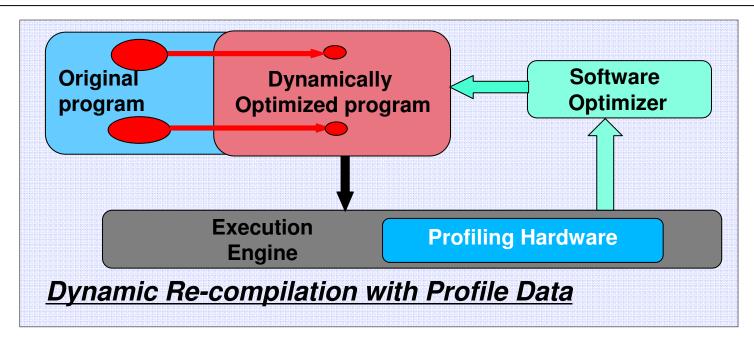

## Innovation Era: Hardware-Software Co-Optimization

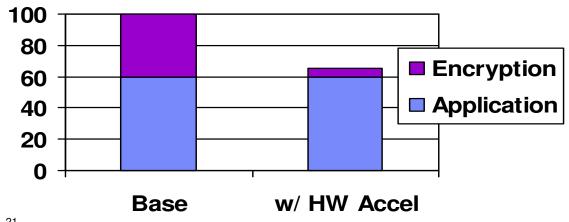

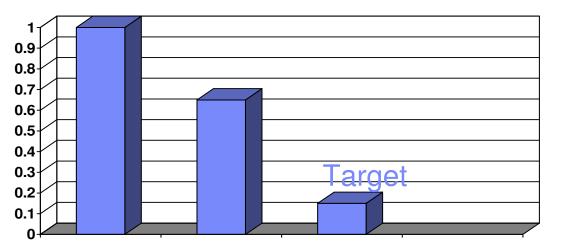

#### **Benefit of Specialized HW** Acceleration

**Specialized HW** acceleration viable in many areas •Graphics Compression Cryptography •More....

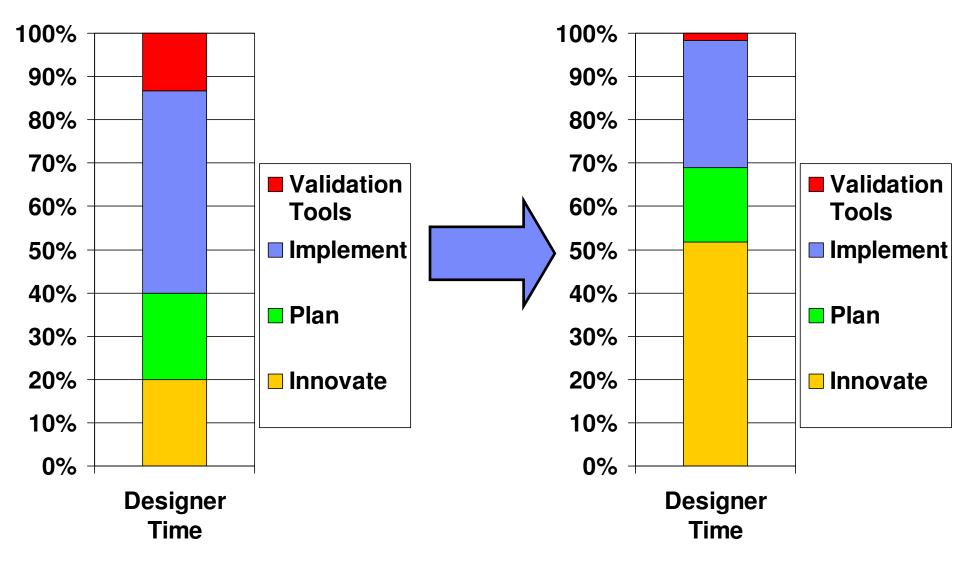

## Designer Time: Technology-Driven Eras vs. Innovation Era

## **Technology Focused**

## **Innovation Focused**

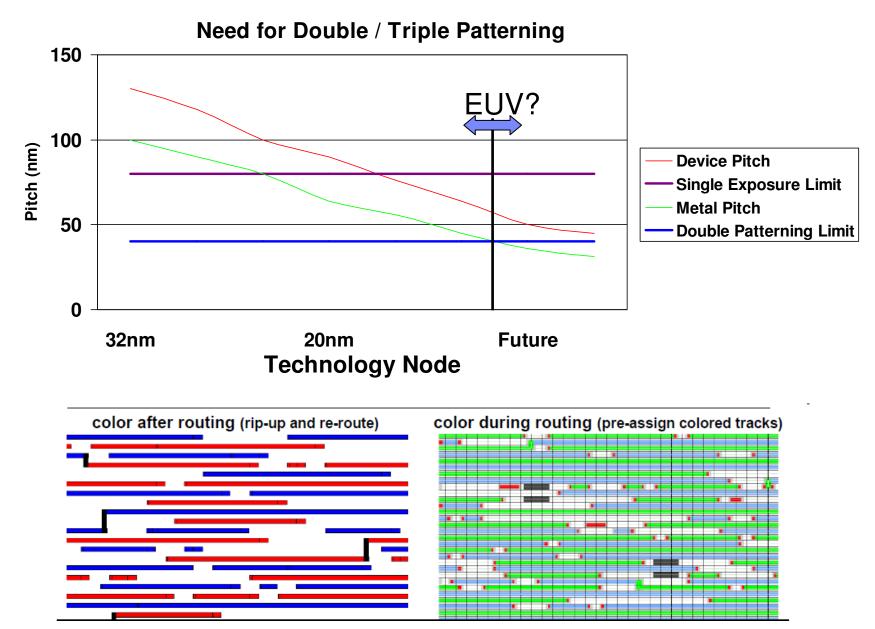

## Manage Technology Complexity: Double Patterning

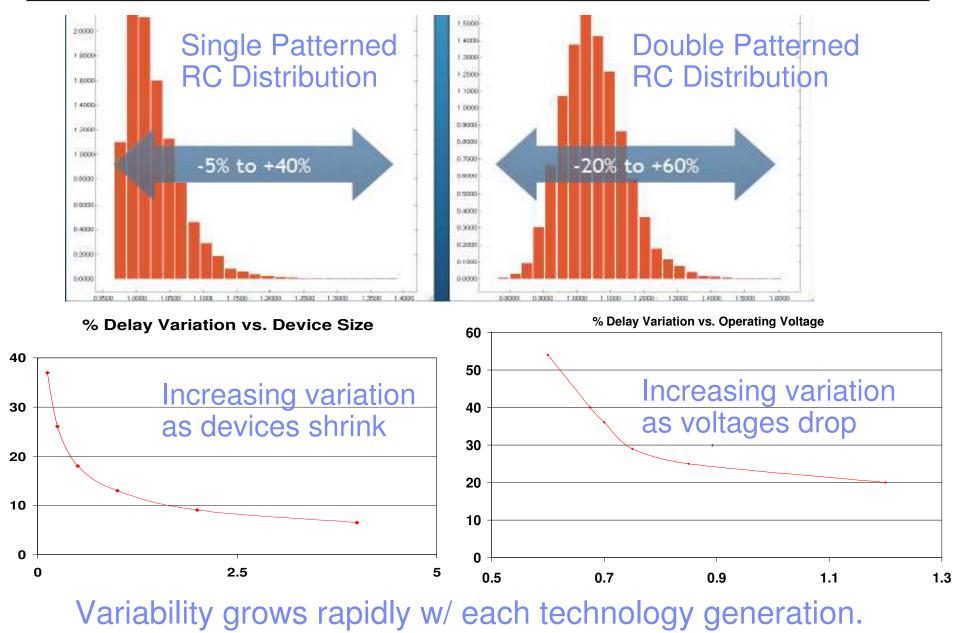

## Manage Technology Complexity: Extreme Variability

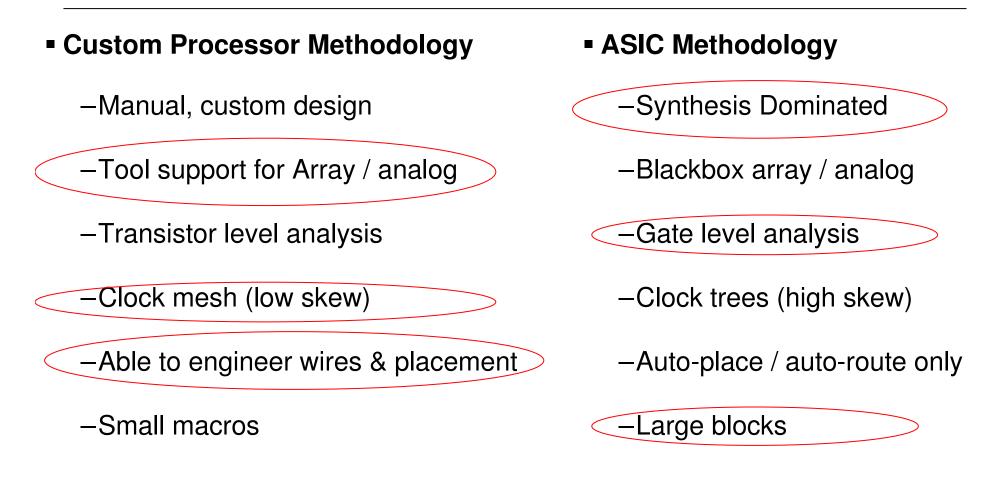

## Productivity & TAT: Merge ASIC Productivity with Custom Performance

# Custom performance w/ ASIC productivity

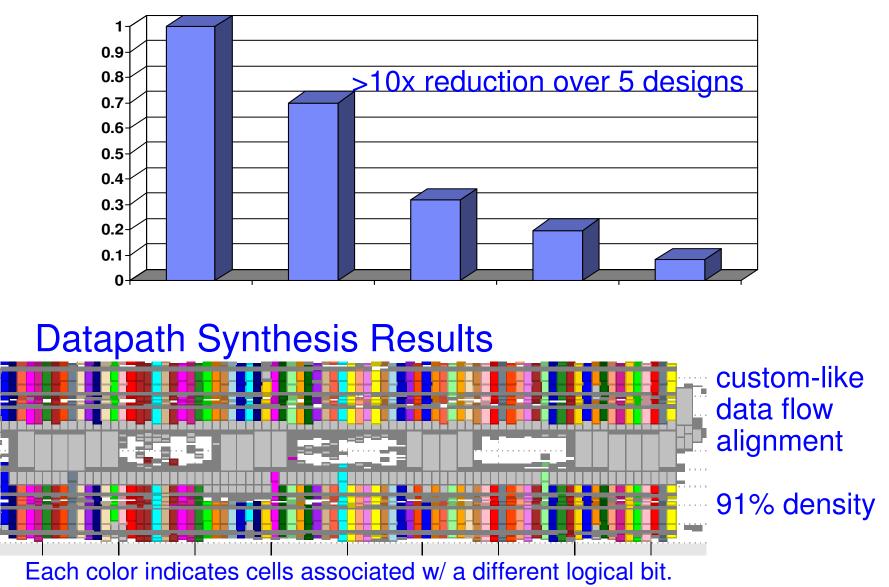

## Productivity: Reduce Custom Design

#### # of Customs over Time

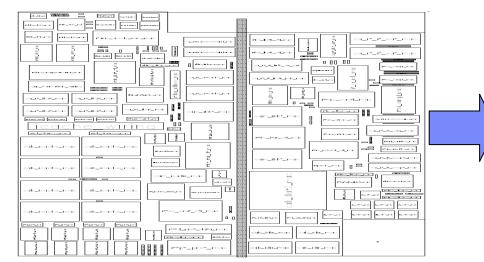

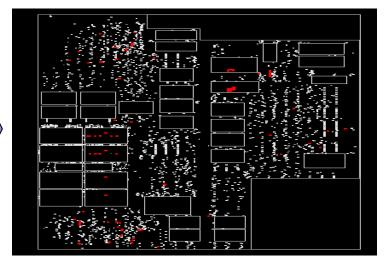

## Productivity: Reduce # of Design Partitions

## # of Macros over Time

60 logic macros, 25 customs, 14 unique arrays/RFs

1 macro, 0 customs, 9 unique arrays / RFs Reduced area & power; equal cycle time © 2012 IBM Corporation

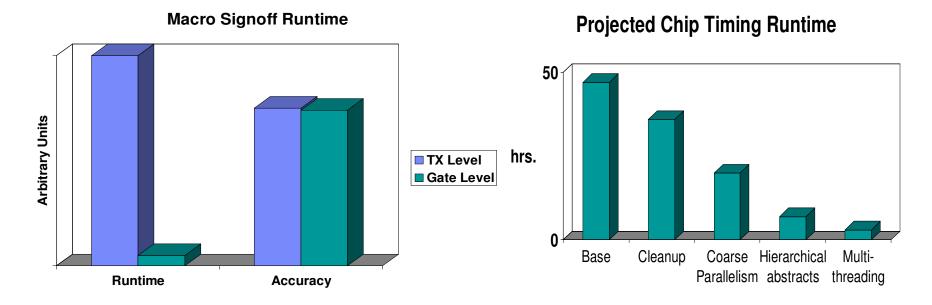

## TAT: Gate-Level Analysis, Hierarchical Abstraction & Multi-Threading

- Fast macro and global analysis tools allow designers to iterate more quickly resulting in reduced implementation time

- Gate level analysis provides orders-of-magnitude speedups over transistor level analysis

- Hierarchical abstraction & multi-threading can provide 5-10x gains in chip level analysis

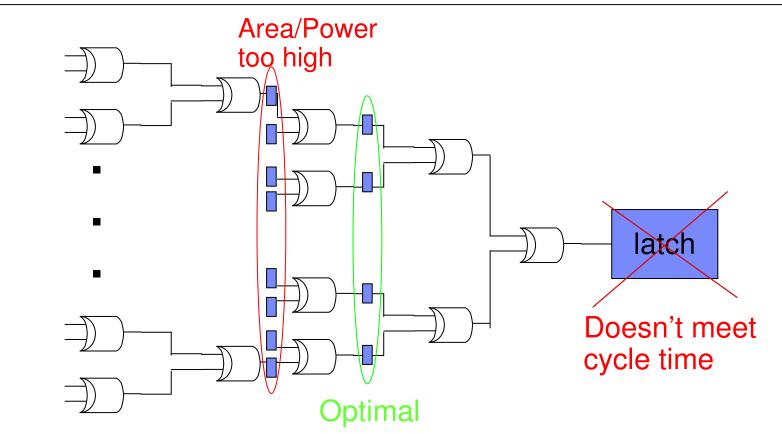

## Productivity: Retiming

- Significant designer effort spent in optimizing cycle boundaries

- Retiming enables synthesis to optimally locate latches to balance timing/area/power

- Invention is required to seamlessly handle verification implications

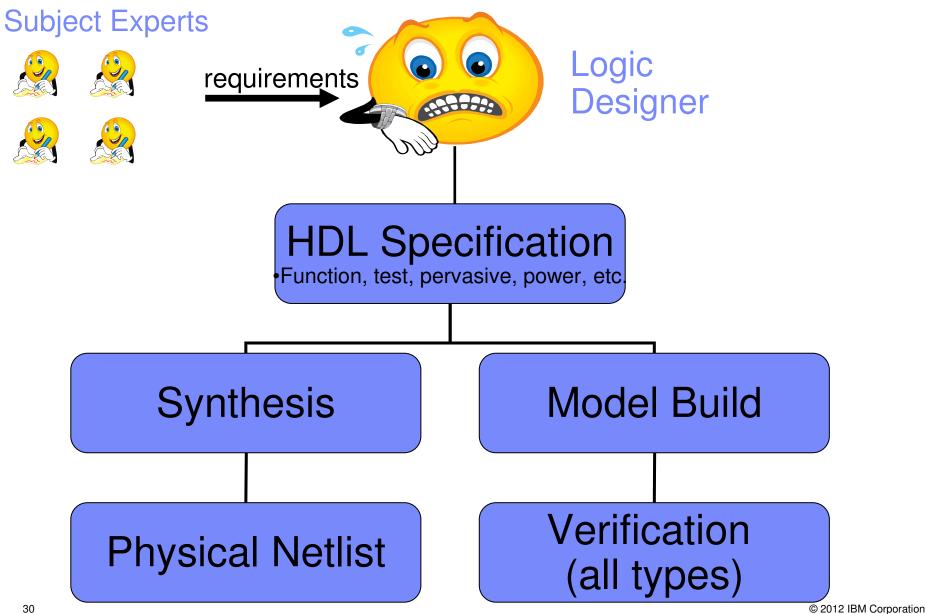

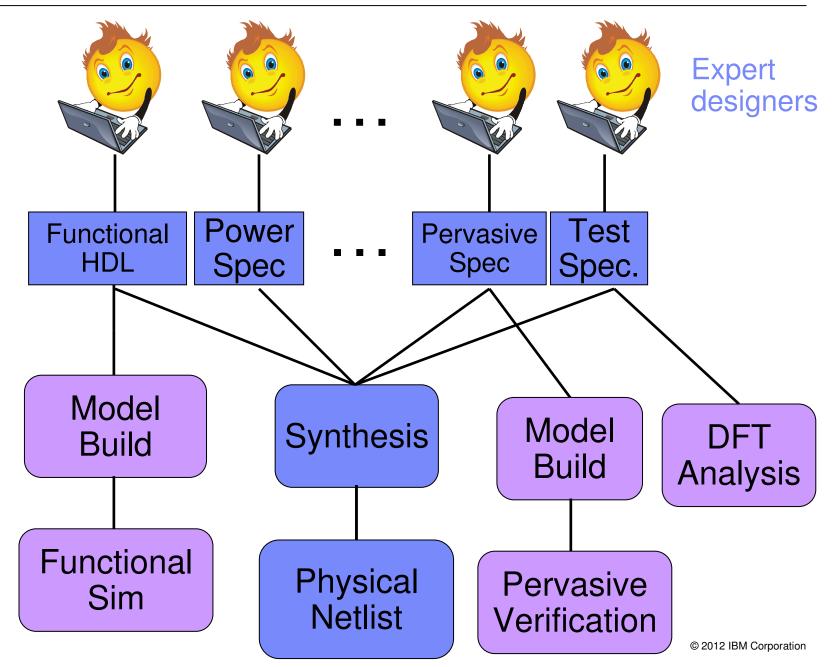

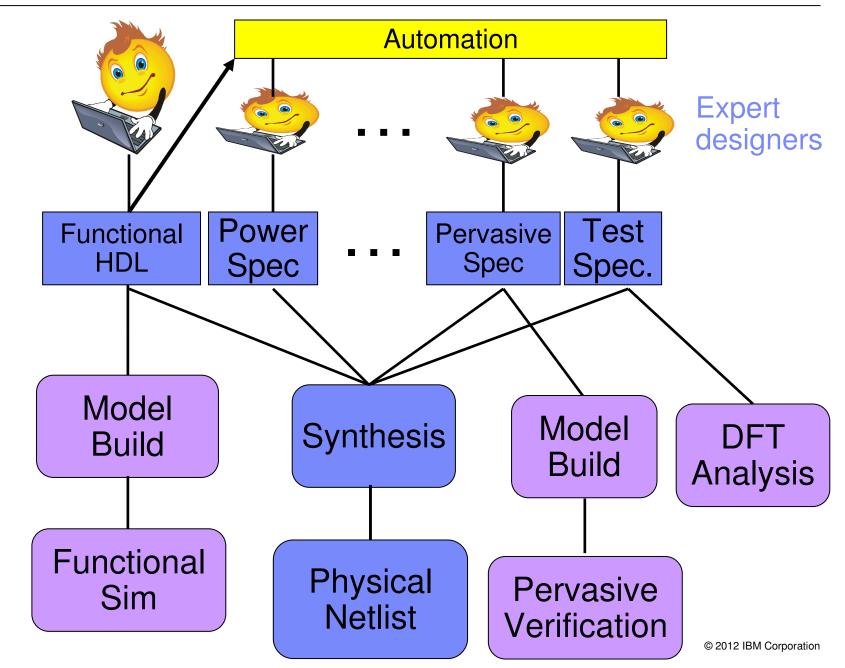

## Productivity: Traditional Design Flow

## Productivity: Aspect-Oriented Design Flow

## Productivity: Aspect-Oriented Design Flow

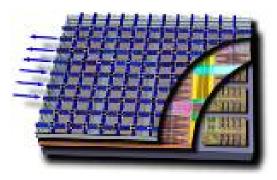

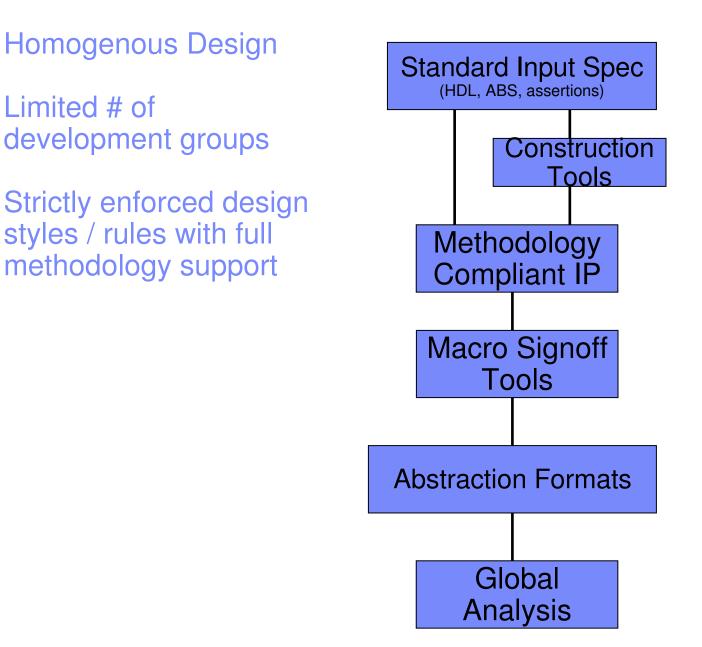

## Multi-Core Era Integration: Homogeneous IP

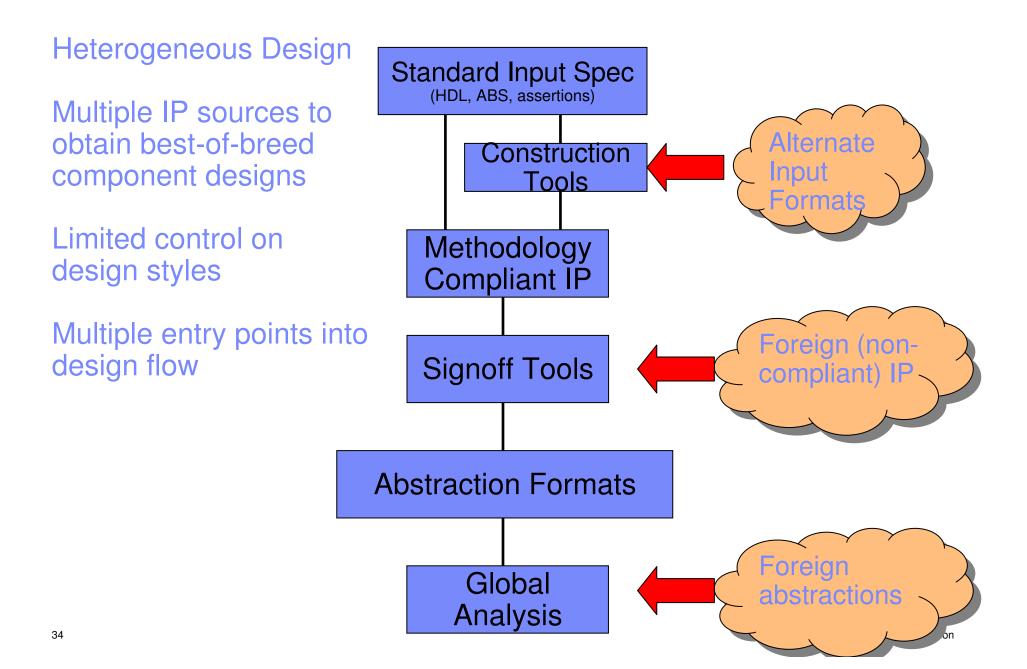

## Innovation Era Integration: Heterogeneous IP

Moore's law continues.....

- However, we will need MORE INNOVATION, not just more cores to leverage it

- EDA tools need to provide MORE

PRODUCTIVITY to enable designer innovation