# High Voltage Devices on Scaled Technologies for RF and Power Management

# Seth J. Wilk,

William Lepkowski, Trevor J. Thornton

SJT Micropower and the SBIR program

Outline

- Silicon MESFET Overview

- High Voltage Capability

- Modeling and Measured MESFETs

- Power Management Applications

- RF Applications

# SJT Micropower Overview

# Company:

- SJT Micropower is a fabless design house based in Phoenix, AZ

- Startup out of Arizona State University

- Multiple SBIR and STTR contracts awarded in past 4 years (~\$3M)

# Technology:

Patented high voltage MESFETs which can be fabricated on SOI CMOS with <u>no additional cost</u>

### Status:

- Devices taped out down to 45nm

- Technology has been demonstrated at multiple foundries on both partially and fully depleted SOI and on both SOI and SOS

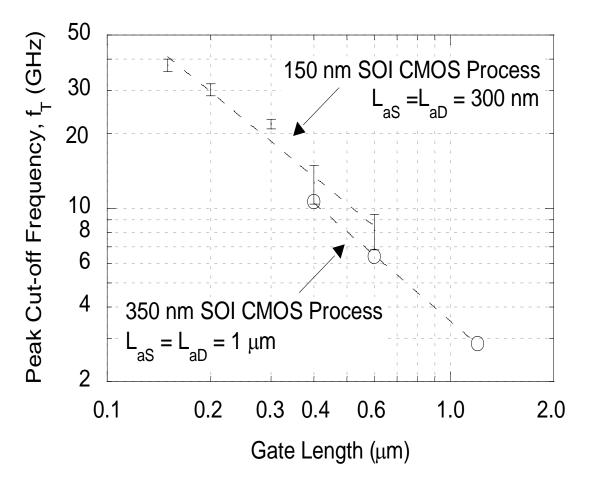

- Cutoff Frequency ~40GHz on 150nm technology, suitable for RF

# SJT\_Micropower

# SBIR Funding

#### **Small Business Innovative Research:**

Each year, Federal agencies with extramural research and development (R&D) budgets that exceed \$100 million are required to allocate 2.5 percent of their R&D budget to these programs. Currently, eleven Federal agencies participate in the program:

#### **Three Phase Program:**

- Phase I. The objective of Phase I is to establish the technical merit, feasibility, and commercial potential of the proposed R/R&D efforts \$150,000 total costs for 6 months.

- **Phase II**. The objective of Phase II is to continue the R/R&D efforts initiated in Phase I. \$1,000,000 total costs for 2 years.

- Phase III. The objective of Phase III, where appropriate, is for the small business to pursue commercialization objectives resulting from the Phase I/II R/R&D activities. The SBIR program does not fund Phase III

http://www.sbir.gov/

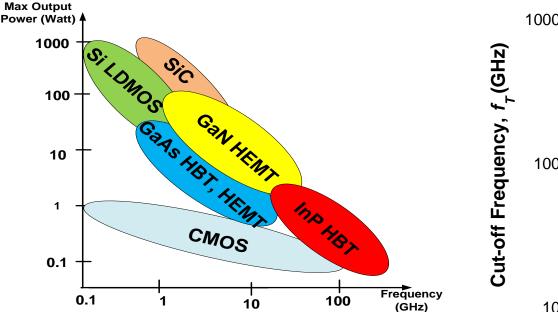

## The Problem with CMOS

#### The Problem

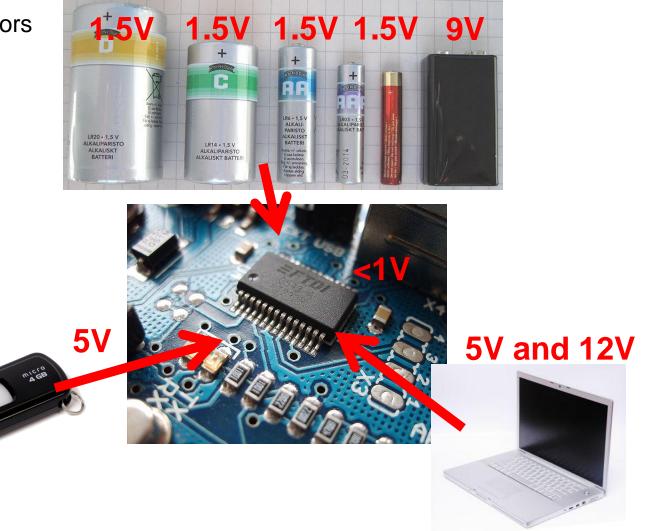

Existing Scaled Transistors are Low Voltage <1V

<u>How do you connect</u> <u>these common items</u> <u>to new chips?</u>

<u>How do you make</u> <u>these common items</u> <u>work with new chips?</u>

# Main Technology and Talk Focus

#### High Voltage on Low Voltage CMOS

Device fabricated on a 45nm process where CMOS limited to ~1V drain voltage

No changes required to the CMOS Process Flow

SJT\_Micropower

# ASU/SJT Micropower Si-MESFET Milestones

- Successful at 5 different foundries & 6 CMOS processes (45nm – 800nm) without changing any of the process flow

- IBM, Honeywell, Peregrine, SPAWAR, MIT Lincoln Labs

- Highest breakdown 55 V (350nm PD-SOI CMOS)

- Peak  $f_T \sim 45$  GHz (150nm PD-SOI CMOS)

- Peak  $f_{max}$  > 55 GHz (45nm PD-SOI CMOS)

- Have developed calibrated TOM3 and VerilogA models

- MESFETs based circuits that we have designed and tested:

- LNA, LDO, Buck Regulator, PA, Polar Modulated PA, opamp, and voltage reference

SJT\_Micropower

## Technology Benefits

| Easy      | y to [ | Imple  | ment | with      |

|-----------|--------|--------|------|-----------|

| <u>ex</u> | istin  | ig SOI | CM   | <u>OS</u> |

- No additional cost to use technology

- Existing CMOS already has steps required to fabricate device

#### **Extreme Environment**

- High Temperature

- Radiation Hardened, Schottky interface is less susceptible to radiation induced damage than MOSFET metal-oxidesemiconductor interface

#### Helps combat obsolescence

- Use existing, older technology high voltage parts with modern low voltage digital CMOS

- Use Existing 5V supply rails

- Conversion of voltages on chip

Simpler RF PA Development

Larger voltage swing allows higher power and easier, more efficient matching to 50Ω

8

SJT Micropower and the SBIR program

Outline

- Silicon MESFET Overview

- High Voltage Capability

- Modeling and Measured MESFETs

- Power Management Applications

- RF Applications

#### What is a MESFET

#### **MESFET:** Metal Semiconductor Field Effect Transistor

#### More common to have SiC or GaAs but a MESFET can be Silicon as well

#### CRF24010 10 W, SiC RF Power MESFET

Cree's CRF24010 is an unmatched silicon carbide (SiC) RF power Metal-Semiconductor Field-Effect Transistor (MESFET). SiC has superior properties compared to silicon or gallium arsenide, including higher breakdown voltage, higher saturated electron drift velocity, and higher thermal conductivity. SiC MESFETs offer greater efficiency, greater power density, and wider bandwidths compared to Si and GaAs transistors.

Package Types: 440196 and 440166 PN's: CRF24010P and CRF240105

#### FH101 High Dynamic Range FET

#### **Product Features**

#### • 50 – 4000 MHz

- 18 dB Gain

- +18 dBm P1dB

- +36 dBm OIP3

- Low Noise Figure

- Single or Dual Supply Operation in the environmentally friendly lead-free/green/RoHS-

- MTTF > 100 years

- Lead free/green/RoHS-compliant SOT-89 Package

#### **Applications**

- Mobile Infrastructure

- CATV / DBS

- WLAN / ISM

- · Defense / Homeland Security

10

#### **Functional Diagram**

| Function | Pin No. |  |

|----------|---------|--|

| Gate     | 1       |  |

| Drain    | 3       |  |

| Source   | 2,4     |  |

**Product Description**

The FH101 is a high dynamic range FET packaged in a

low-cost surface-mount package. The combination of low

noise figure and high output IP3 at the same bias point

makes it ideal for receiver and transmitter applications. The device combines dependable performance with superb

quality to maintain MTTF values exceeding 100 years at

mounting temperatures of +85°C. The FH101 is available

The device utilizes a high reliability GaAs MESFET

technology and is targeted for applications where high linearity is required. It is well suited for various current

and next generation wireless technologies such as GPRS,

GSM, CDMA, and W-CDMA. In addition, the FH101 will

work for other applications within the 50 to 4000 MHz

compliant SOT-89 package.

frequency range such as fixed wireless.

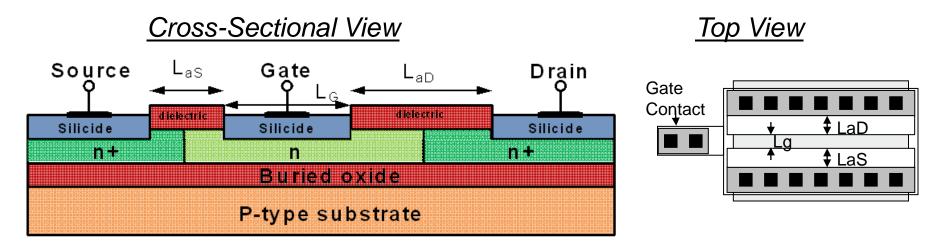

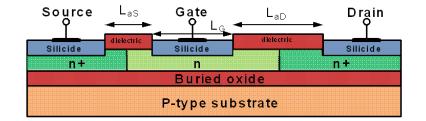

# Si-MESFET Structure and Background

- Majority carrier device—does not suffer from floating body effects

- Schottky gate created by a silicided contact on lightly doped n-well

- Controlled by vertically depleting the channel

- Depletion Mode—Vt is usually in the range of -0.5V to -1V

- Gate Length (Lg) is limited by the separation of the oxide spacers

- Typically contact the gate outside of LaS & LaD to shorten Lg

- Can size LaS and LaD to give optimal RF performance and breakdown

#### SJT\_Micropower

# Fabrication: n-MOSFETs vs.n-MESFETs

| a) <u>n-MOSFET</u> | <u>n-MESFET</u>                                           |  |  |  |

|--------------------|-----------------------------------------------------------|--|--|--|

| p-well             | n-well                                                    |  |  |  |

| Buried Oxide       |                                                           |  |  |  |

| p-type substrate   |                                                           |  |  |  |

| b)                 |                                                           |  |  |  |

| p-well             | n-well                                                    |  |  |  |

| Buried Oxide       |                                                           |  |  |  |

| p-type substrate   |                                                           |  |  |  |

| c)                 |                                                           |  |  |  |

| p-well             | n-well                                                    |  |  |  |

| Buried Oxide       |                                                           |  |  |  |

| p-type substrate   |                                                           |  |  |  |

| d)                 | I<br>I<br>I<br>I<br>I<br>N <sup>+</sup><br>N <sup>+</sup> |  |  |  |

| Buried Oxide       |                                                           |  |  |  |

| p-type substrate   |                                                           |  |  |  |

| e)                 |                                                           |  |  |  |

| p-well             | n-well                                                    |  |  |  |

| Buried Oxide       |                                                           |  |  |  |

| p-type substrate   |                                                           |  |  |  |

| SJT_Micropower     |                                                           |  |  |  |

- a) Fabrication steps are the same through the LOCOS step

- b) MOS gate is defined

- SB used to pattern the oxide spacers of a MOSFET is used to define the gate length of the MESFET

- d) Source/drain implant step is same for the MOSFET & MESFET.

- e) CoSi<sub>2</sub> salicide used to form the lowresistance contacts is used to form a Schottky contact over the lightly doped channel

- \*\*\*Back-end processing steps same as SOI/SOS CMOS

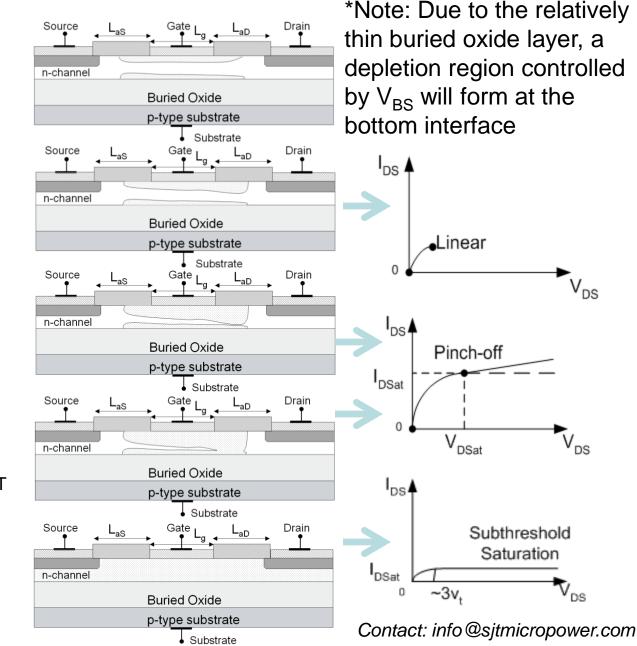

## Cross-Section MESFETs

#### Regions of Operation

$V_{GS} = 0 \ V \ \& \ V_{DS} = 0 \ V$

Linear Region:  $V_{GS} = 0 V \& small V_{DS}$

Pinch-off:  $V_{GS} = 0 V \& V_{DS} = V_{DSAT}$

Saturation Region:  $V_{GS} = 0 V \& V_{DS} > V_{DSAT}$

Subthreshold Region: V<sub>GS</sub> < V<sub>t</sub> & V<sub>DS</sub> = 0 V SJT\_Micropower

#### Major Differences between SOI MOSFETs and MESFETs

|                                       | MOSFET                                                                      | MESFET                                                                          | MESFET Advantages                                                                                                                                                         |

|---------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Threshold<br>Voltage, V <sub>th</sub> | Enhancement mode<br>(normally-off)<br>e.g. $V_{th} = +0.6V$ for<br>N-MOSFET | Depletion mode<br>(normally-on)<br>e.g. V <sub>th</sub> = -0.5V for<br>N-MESFET | The availability of depletion<br>mode devices alongside<br>traditional enhancement mode<br>devices allows for greater<br>flexibility in circuit design                    |

| Conduction<br>Type                    | Minority carrier,<br>inversion channel                                      | Majority carrier,<br>depletion channel                                          | MESFET does not suffer from<br>floating body effects such as the<br>kink effect. It does not require<br>the body-tie contacts often used<br>as part of SOI CMOS.          |

| Self-aligned                          | Yes                                                                         | No                                                                              | The extended drift region from<br>the gate to the drain $(L_{aD})$ gives<br>the MESFET a high breakdown<br>voltage.                                                       |

| Gate Material                         | Metal-Oxide-Semi                                                            | Metal Silicide                                                                  | The Schottky gate of the<br>MESFET can support<br>significant current flow. It is<br>tolerant of high voltage<br>excursions, radiation and wide<br>temperature variations |

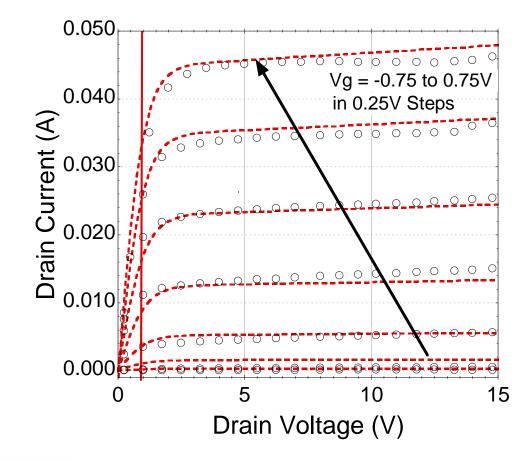

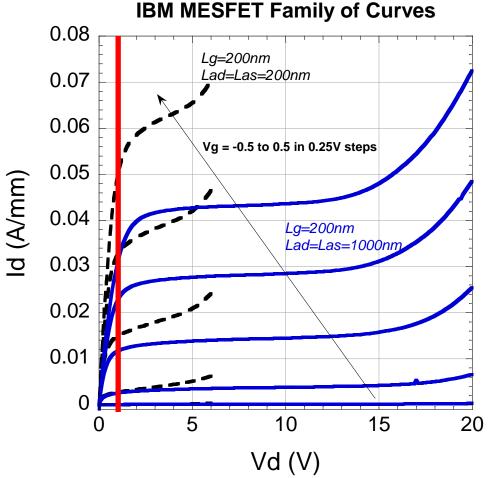

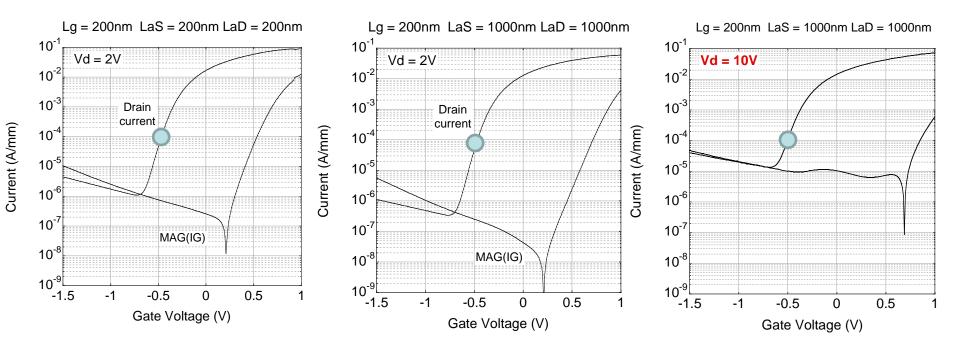

Family of Curves

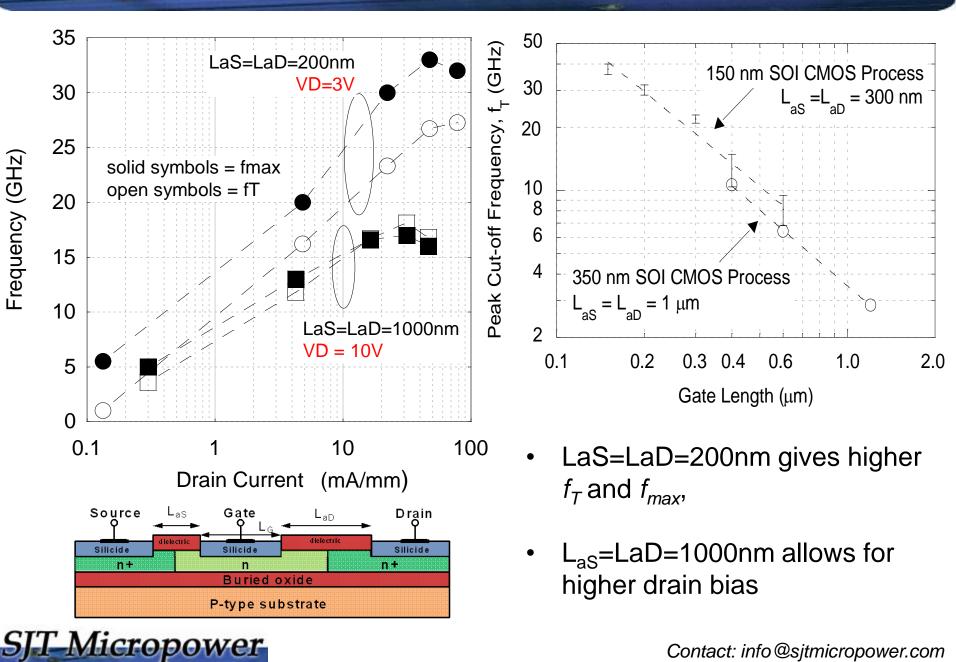

LaS=LaD=200nm gives highest <u>current drive</u>

#### but

LaS=LaD=1000nm allows for higher voltage drive (>20V)

Note that the red line shows an approximate breakdown voltage of a MOSFET

SJT\_Micropower

#### Turn-on Characteristics / Gummel Curves

The threshold voltage is relatively independent of LaS and LaD

Vth close to -0.5V for both LaS=LaD=200nm and LaS=LaD=1000nm

SJT\_Micropower

Contact: info@sjtmicropower.com

16

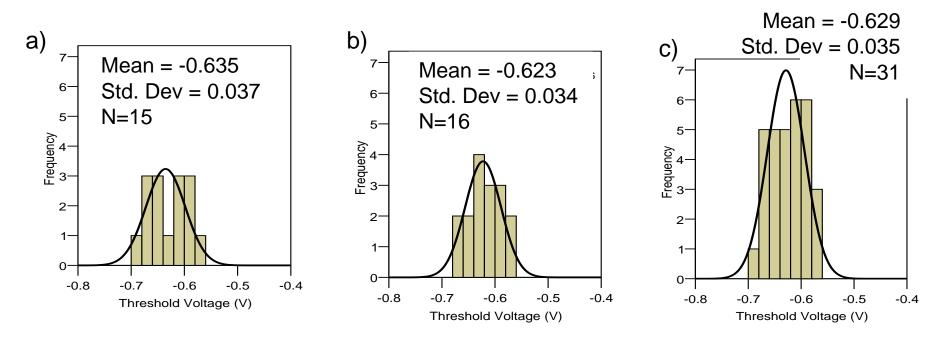

MESFETs structures have been fabricated on multiple foundry runs. Key parameters such as Vt (shown here) have been measured across the different runs on multiple die.

The threshold voltage distributions for (a) Run 1 (b) Run 2. The distribution across all 31 devices is shown in (c). We are currently adding to these statistics.

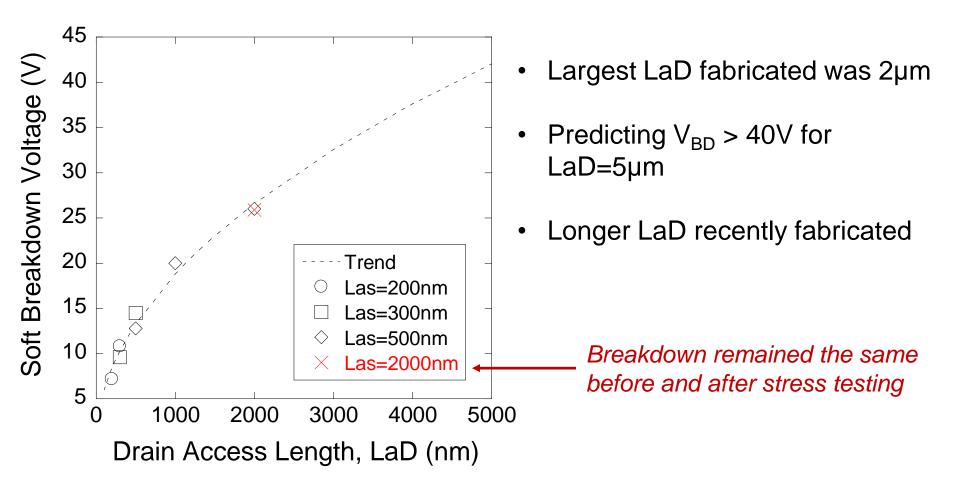

Soft Breakdown Characteristics – 45nm Technology<sup>18</sup>

The (soft) breakdown voltage appears to be proportional to LaD/In(LaD) which suggests avalanche breakdown

SJT\_Micropower

#### Ft of MESFETs at different Nodes

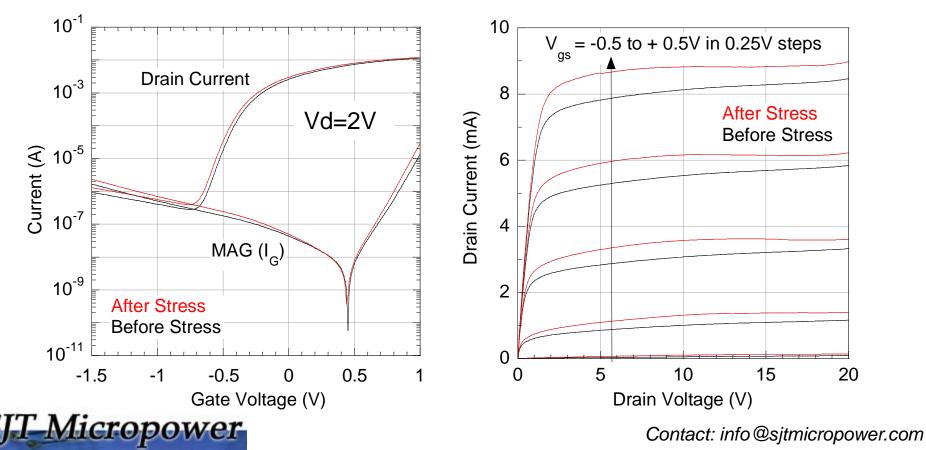

# Accelerated Lifetime Test

- MESFET measured had Lg=200nm and LaS=LaD=2000nm

- Stress Conditions: 160°C at a fixed bias of Vd=10V, Vg=0.5V for 168 hours.

- Small increase in drain current and marginal shift in Vt was observed after stress but otherwise there were few changes in the MESFET's operation.

- Off-state breakdown voltage remained at ~25V after the stress test.

SJT Micropower and the SBIR program

Outline

- Silicon MESFET Overview

- High Voltage Capability

- Modeling and Measured MESFETs

- Power Management Applications

- RF Applications

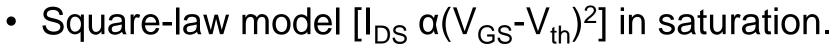

SPICE Model

- Exponential characteristics  $[I_{DS} \alpha \exp(V_{GS} V_{th})]$  in sub-threshold.

- Well-defined extraction procedure.

- Correlated to analytical models to ease the development of higher level models.

- Sub-circuits for leakage effects, breakdown voltage and short-channel effects.

- Charge-based capacitance model.

# Availability of Model in Cadence and ADS Important

TOM3 Model

MESFET modeling consists of :

- DC Measurements

- S-parameter measurements of GSG devices at different bias conditions

- Pad de-embedding

- Extrinsic parameters extraction using a ColdFET method

- VDS=0 and gate is turned on very hard

- Intrinsic parameter extraction based on DC and S-parameters measurements

$$I_{ds} = \beta \times (V_G)^{\mathcal{Q}} \times f_k \times (1 + \lambda V_{ds})$$

$$f_k \approx \tanh(\alpha V_{ds})$$

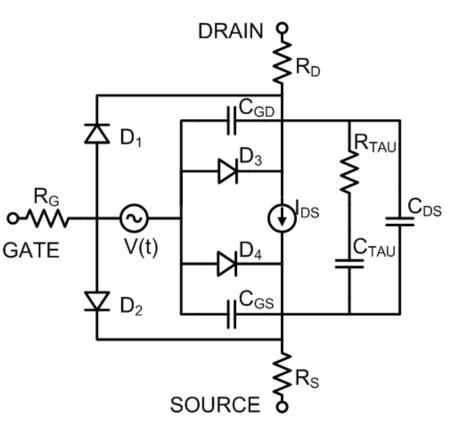

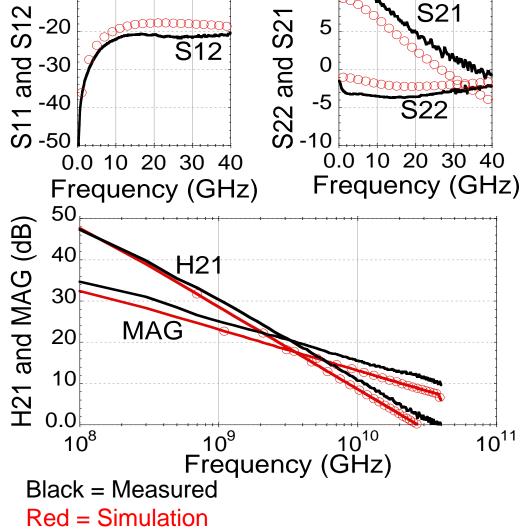

### Turn-on Characteristics

TOM3 Model shows a good fit across different drain and gate bias conditions

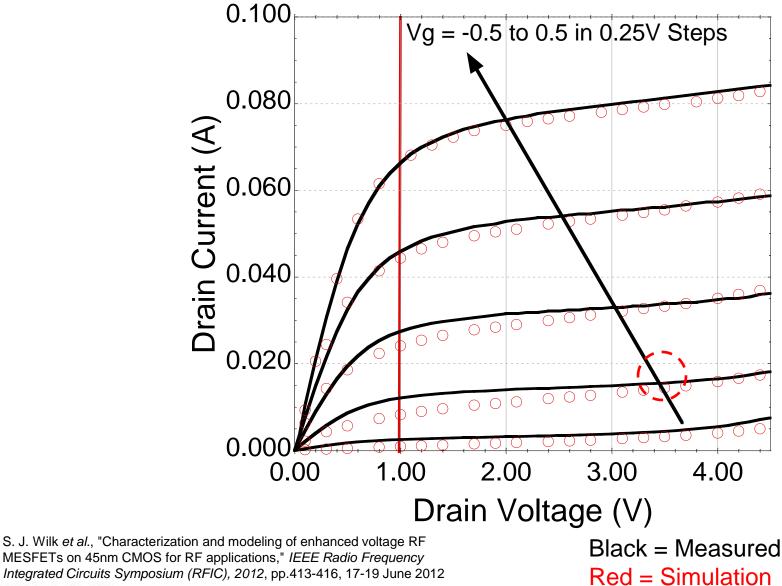

### Family of Curves

Integrated Circuits Symposium (RFIC), 2012, pp.413-416, 17-19 June 2012

**RF** Characteristics

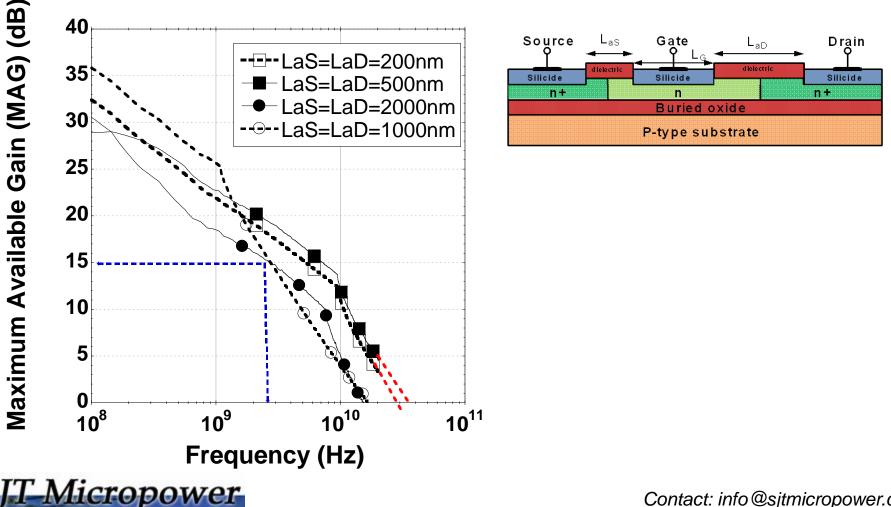

27 Maximum Available Gain of MESFETs on 45nm Process

- All MESFETs measured thus far have more than 15 dB gain below 2.5GHz

- Can improve fmax by optimizing LaS

- LaS can be equated to source degeneration of an amplifier

# S Parameter Measurements and Model

# **Cut-off Frequency**

$$f_T \cong \frac{gm}{2\pi C_{GG}}$$

## Model the Gate Charge

$$Q_{GG} = Q_{GL} \times T + Q_{GH} \times (1 - T)$$

Where

**Q**<sub>GL</sub> is the low power region And

$\boldsymbol{Q}_{\textit{GH}}$  is the highpower region

# T describes the transition between regions

$$T = \exp(-Q_{GGB} \times I_{ds} \times V_{ds})$$

# Vd=2V and Vg=0.25V

Contact: info@sjtmicropower.com

5JT Micropower

SJT Micropower and the SBIR program

Outline

- Silicon MESFET Overview

- High Voltage Capability

- Modeling and Measured MESFETs

- Power Management Applications

- RF Applications

#### Power Management

#### Linear Regulator

*linear regulator* is a circuit used to maintain a steady output voltage

**Pros:** Steady Output Voltage High PSRR

#### **Buck Converter**

A **buck converter** is a stepdown DC to DC converter

**Pros:**

Efficient for larger voltage steps

#### Buck Converter and Low Dropout Linear Regulator

Efficient for larger voltage steps and can maintain output voltage

#### Cons:

Inefficient as input voltage becomes much higher than output voltage because transistor must dissipate the difference

#### Cons:

High ripple and noise can be too much for system requirements Want low dropout regulator so that the buck output can be close to the desired output voltage for best efficiency

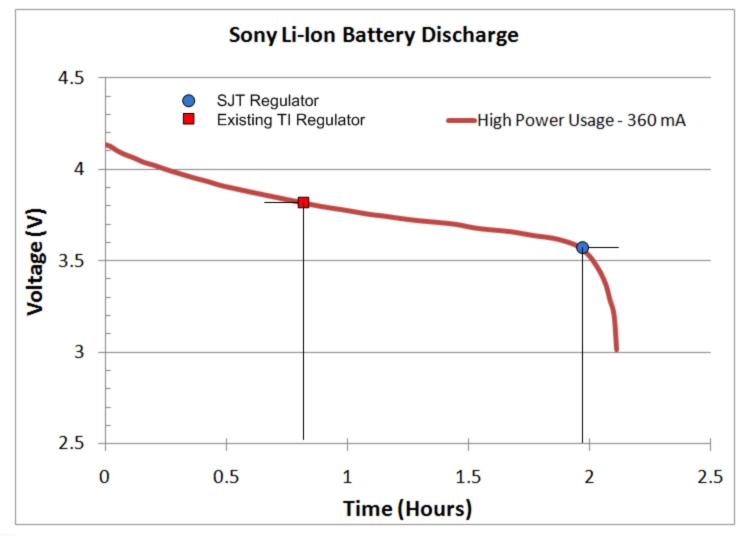

The less overhead your power management needs, the longer the device can work on a single battery charge

Integrating Power Management - Processors

Ideally, integrate power management because designers are pin constrained

How to connect the supply to the integrated circuit if the on chip transistors are low voltage?

Pin constrained if you need a specific capacitor at the output

**SJT Solution**

**Pinpoint Load Placement**

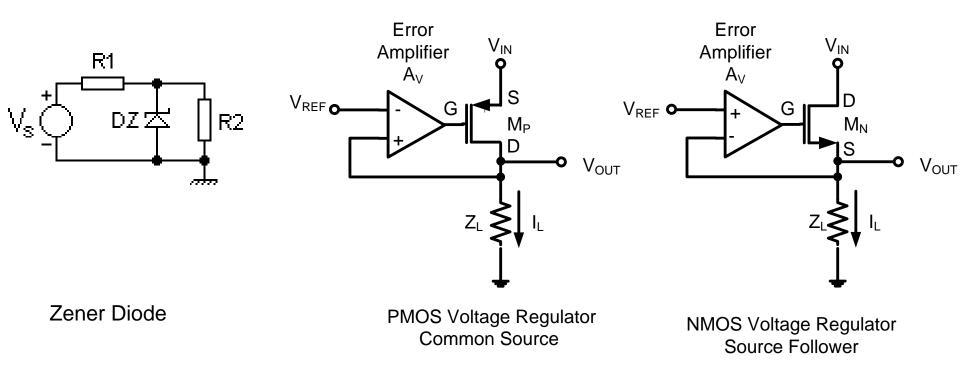

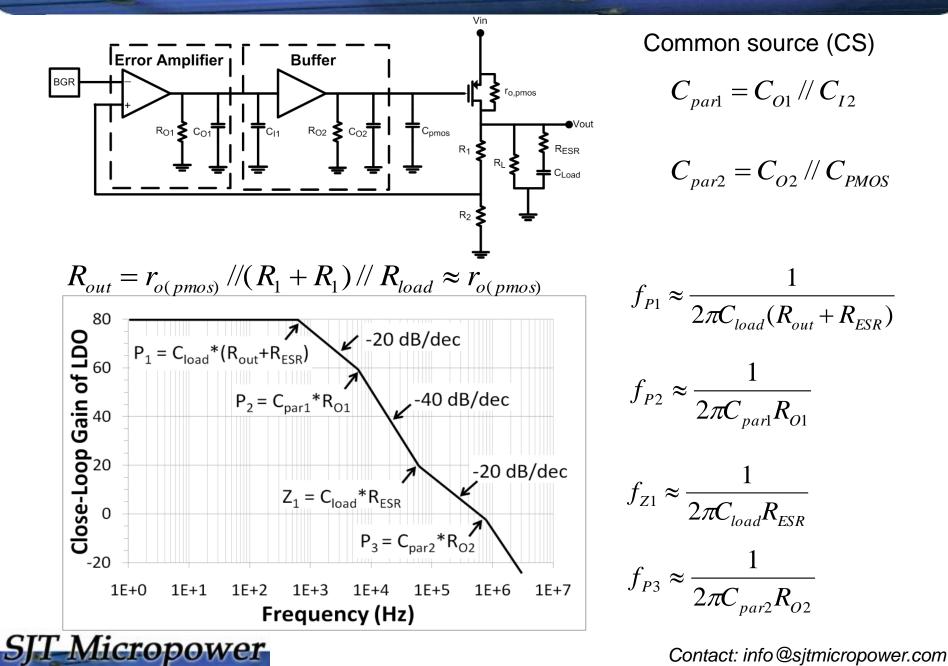

# Common Linear Regulator Topologies

Contact: info@sjtmicropower.com

33

# PMOS LDO Implementation

#### <u>Advantages</u>

- Common source (CS) configuration allows error amp to drive gate of PMOS below V<sub>out</sub>

- Can achieve very low dropout voltages

$$- V_{DO} = R_{on}^* I_{load} = V_{DSAT}$$

Note: Ideal dropout—does not include the parasitic voltage drop from metal lines

#### <u>Disadvantages</u>

- Stability concerns arise from CS configuration

- High  $R_{out}$  at  $V_{out}$  node

- Need load cap with its associated ESR

- PMOS has 2-3x lower mobility than NMOS

- Need 2-3x larger pass device to achieve a given current drive

Micropower

# PMOS LDO Implementation (Cont)

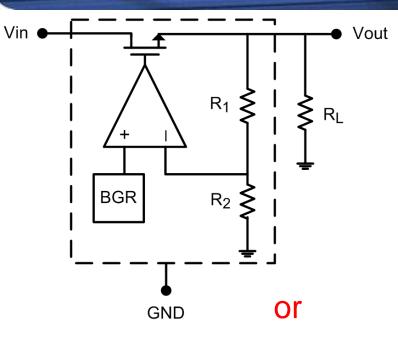

# NMOS (Enhancement Mode) LDO Implementation <sup>36</sup>

#### <u>Advantages</u>

- Source follower configuration

- $R_{out} \sim 1/gm$

- Significantly improves stability

- NMOS device has higher current drive than PMOS

- Smaller input capacitance since smaller device is needed for given current drive

- Improved transient response

#### <u>Disadvantages</u>

- Without charge pump (CP), gate must be driven to overcome V<sub>t</sub>

- Dropout is dependent on V<sub>t</sub>

$$V_{DO} = V_t + V_{DSAT}$$

Including CP negates dependence of V<sub>t</sub> but increases die size and noise

#### 37 NMOS (Enhancement Mode) LDO Implementation

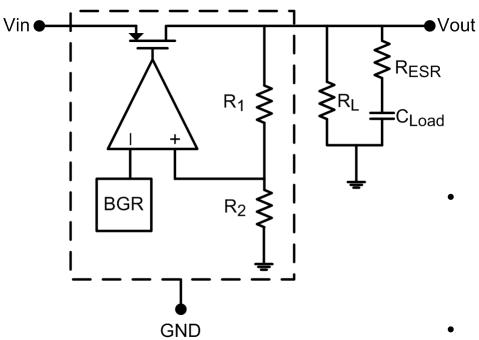

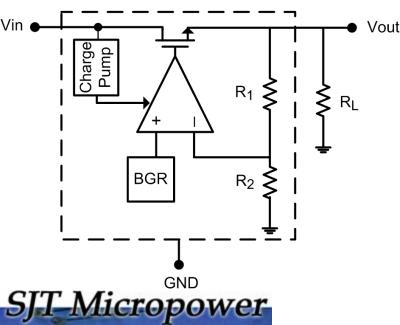

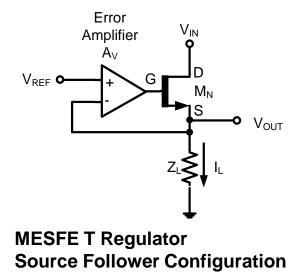

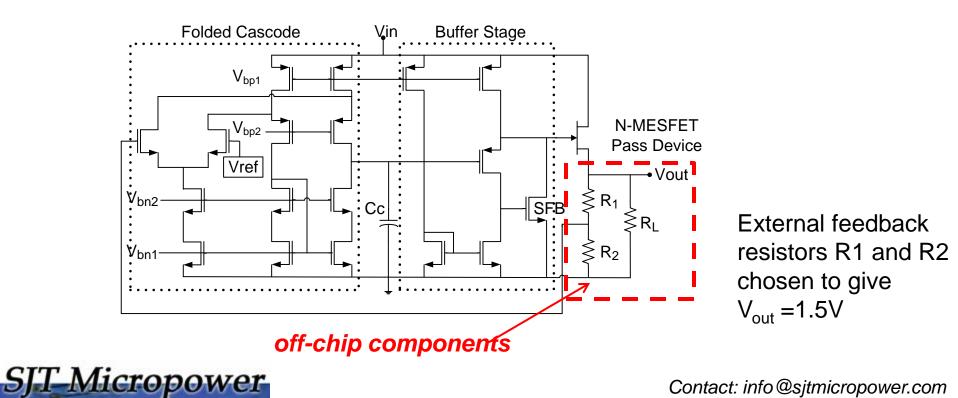

# MESFET LDO

### <u>Advantages</u>

- Combines attributes of NMOS and PMOS LDOs

- Depletion mode operation allows pass transistor to be orientated in source follower configuration without a charge pump

- Closed loop frequency response is similar to NMOS LDO

### <u>Disadvantages</u>

- Depletion mode means MESFET will conduct under most bias conditions

- Gate leakage of MESFET

### SJT\_Micropower

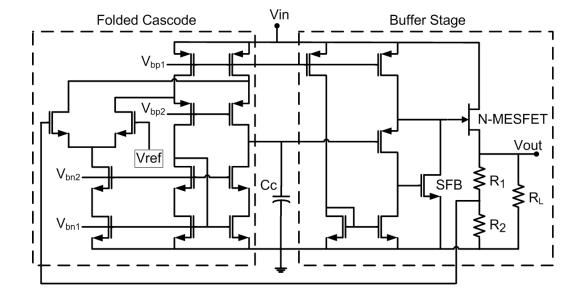

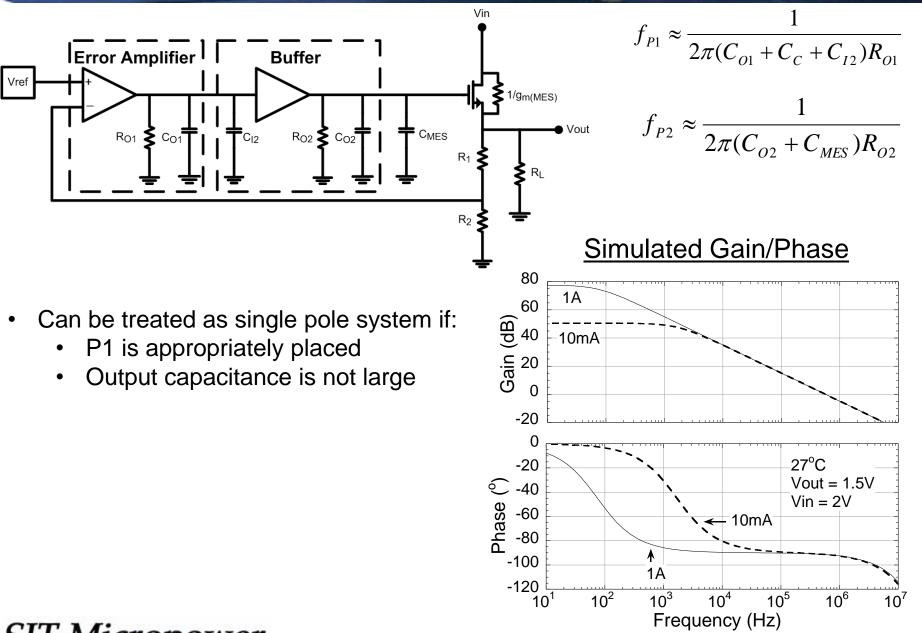

# MESFET LDO (Cont)

SJT Micropower

Contact: info@sjtmicropower.com

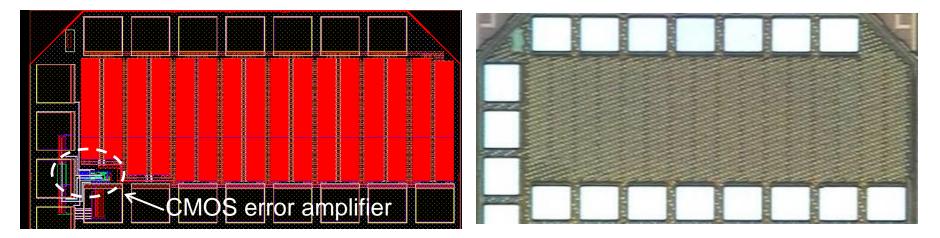

# **IBM MESFET Linear Regulator**

- Design includes a high current drive MESFET integrated with a CMOS error amplifier

- MESFET width of 152.2 mm with gate length of 200nm and LaD=LaS=200nm

- Die size of ~ 0.5mm x 1mm

- Regulator area is 0.245 mm<sup>2</sup> without the bond pads

CAD Layout

Die Photograph

# **MESFET** Linear Regulator

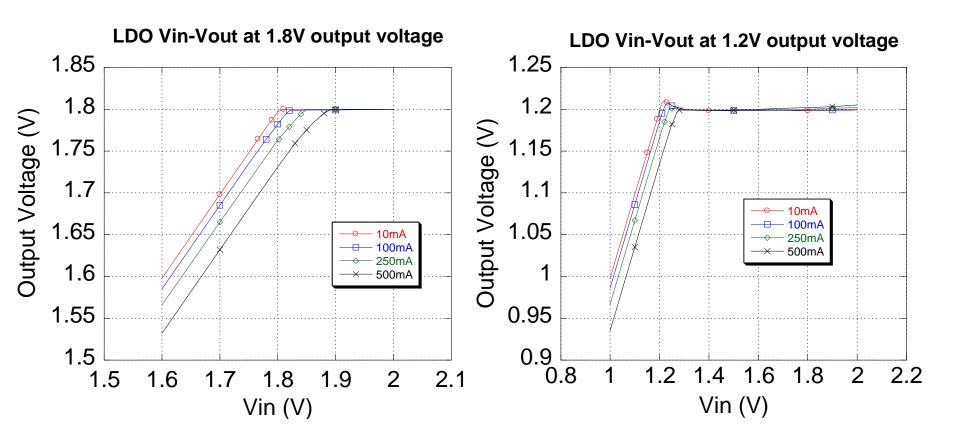

### Summary of Measurements

- High current drive > 3A

- Low on resistance,  $R_{on} < 10 \text{ m}\Omega \cdot \text{mm}^2$

- Low dropout voltage  $V_{DO}$ < 170mV for a 1A load

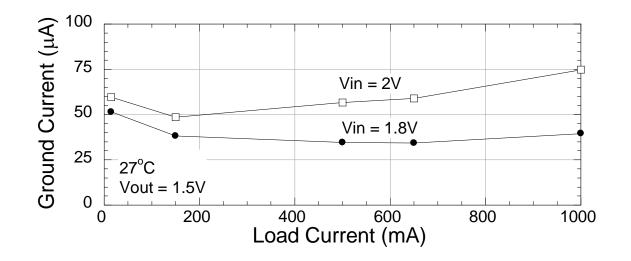

- Low quiescent current,  $I_Q < 75 \mu A$

## MESFET Linear Regulator (cont.)

## Line Regulation

SJT Micropower

W. Lepkowski, et al., "An integrated MESFET voltage follower LDO for high power and PSR RF and analog applications," *Custom Integrated Circuits Conference (CICC), 2012 IEEE*, vol., no., pp.1-4, 9-12 Sept. 2012

Contact: info@sjtmicropower.com

### Quiescent current

W. Lepkowski, et al., "An integrated MESFET voltage follower LDO for high power and PSR RF and analog applications," *Custom Integrated Circuits Conference (CICC), 2012 IEEE*, vol., no., pp.1-4, 9-12 Sept. 2012

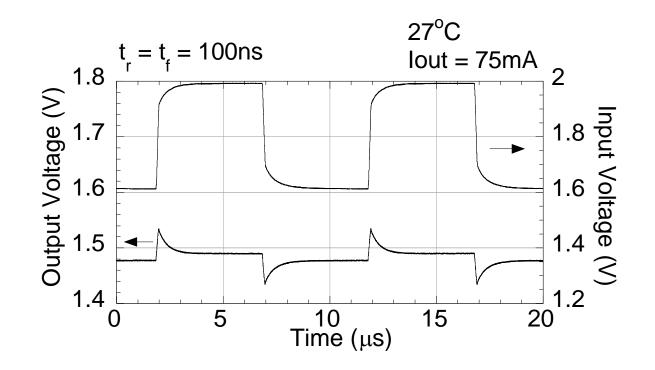

# MESFET LDO: Transient Line Regulation

- Vout settles in ~2µs w/ single overshoot and undershoot

- Suggests high level of phase margin

Micropower

• No output cap other than 12pF parasitic cap from scope probe

W. Lepkowski, et al., "An integrated MESFET voltage follower LDO for high power and PSR RF and analog applications," *Custom Integrated Circuits Conference (CICC), 2012 IEEE*, vol., no., pp.1-4, 9-12 Sept. 2012 *Contact: info@sjtmicropower.com*

# MESFET LDO: PSR

- PSR measurement includes integrated BGR

- > 40dB performance at 80mA load.

- Expect PSR to be higher at increased load currents due to higher simulated open loop gain

W. Lepkowski, et al., "An integrated MESFET voltage follower LDO for high power and PSR RF

SJT\_Micropower

W. Lepkowski, et al., "An integrated MESFET voltage follower LDO for high power and PSR RF and analog applications," *Custom Integrated Circuits Conference (CICC), 2012 IEEE*, vol., no., pp.1-4, 9-12 Sept. 2012

SJT Micropower and the SBIR program

Outline

- Silicon MESFET Overview

- High Voltage Capability

- Modeling and Measured MESFETs

- Power Applications

- RF Applications

46

### PA Integration

# CMOS technology is drawing more attention for handset applications:

Low cost solutions

High integration with digital circuits

Single chip transceiver solutions

Easy to redesign after technology scaling

Good modeling of silicon based components

### But ... It has power limitations

## SJT\_Micropower

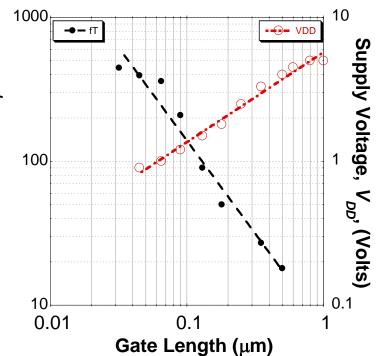

Standard CMOS scaling trend (Data collected from different sources)

47

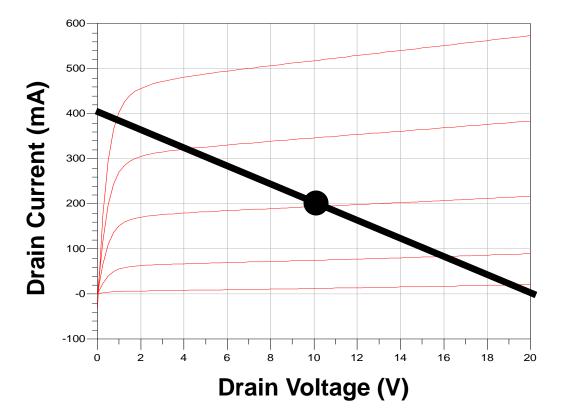

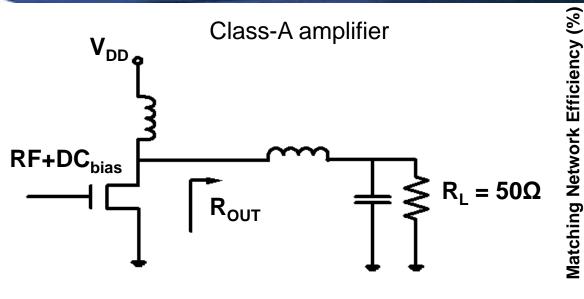

## Simple Class A Amplifier Design

- $P_{out} Class A = \frac{1}{2} i_{dc} V_{dc} = \frac{1}{2} 0.2A 10V = 1W, R_{load} = V_{dc}/i_{dc} = 50\Omega$

- Note that if Vd of the transistor goes down, current must go up and R<sub>load</sub> goes down

- For 1W if  $V_{dc}$  = 1V,  $i_{dc}$  = 2A and  $R_{load}$  = 0.5  $\Omega$

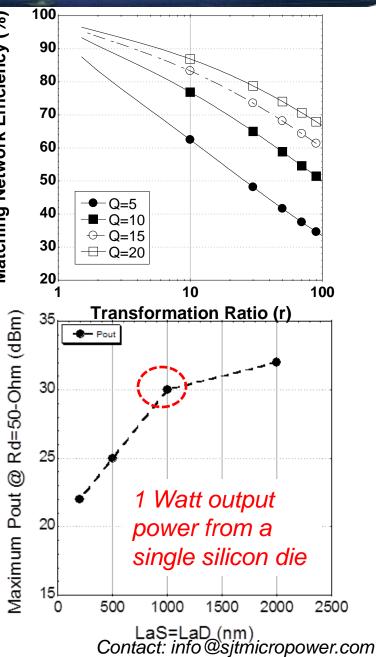

### PA Efficiency Reduced by Large Impedance Transformations<sup>49</sup>

- CMOS PAs may need to use large transformation ratios, r = R<sub>L</sub>/R<sub>OUT</sub> > 10

- A MESFET PA with  $P_{out} > 1W$  can be designed to have  $R_{OUT} \sim 50 \Omega$

SJT Micropower

**Overcoming Low Voltage Design Constraints**

There are several techniques to overcome VBD issue in CMOS technology:

- Cascode architecture (less than ~2 times improvement)

- Thick oxide transistors (~factor of 2 improvement)

- Parallel amplification (lowers the PAE)

- High voltage devices such as BiCMOS (cost, not always available on digital processes)

### **Proposed SOI-MESFET**

- ~2-to-10 times improvement in VBD

- No additional cost

- Available on any SOI digital process

- High enough cut-off frequency for PA design at f0<5GHz

# MESFET Breakdown Voltage and Cutoff Frequency <sup>51</sup>

- There is a tradeoff between  $V_{BD}$  and  $f_T$

- Optimum device geometries found to be

- $L_{aD}=L_{aS}=500$  nm,  $L_{aS}=200$  nm =>>  $f_T=24$  GHz,  $V_{BD}=15$  V

- $L_{aD} = L_{aS} = 2000$  nm,  $L_g = 200$  nm =>>  $f_T = 9$  GHz,  $V_{BD} = 28$  V

|                          |          | LaS=LaD= |          |

|--------------------------|----------|----------|----------|

| Parameter                | LAS=LAD= | 1000nm   | LaS=LaD= |

| i di di lictor           | 500nm    |          | 2000nm   |

|                          |          |          |          |

| Gate oxide               | No Gate  | No Gate  | No Gate  |

|                          | Oxide    | Oxide    | Oxide    |

| $L_G(nm)$                | 200      | 200      | 200      |

| $L_{ext}/L_{Spacer}(nm)$ | 500      | 1000     | 2000     |

|                          |          |          |          |

| $W_{finger}(\mu m)$      | 15       | 15       | 15       |

| $V_{BD}(V)$              | 15       | 21       | 28       |

| $f_T$ (GHz)              | 24       | 17.5     | 9        |

| $f_{MAX}(\text{GHz})$    | 35       | 25       | 20       |

| $V_{T}(V)$               | -0.5     | -0.5     | -0.5     |

|                          |          |          |          |

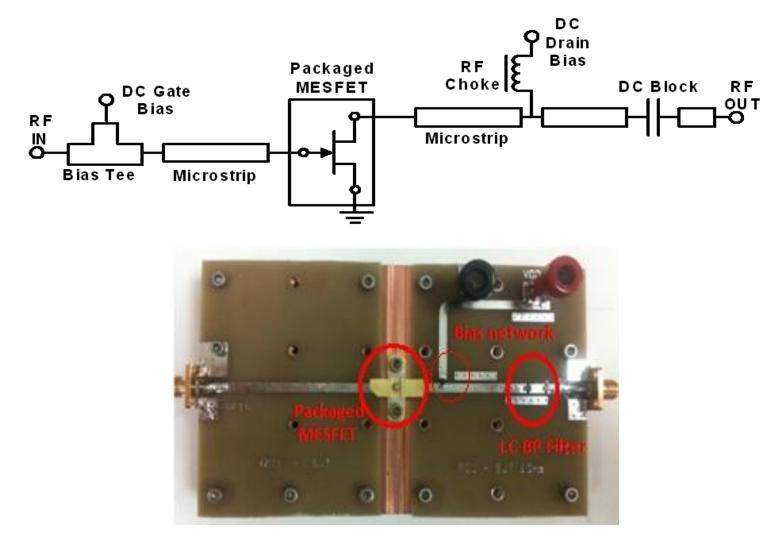

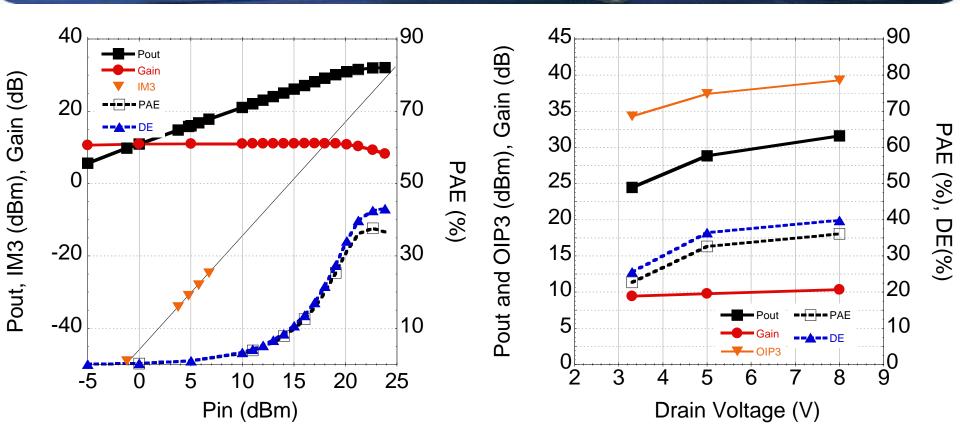

## **MESFET 433MHz PA Demonstration**

### **Simplified Circuit and Board Design**

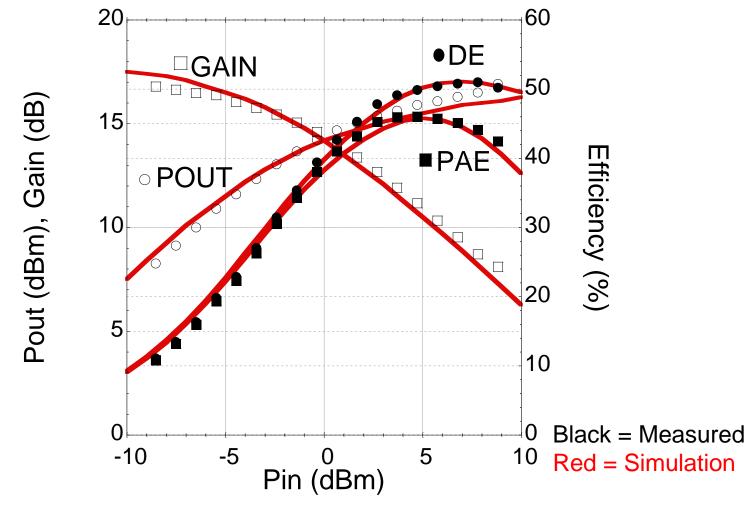

## MESFET 433MHz PA Demonstration – Cont.

• Gain of 16.8dB

- Peak PAE 46% at Pout of 15.9dBm

- Peak Pout of 17dBm with PAE of 42.5%

SJT\_Micropower

Contact: info@sjtmicropower.com

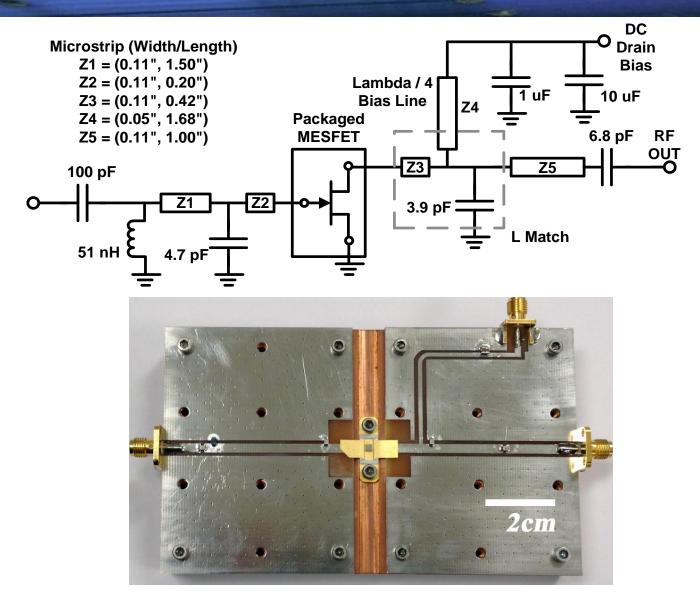

### **MESFET 900MHz PA Demonstration**

S. J. Wilk, W. Lepkowski and T. J. Thornton, "32 dBm Power Amplifier on 45 nm SOI CMOS," IEEE Microwave and Wireless Components Letters, Accepted for publication Jan 2013.

## MESFET 900MHz PA Demonstration – 1.5W

• Gain of 11.1dB

SJT\_Micropower

Peak Pout of 32dBm

Peak PAE 37.6%OIP3 of 39.3dBm

S. J. Wilk, W. Lepkowski and T. J. Thornton, "32 dBm Power Amplifier on 45 nm SOI CMOS," IEEE Microwave and Wireless Components Letters, Accepted for publication Jan 2013.

Contact: info@sjtmicropower.com

# Ongoing Research and Development Efforts

- Higher Frequency PA Measurements Working on >2GHz and 1W PA designs along with Polar Modulation

- Development of integrated low dropout linear regulators for defense applications (supported by NASA and DARPA Phase 2 SBIR projects)

- Continued development of MESFETs on 45nm and 32nm process nodes

- Continued statistical analysis of MESFET devices and model development.

S. J. Wilk, W. Lepkowski and T. J. Thornton, "32 dBm Power Amplifier on 45 nm SOI CMOS," *IEEE Microwave and Wireless Components Letters,* Accepted for publication Jan 2013.

M.R.Ghajar, S. J. Wilk, W. Lepkowski, B. Bakkaloglu and T. J. Thornton "Backgate Modulation Technique for Higher Efficiency Envelope Tracking" *IEEE Transactions on Microwave Theory and Techniques, accepted for publication* Jan 2013.

W. Lepkowski, S. J. Wilk, M.R.Ghajar, T. J. Thornton, "High Voltage SOI MESFETs at the 45nm Technology Node," *IEEE International SOI Conference, 2012*, October 2012

W. Lepkowski, Wilk, S.J. Ghajar, M.R.; Bakkaloglu, B., Thornton, T.J., "An integrated MESFET voltage follower LDO for high power and PSR RF and analog applications," *Custom Integrated Circuits Conference (CICC), 2012 IEEE*, vol., no., pp.1-4, 9-12 Sept. 2012

S. J. Wilk *et al.*, "Characterization and modeling of enhanced voltage RF MESFETs on 45nm CMOS for RF applications," *IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2012*, pp.413-416, 17-19 June 2012.

Lepkowski, W., Ghajar, M.R., Wilk, S.J., Summers, N., Thornton, T.J., Fechner, P.S., , "Scaling SOI MESFETs to 150-nm CMOS Technologies," *Electron Devices, IEEE Transactions on*, vol.58, no.6, pp.1628-1634, June 2011

Lepkowski, W., Goryll, M., Wilk, S.J., Zhang, Y., Sochacki, J., Thornton, T.J., , "SOI MESFETs for extreme environment buck regulators," *SOI Conference (SOI), 2011 IEEE International*, vol., no., pp.1-2, 3-6 Oct. 2011

J. Ervin, A. Balijepalli, P.J. Joshi, V. Kushner, J. Yang, T.J. Thornton, "CMOS-Compatible SOI MESFETs with High Breakdown Voltage," IEEE Trans. Elec. Dev., vol. 53, p. 3129, 2006.

# **QUESTIONS?**

**Contact Information:**

Seth Wilk Phone: 602-703-3730 swilk@sjtmicropower.com

http://sjtmicropower.com/