# Bridging Design and Manufacture of Analog/Mixed-Signal (AMS) Circuits in Advanced CMOS

Alvin Loke, Ray Stephany, Dennis Fischette, Tin Tin Wee, John Faricelli, Hoang Dao, Larry Bair, Jim Buller, Dru Cabler, Bruce Doyle, Shawn Searles, Emerson Fang Advanced Micro Devices

Jia Feng, Joanne Wu, Jung-Suk Goo, Christoph Schwan, Xin Li GLOBALFOUNDRIES

Joddy Wang, Dehuang Wu, Song Zhou, Weidong Liu Synopsys

July 6, 2012

**AUTHORIZATION**

All copyrights to the material contained in this document are retained by me or by my employer.

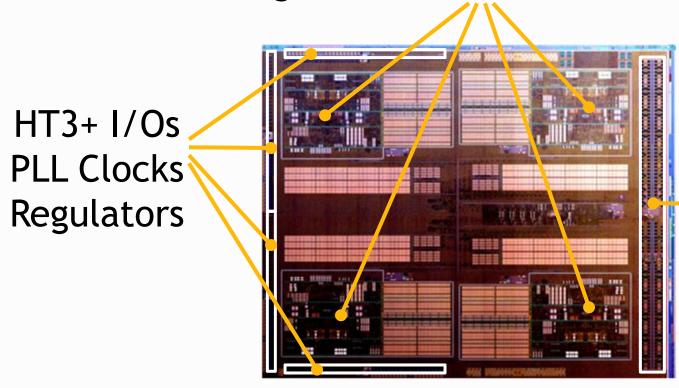

#### AMS is Essential in Processors

Core PLL Clocks (voltage/frequency islands)

Regulators & Thermal Sensors

DDR3 I/O PLL Clock

32nm SOI-CMOS "Orochi" server processor with Bulldozer cores

Fischer et al., Ref. [1]

#### **Outline**

- Background & Motivation

- Device-Level Characterization

- Circuit-Level Characterization

- Circuit Simulator Developments

- Conclusions

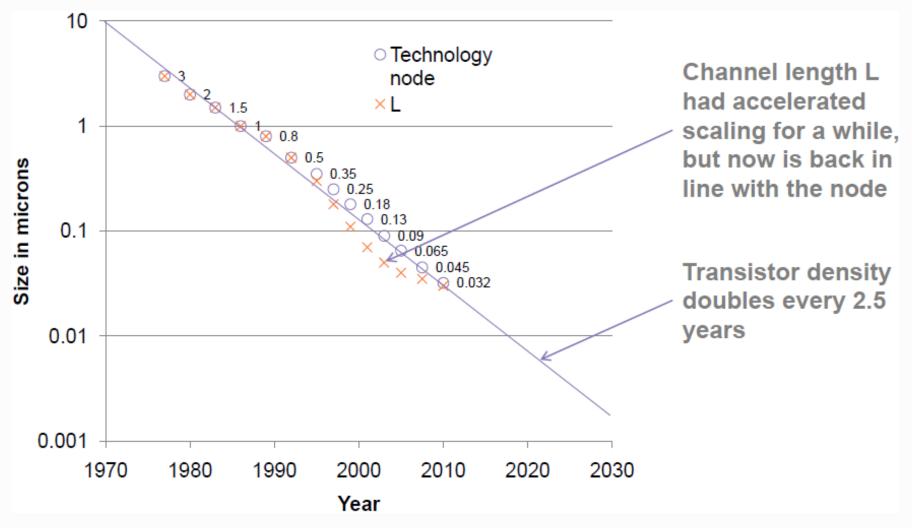

## **CMOS Scaling Driven by Logic Needs**

Keating, Ref. [2]

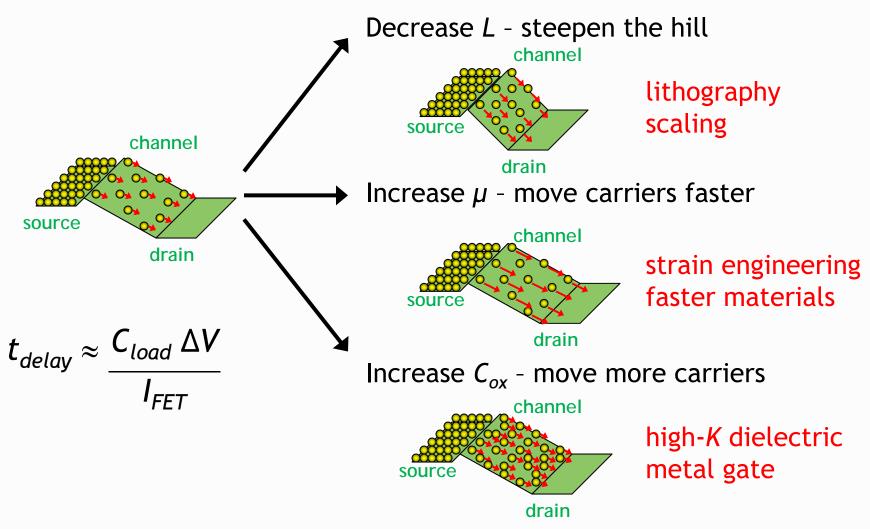

## The Roads to Higher Performance

• Doing it all without parasitic R & C undoing all the  $I_{FET}$  gains

## **AMS Design Realities**

- Difficult to co-optimize process for both AMS and logic and stay cost-effective

- So we generally have to live with what we get

- Voltage headroom ↓

- FETs: gain  $\downarrow$ , output resistance  $\downarrow$ , variation  $\uparrow$ , leakage  $\uparrow$

- Passives: as cheap as possible, choices  $\downarrow$ , less ideal

- Layout proximity effects ↑

- − Circuit options ↓

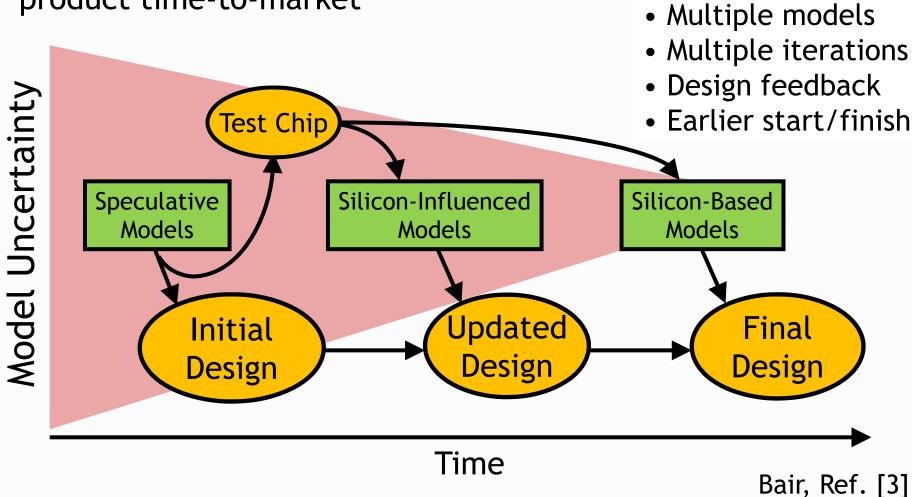

## Bleeding-Edge Processor Development

• Design concurrently developed with technology to shorten product time-to-market

#### Let The Truth Be Told About Our Models

- Speculative and inherently uncertain

- Historically tailored to logic, not analog or passives

- Go digital if it makes sense (complexity, power, area, etc.)... fab will take better care of you, easier to port to next node

- Limited to fab understanding of design usage

- Intrinsically late to capture new effects

- e.g., STI stress, well implant proximity, stress proximities

- Understand their limitations

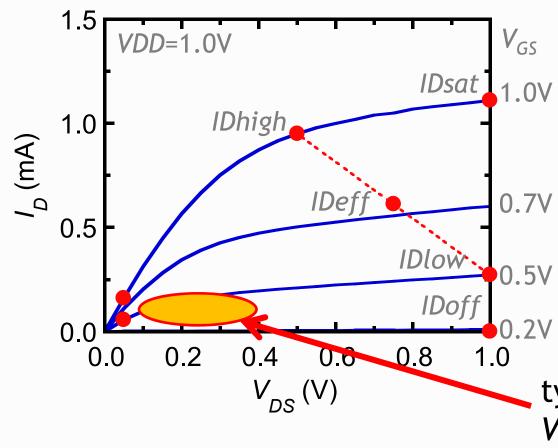

## Analog vs. Digital Regions of Operation

IDeff is better metric than Idsat for effective inverter current in CV/I

Na et al., Ref. [4]

typical analog biasing  $V_{GS}=V_T$  to  $V_T+0.2V$

• Analog design needs accurate modeling of slopes  $(g_m, g_{ds}, \text{ etc.})$  as well as points (*IDsat*, *IDoff*, etc.)

#### Don't Overlook the Circuit Simulator

- HSPICE calculates FET parameters (terminal currents & voltages, transconductances, capacitances, etc.) and reports them in output templates

- Parameters (as basic as  $V_T$ ) may not be measured the same way on silicon

- We'll cover examples of simulator limitations and co-development to overcome them

#### **Outline**

- Background & Motivation

- Device-Level Characterization

- MOSFETs

- Current-Based  $g_m$ ,  $g_{ds}$  &  $g_{mb}$

- Drain saturation margin

- Passives

- Circuit-Level Characterization

- Circuit Simulator Developments

- Conclusions

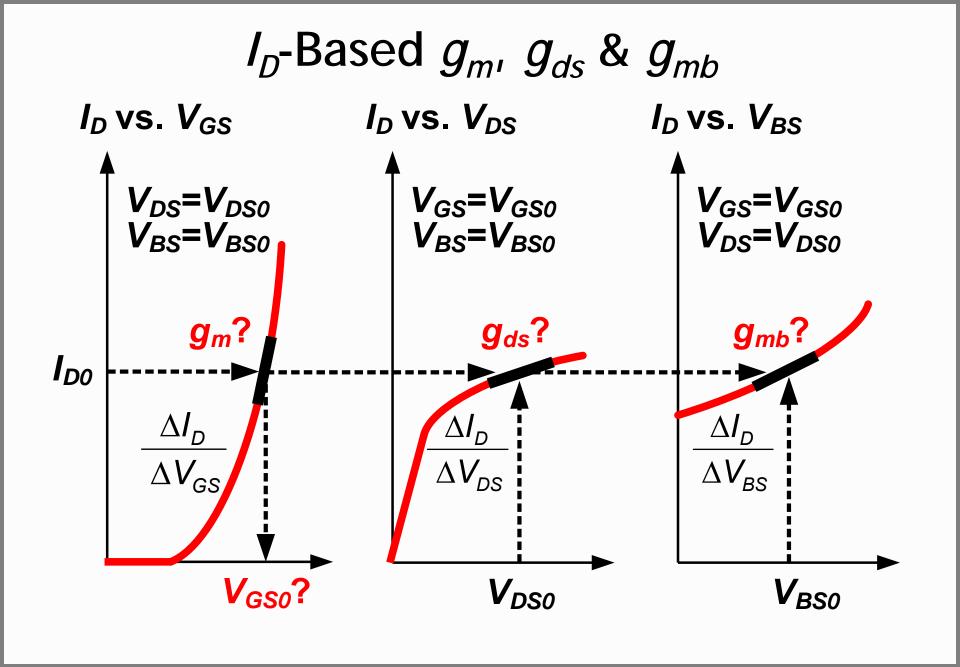

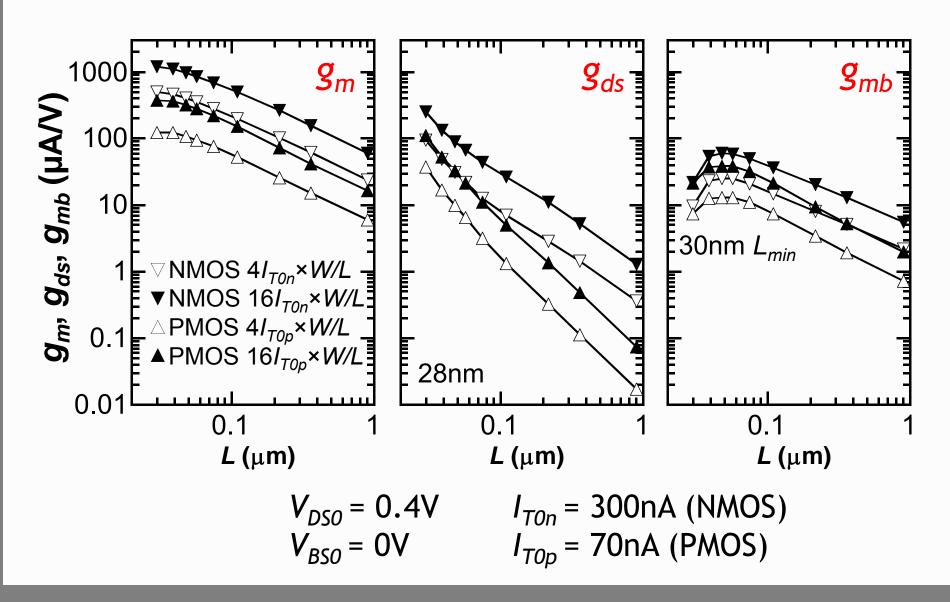

## **Analog Usage of MOSFETs**

- Transconductor in saturation, want  $I_{DS}=f(\text{only }V_{GS})$

- Fab measures  $g_m$ ,  $g_{ds}$  &  $g_{mb}$  at  $V_{GS} = V_T + V_{ON}$  or VDD

- Scaled supply  $\rightarrow V_{ON} \& V_{DS} V_{DSsat}$  as low as 50mV

- Constant-current  $V_{\tau}$  definition somewhat arbitrary

- Simulated  $V_T$  criterion  $\neq$  Fab  $V_T$  criterion

- Cumbersome to correlate simulation to silicon

- Analog circuits typically biased by  $I_{REF}$

- Examine  $g_m$ ,  $g_{ds}$  &  $g_{mb}$  at realistic min/max  $I_{DS}$  usage

## $I_D$ -Based $g_{m'}$ $g_{ds}$ & $g_{mb}$ Example

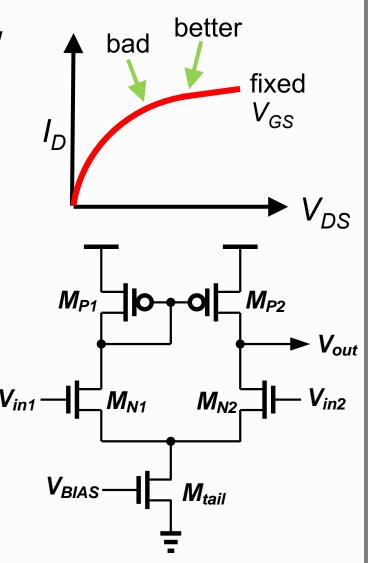

## **Saturation Margin**

- Analog folks adamant about biasing FETs safely in saturation, i.e., device stays in "pinch-off"

- Need for saturation margin

- Signal swing (sometimes with gain)

- Modeling errors

- Supply droop

- Saturation margin usually  $V_{DS} V_{DSsat}$

- $V_{DSsat}$  depends on model & is difficult to measure

- Tough to have ample margin with decreasing VDD

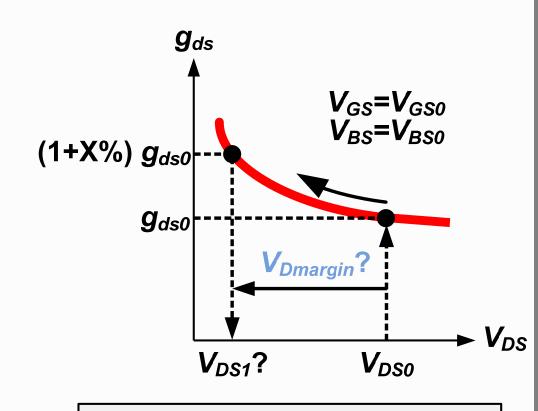

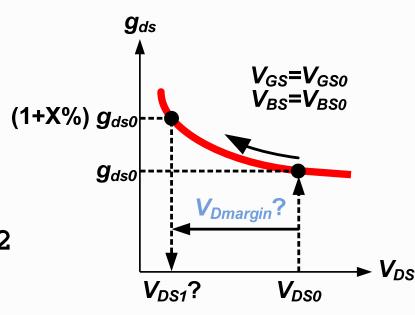

# Introducing $V_{Dmargin}$

- Find  $V_{DS}$  margin available before  $g_{ds} \uparrow$  by X%

- V<sub>Dmargin</sub> can be simulated

& measured uniquely

- $V_{Dmargin}$  is much smaller in linear vs. saturation region

$$V_{Dmargin} = V_{DS0} - V_{DS1}$$

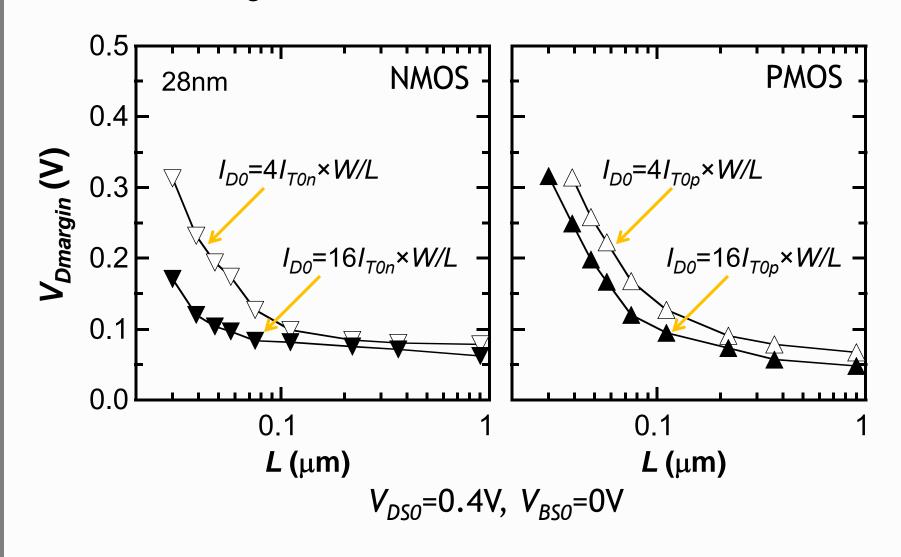

# $V_{Dmargin}$ Example for $\Delta g_{ds}$ =+20%

#### **Outline**

- Background & Motivation

- Device-Level Characterization

- MOSFETs

- Passives

- Across-Chip Variation of Poly Resistor

- Series Resistance of Accumulation-Mode Varactor

- Diode Ideality

- Circuit-Level Characterization

- Circuit Simulator Developments

- Conclusions

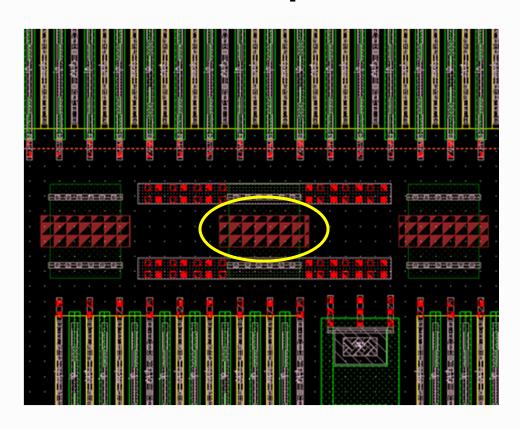

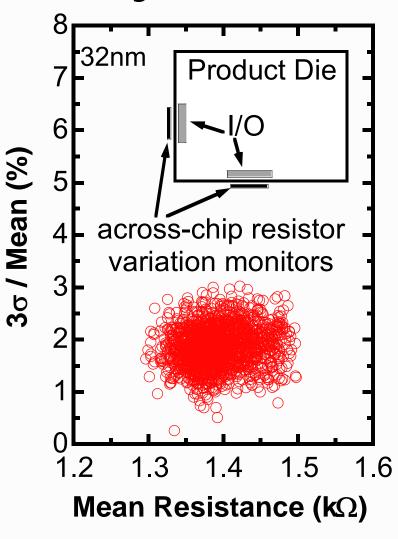

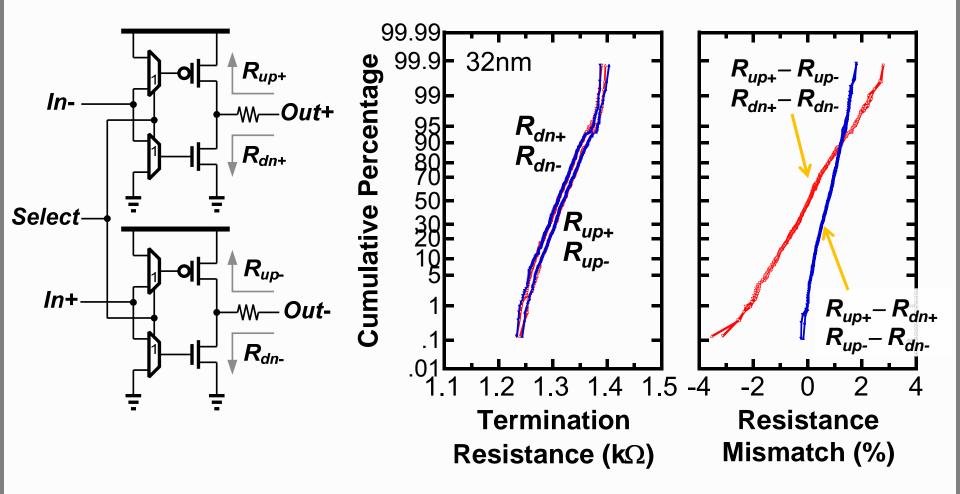

## Calibration of Poly Resistance Variation

## Across-Chip Variation of Poly Resistor

Scribe lane monitor has array of cropped I/O receiver layout to minimize scribe-to-die bias

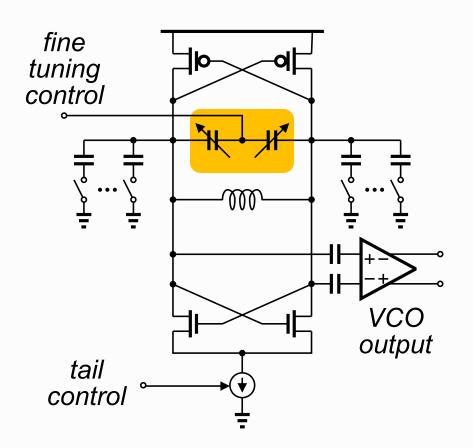

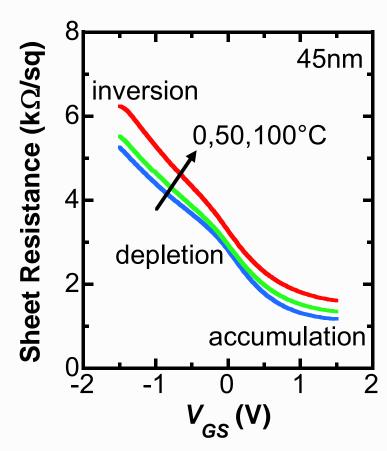

#### Series Resistance of Varactor n-Well

- n-type accumulation DECAP built for VDD noise reduction

- Need accurate Q modeling for LC-VCO application

Fischette et al., Ref. [5]

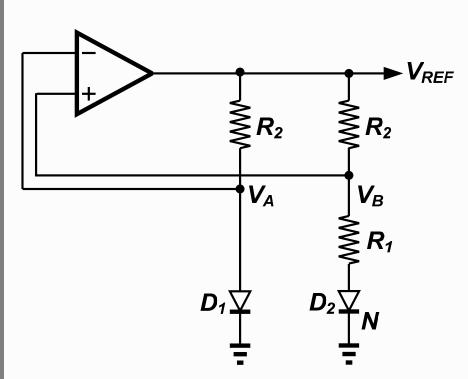

## Bandgap Voltage Reference

$$V_{REF} = V_{D_1} + I_{R_1}R_2 = V_{D_1} + \frac{\Delta V_D}{R_1}R_2$$

$$= V_{D_1} + \frac{\frac{\eta kT}{q}\ln\left(\frac{I_{R_2}}{I_S}\right) - \frac{\eta kT}{q}\ln\left(\frac{I_{R_2}}{NI_S}\right)}{R_1}R_2$$

$$= V_{D_1} + \frac{R_2}{R_1}\frac{\eta kT}{q}\ln N \approx 1.2V$$

$$CTAT + PTAT \rightarrow zero tempco$$

- PTAT+CTAT using voltage

- · Resistors determine weighted voltage summing

- Applications: absolute voltage references, references for regulators delivering quieter power

Razavi, Ref. [6]

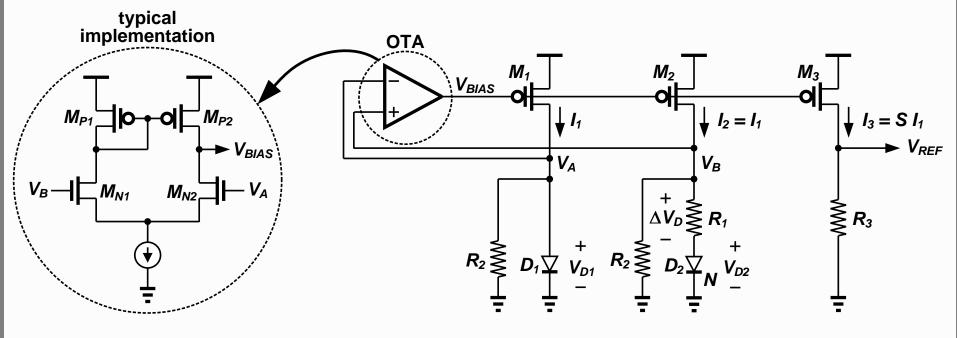

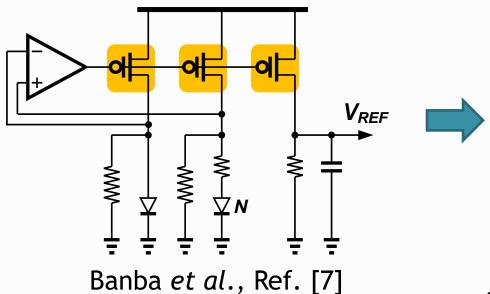

## Low-Voltage Bandgap Reference

$$V_{REF} = SI_{1}R_{3} = S\left(\frac{V_{D_{1}}}{R_{2}} + \frac{\Delta V_{D}}{R_{1}}\right)R_{3} = S\left(\frac{V_{D_{1}}}{R_{2}} + \frac{\frac{\eta kT}{q}\ln N}{R_{1}}\right)R_{3} = \frac{SR_{3}}{R_{2}}V_{D_{1}} + \frac{SR_{3}}{R_{1}}\frac{\eta kT}{q}\ln N$$

$$CTAT PTAT$$

- PTAT+CTAT using current

- Resistors determine weighted summing

Banba et al., Ref. [7]

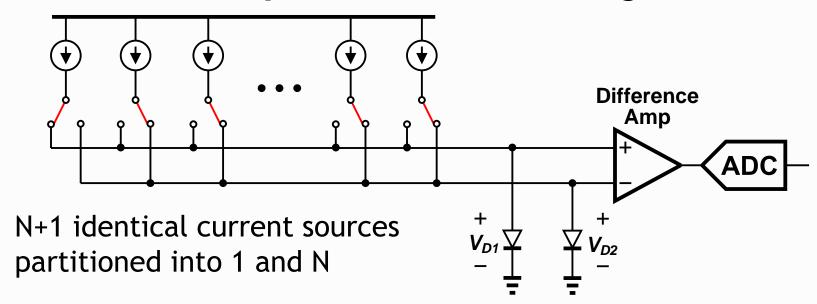

## **Temperature Sensing**

- Sense PTAT  $\Delta V_D$  between identical diodes with ratio'ed currents

- Average/integrate with Dynamic Element Matching (DEM) to eliminate impact of current source mismatches

- Swap inputs to difference amp to average out offset

$$\Delta V_D = V_{D1} - V_{D2} = \frac{\eta kT}{q} \ln \left( \frac{NI_D}{I_S} \right) - \frac{\eta kT}{q} \ln \left( \frac{I_D}{I_S} \right) = \frac{\eta kT}{q} \ln N$$

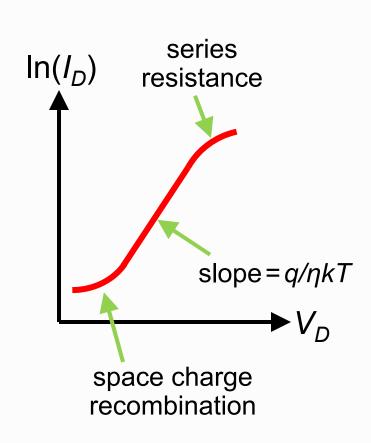

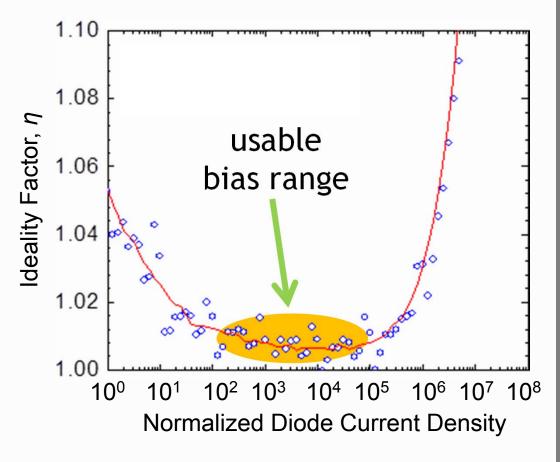

## **Diode Ideality**

- Need to operate at constant  $\eta$  for accurate  $\Delta V_D$  computation

- Factor some margin to cover PVT variation

- Monitor  $\eta$  at forward-bias current range of interest

#### **Outline**

- Background & Motivation

- Device-Level Characterization

- Circuit-Level Characterization

- Voltage-Starved Ring Oscillators

- Transmitter Differential Output Driver

- Pseudo-Bandgap Voltage Reference

- Circuit Simulator Developments

- Conclusions

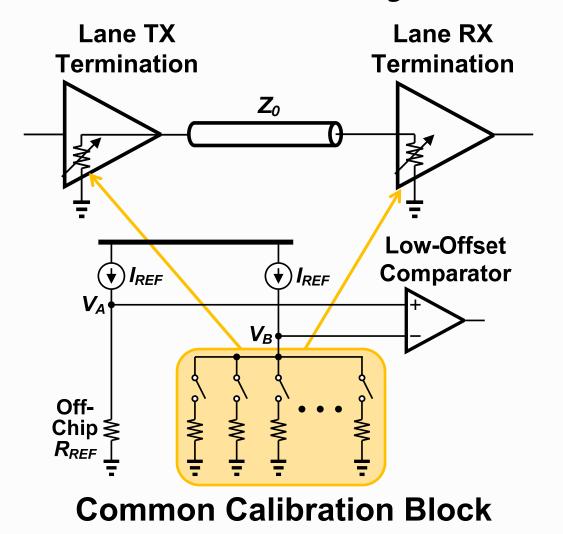

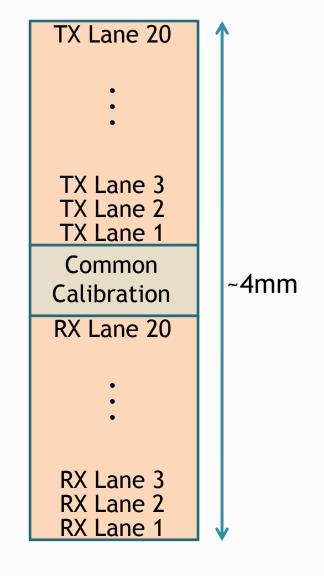

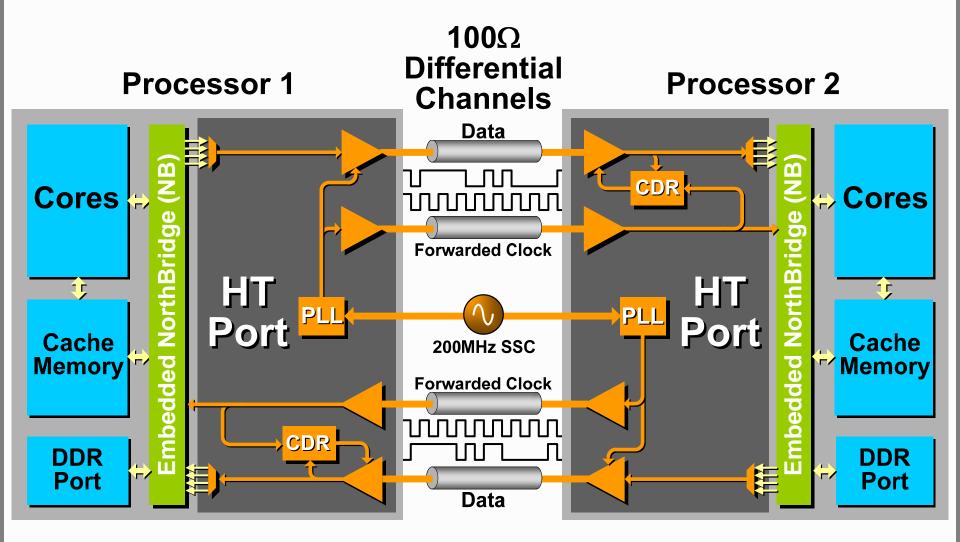

## HyperTransport™ Die-to-Die Link

Loke et al., Ref. [8]

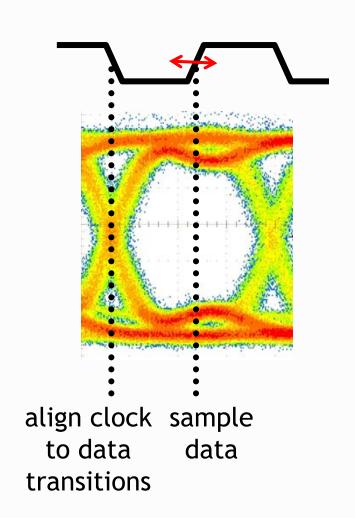

## **DLL for Data Recovery**

- Need ability to adjust clock phase for optimum sampling of data

- Generate phases spaced by 30° for subsequent phase interpolation to achieve finer phase resolution

- Use cascade of variable delay stages to generate required phases

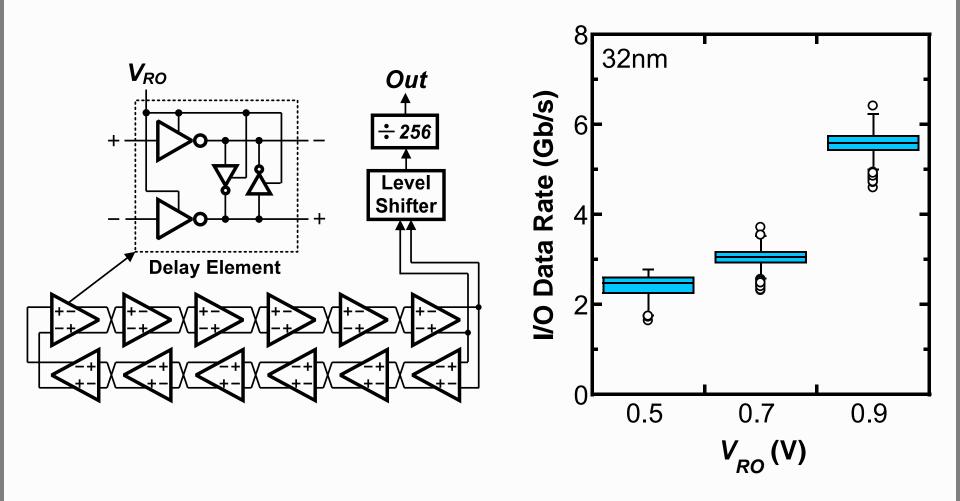

## Voltage-Starved Ring Oscillator

Monitor FET digital behavior at low VDD (0.5-0.7V)

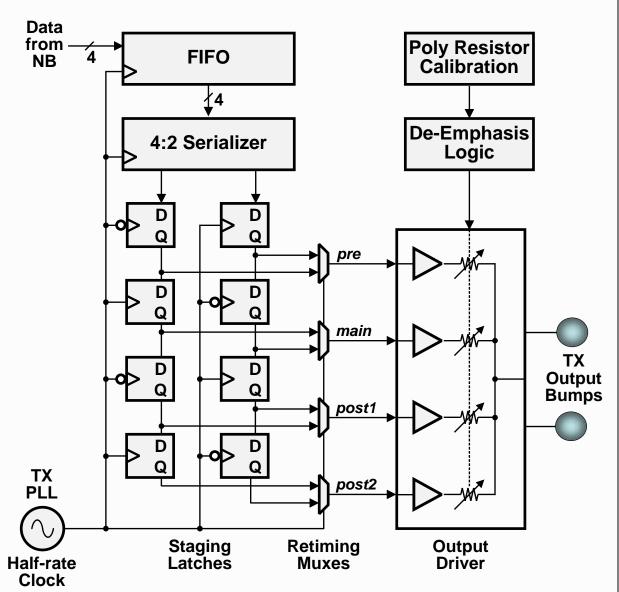

#### **HT Transmitter Architecture**

- 4-tap FIR filter to equalize channel losses

- Tunable driver output resistance to match channel Z<sub>0</sub> for minimal reflection

## Transmitter Differential Output Driver

• Monitor FET  $R_{linear}$ , resistors,  $\beta$  ratio, mismatch

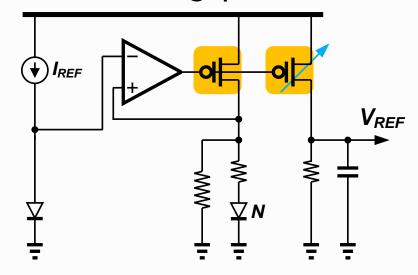

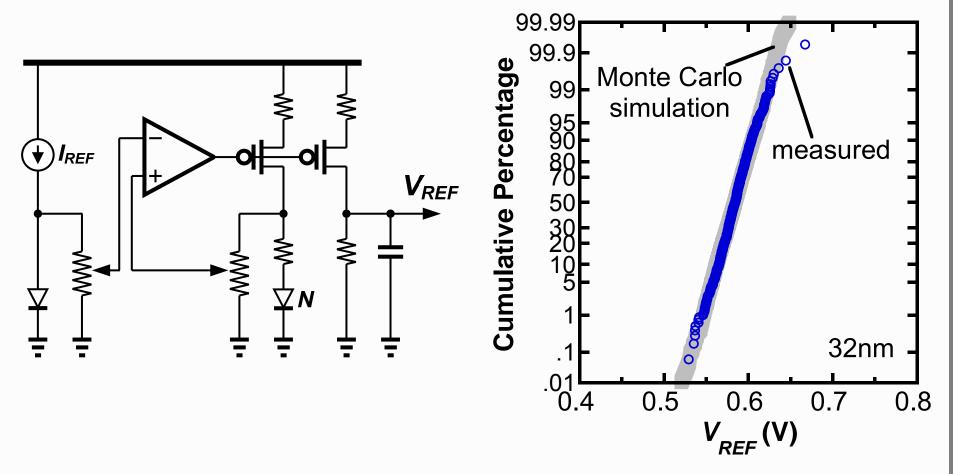

## Pseudo-Bandgap Voltage Reference

Classic Low-Supply Bandgap Reference

- PTAT+CTAT with current

- Prone to PMOS mismatch

Low-Supply Pseudo-Bandgap Reference

- Less PMOS mismatch

- More systematic PVT variation which can be removed by calibration

## Pseudo-Bandgap Measurements

Monitor long-L FETs, diodes, resistors, mismatch

#### **Outline**

- Background & Motivation

- Device-Level Characterization

- Circuit-Level Characterization

- Circuit Simulator Developments

- $-V_{\tau}$  Measurement

- V<sub>Dmargin</sub> Measurement

- Macromodel Output Templates

- Conclusions

## Revisiting the Most Basic of Basics

## BSIM4.6.2 $V_T$ Equation - The Band-Aids

$$\begin{split} &V_{T} = VTH0 + \left(K_{1ox} \cdot \sqrt{\Phi_{s} - V_{BSeff}} - K1 \cdot \sqrt{\Phi_{s}}\right) \sqrt{1 + \frac{LPEB}{L_{eff}}} - K_{2ox}V_{BSeff} \\ &+ K_{1ox} \left(\sqrt{1 + \frac{LPEB}{L_{eff}}} - 1\right) \sqrt{\Phi_{s}} + \left(K3 + K3B \cdot V_{BSeff}\right) \frac{TOXE}{W_{eff}' + W0} \Phi_{s} \\ &- \left[\frac{DVT0W}{\cosh\left(DVT1W\frac{L_{eff}W_{eff}'}{I_{tw}}\right) - 1} + \frac{DVT0W}{\cosh\left(DVT1\frac{L_{eff}W_{eff}'}{I_{t}}\right) - 1}\right] \frac{V_{bi} - \Phi_{s}}{2} \\ &- \frac{ETA0 + ETAB \cdot V_{BSeff}}{\cosh\left(DSUB\frac{L_{eff}}{I_{to}}\right) - 1} \frac{V_{DS}}{2} - n \frac{k_{B}T}{q} \ln \left\{\frac{L_{eff}}{L_{eff} + DVTP0[1 + \exp(-DVTP1 \cdot V_{DS})]}\right\} \end{split}$$

Reported in Lv9 output template

Yang *et al.*, Ref. [9]

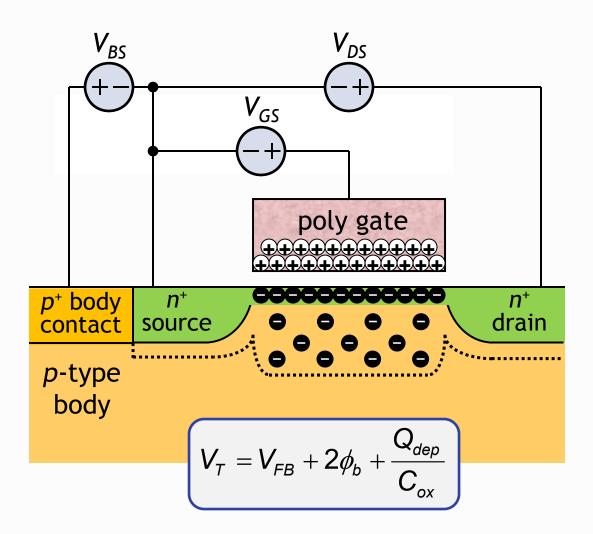

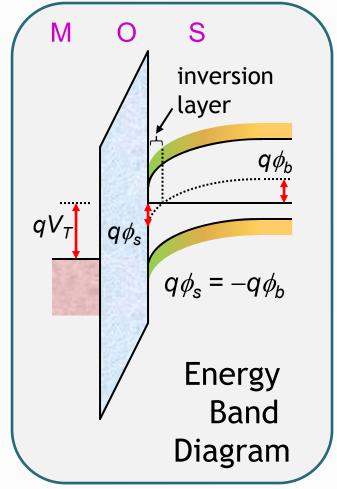

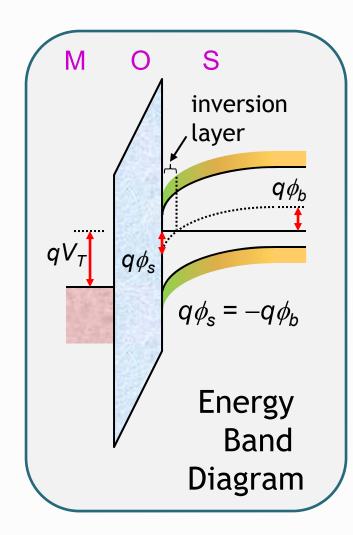

## Please... Physics NOT Math

- Based on "fundamental" strong inversion criterion

- Extended to behaviorally model

- Body effect ( $V_{BS}$  < 0 in NMOS,  $V_{BS}$  > 0 in PMOS)

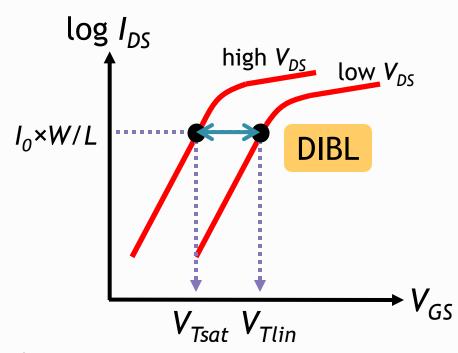

- Short-channel effect including DIBL

- Narrow-width effect

- Non-uniform lateral doping halo implants

- Non-uniform vertical doping retrograded well

- LOD effect from STI compressive stress

- Well proximity effect from implant mask scattering

- Model late to include new silicon  $V_{\tau}$  dependencies

- Impossible to measure in silicon

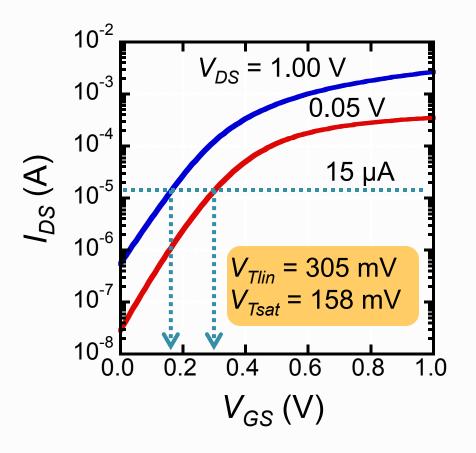

## Fab Measurement - Constant-Current $V_T$

- Sweep log  $I_{DS}$  vs.  $V_{GS}$  at fixed  $V_{BS}$

- Choose  $V_{DS}$  depending on region of operation

- Find  $V_{GS}$  when  $I_{DS}$  crosses user-specified threshold  $I_0$  normalized to W/L

- Typical I<sub>0</sub> ~ 10 to 500 nA

- No physical connection to onset of strong inversion

- Be careful when you compare  $V_T$  across foundries  $\rightarrow$  know their  $I_0$

$$V_T = V_{GS} \Big|_{I_{DS} = I_0 imes rac{W_{drawn}}{L_{drawn}}}$$

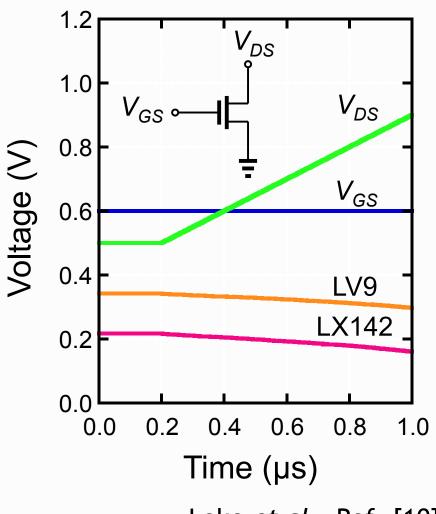

## Simulating What The Fab Measures

- .OPTION IVTH=val | IVTHN=val1 | IVTHP=val2

- Freeze FET node voltages at given instant

- Determine  $V_{GS}$  for  $I_{DS} = I_0 \times W_{drawn} / L_{drawn}$

- Report extracted  $V_T$  in Lx142 output template

- $V_{DS}$  limited to **VDSMIN** (50mV default)

- Feature available since HSPICE-2009.09

$$V_{GS} = ?$$

for  $I_{DS} = IVTHN \times W/L$

## LX142 Example

Loke *et al.*, Ref. [10]

#### Not So Fundamental After All

$$oxed{V_{\mathcal{T}} = V_{\mathcal{FB}} + 2\phi_b + rac{\mathsf{Q}_{dep}}{C_{ox}}}$$

- Body doping levels have increased by 2-3 orders of magnitude over the decades

- Surface charge density way more conductive at strong inversion condition based on "fundamental"  $V_T$  definition

- Best to treat  $V_T$  as just a reference point

- I<sub>OFF</sub> vs. I<sub>ON</sub> plots have become universally more important for reporting device characteristics

# V<sub>Dmargin</sub> in HSPICE

- Feature recently implemented in HSPICE-2012.06

- LX286 output template

- Usage example

- .IVDMARGIN M3 DELTAGDS=0.2

- .PRINT DC VDMARGIN(M3)

$$V_{Dmargin} = V_{DS0} - V_{DS1}$$

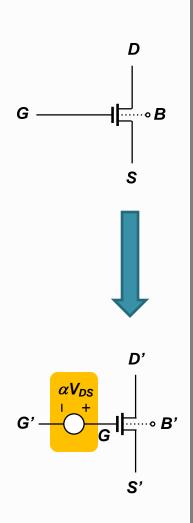

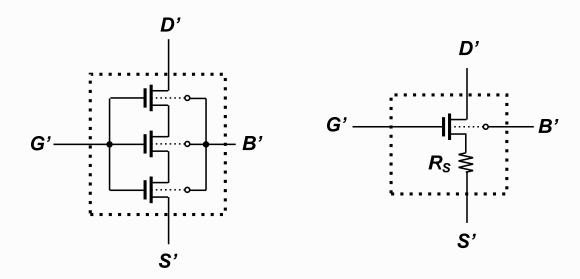

## Macromodel Output Templates

- Models late to capture new silicon observation

- Meanwhile, foundries build subckt wrappers around intrinsic models

- Output templates report device characteristics of intrinsic model BUT what really matters are characteristics of the subckt

- Example

- $V_{DS}$ -controlled voltage source in series with gate to degrade  $V_T$  and  $g_{ds}$  for better correlation to observed silicon at process corners

- "DIBL wrapper" took over a year to implement into BSIM4.7

- Co-development with Synopsys R&D in progress to provide subckt output templates

## **Extending Macromodel Concept**

- Scaling of conventional planar devices continues to constrain analog design, e.g., poor  $g_{ds}$

- Stronger halo implants for short-channel control

- Stricter  $L_{max}$  from replacement-gate HKMG integration

- More frequent usage of source degeneration to reduce  $g_{ds}$

Really interested in output template of composite device

#### Conclusion

- Scaling will continue to be more restrictive on AMS

- Co-development improves model quality and fab monitoring of device behavior for AMS designs

- Pay attention to details, don't overlook CAD

#### References

- [1] H. McIntyre *et al.*, "Design of the two-core x86-64 AMD "Bulldozer" module in 32 nm SOI CMOS," *IEEE J. Solid-State Circuits*, vol. 47, no. 1, Jan. 2012, pp. 164-176.

- [2] M. Keating, "Science fiction or technology roadmap: a look at the future of SoC design," in SNUG San Jose Conf., Mar. 2010.

- [3] L. Bair, "Process/product interactions in a concurrent design environment," in *Proc. IEEE CICC*, pp. 779–782, Sep. 2007.

- [4] M. Na et al., "The effective drive current in CMOS inverters," in IEEE IEDM Tech. Dig., pp. 121-124, Dec. 2002.

- [5] D. Fischette *et al.*, "A 45nm SOI-CMOS dual-PLL processor clock system for multi-protocol I/O," in *IEEE ISSCC Tech. Dig.*, pp. 246–247, Feb. 2010.

- [6] B. Razavi, Design of Analog CMOS Integrated Circuits, McGraw-Hill, 2001.

- [7] H. Banba *et al.*, "A CMOS bandgap reference circuit with sub-1-V operation," *IEEE J. Solid-State Circuits*, vol. 34, no. 5, pp. 670-674, May 1999.

- [8] A. Loke *et al.*, "An 8.0-Gb/s HyperTransport™ transceiver for 32-nm SOI-CMOS server processors," to be published in *IEEE J. Solid-State Circuits*, vol. 47, no. 11, Nov. 2012.

- [9] W. Yang et al., BSIM4.6.2 MOSFET Model User's Manual, Regents Univ. California, Berkeley, CA, 2008.

- [10] A. Loke *et al.*, "Constant-current threshold voltage extraction in HSPICE for nanoscale CMOS analog design," in *SNUG San Jose Conf.*, Mar. 2010.