#### DOCUMENT RESUME

ED 086 179 IR 000 025

AUTHOR Perone, Sam P.

TITLE Introduction of Digital Computer Technology Into the

Undergraduate Chemistry Laboratory. Final Technical

Report.

INSTITUTION Purdue Univ., Lafayette, Ind. Dept. of Chemistry.

SPONS AGENCY National Science Foundation, Washington, D.C.

REPORT NO NSF-TIE-GJ428-SPPCPU

PUB DATE 31 Aug 73 NOTE 157p.

EDRS PRICE MF-\$0.65 HC-\$6.58

DESCRIPTORS \*Chemistry Instruction; Chemistry Teachers; \*College

Science; Computer Assisted Instruction; Computer Based Laboratories; Computer Programs; \*Computer Science Education; Course Descriptions; Curriculum Development; \*Digital Computers; Inservice Courses; Laboratory Techniques; On Line Systems; \*Science

Experiments: Undergraduate Study

IDENTIFIERS PRTB: Purdue Real Time Basic System

#### ABSTRACT

The objective of this project has been the development of a successful approach for the incorporation of on-line computer technology into the undergraduate chemistry laboratory. This approach assumes no prior programing, electronics or instrumental analysis experience on the part of the student; it does not displace the chemistry content with computer related material. Readily implemented by an inexperienced undergraduate, it utilizes a real-time BASIC language and functionally-oriented general-purpose interface. The result is that the student can regard the laboratory computer as a very powerful routine experimental tool. An intensive three-week summer course was implemented for college instructors and practicing chemists to provide an introduction to digital instrumentation and the technology of digital computer implementation in the laboratory. Other developmental activities have included the design of the Purdue Real-Time BASIC software system and the writing of a number of experiments, both in digital logic and in chemical analysis using the computer, which will be incorporated into the proposed Laborator Manual. The appendixes of this report include the texts of seven of these experiments. (SL)

# FINAL TECHNICAL REPORT

Report Number - NSF-TIE-GJ428-SPPCPU

NSF Grant GJ-428 - "Introduction of Digital Computer Technology into the Undergraduate Chemistry Laboratory"

Principal Investigator: Sam P. Perone

Institution Department of Chemistry

Purdue Univeristy

Lafayette, Indiana 47907

Grant Starting Date --- September 1, 1969

Grant Ending Date --- August 31, 1973

U.S. DEPARTMENT OF HEALTH,

EDUCATION & WELFARE

NATIONAL INSTITUTE OF

EDUCATION

THIS DOCUMENT HAS BEEN REPRO

DUCED EXACTLY AS RECEIVED FROM

THE PERSON OR ORGANIZATION ORIGIN

ATING IT. POINTS OF VIEW OR OPINIONS

STATED DO NOT NECESSARILY REPRE

SENT OFFICIAL NATIONAL INSTITUTE OF

EDUCATION POSITION OR POLICY.

# Initial Objectives.

The objectives of the work conducted here were two-fold: (1) to develop a satisfactory and effective approach to the incorporation of digital computer technology into the undergraduate chemistry laboratory; and (2) to work in collaboration with Profs. C. E. Klopfenstein and C. L. Wilkins of the Universities of Oregon and Nebraska, respectively, to produce and publish a <u>Lab Manual</u> for computerized experimentation at the undergraduate level.

# Major Accomplishments.

The most significant aspect of this project has been the development of a successful approach for the incorporation of computer technology into the undergraduate laboratory. This approach assumes no prior programming, electronics, or instrumental analysis experience. Moreover, a major prerequisite is that the chemistry content of the course work not be displaced by computer-related material. This has been accomplished by developing a laboratory computer system which is readily implemented by the inexperienced undergraduate. It utilizes a real-time BASIC language and a functionallyoriented general-purpose interface. The result is that the student can regard the laboratory computer as a very powerful routine experimental tool. He learns to use this tool properly and effectively, and yet the attention is focused on the chemistry or quantitative measurements to be made. Finally, it should be pointed out that the approach developed here is readily transferable to other institutions, regardless of specific alternate hardware configurations. Thus, the laboratory manual under development should find a wide and accessible audience.

During the past year we have completed, in collaboration with Professors C. E. Klopfenstein (University of Oregon) and C. L. Wilkins (University of Nebraska), an approximately 375 page laboratory manual for instruction of undergraduates in laboratory computer use. All material has been tested, using the manual, in a formal course taught at the University of Nebraska-Lincoln during the Spring semester 1973.

At Purdue, we have developed several of the experiments and appendices for the lab manual. In addition, we have proposed arbitrary standard data acquisition terminology for the Real-Time BASIC language. Finally, we continue working to eliminate "bugs" from old experiments and develop new experiments for inclusion in the Lab Manual. Final manuscript typing has been begun at Nebraska, and a publisher will be selected late this fall after we have obtained responses from all those interested. This will result in publication of the manual in 1974.

# Papers Published, Submitted, or in Preparation.

#### A. Published.

- S. P. Perone, "A Laboratory Course on Digital Computers in Chemical Instrumentation", J. Chem. Educ., 47, 105 (1970).

- J. F. Eagleston and S. P. Perone, "The Introduction of Digital Computer Technology into the Undergraduate Chemistry Laboratory", J. Chem. Educ., 48, 317 (1971).

- J. F. Eagleston and S. P. Perone, "On-Line Digital Computer Applications" in Gas Chromatography. An Experiment for the Undergraduate Analytical Laboratory", J. Chem. Educ., 48, 438 (1971).

- D. O. Jones, M. D. Scamuffa, L. S. Portnoff, and S. P. Perone, "On-Line Digital Computer Applications to Kinetic Analysis. An Undergraduate Experiment", J. Chem. Educ., 49, 717 (1972).

- S. P. Perone, F. E. Lytle, and J. F. Eagleston, "The Introduction of Digital Computer Technology into the Undergraduate Chemistry Laboratory", Proc. of Second Annual Conf. on Computers in the Undergraduate Curricula, Dartmouth College, June, 1971, p. 277.

- S. P. rone, "The Use of Computers in Undergraduate Laboratory Instruction",

Proc of Conf. on Computers in Chemical Education and Research,

1 Kalo, Illinois, July, 1971, p. 4-15.

- erone, "Training Chemists in Laboratory Computing", Computers

Chemical and Biochemical Research, Vol. 1, C. E. Klopfenstein

C. L. Wilkins, eds., Academic Press, NY, 1972, p. 1.

- S. P. Per e and F. G. Pater, "Computer-Controlled Colorimetry. An Under aduate Experiment, "J. Chem. Educ., 50, 428 (1973).

#### B. In Preparation.

- D. O. Jones and S. P. Perone, "Synthetic Signal Sources for On-Line Computer Experiments", J. Chem. Educ., In preparation, 1973.

- S. P. Perone and P. Gaarenstroom, "Real-Time Computer Processing for Predictive Coulometry. An Undergraduate Experiment", J. Chem. Educ., In preparation, 1973.

# Supporting Material.

Included as an addendum to this report are copies of all relevant materials produced by this research program at Purdue. The unpublished materials included will be incorporated into the proposed Lab Manual also.

# Reprinted from:

COMPUTERS IN CHEMICAL AND BIOCHEMICAL RESCARCH, VOL. :

© 1972

Academic Press, Inc., New York and London

# Training Chemists in Laboratory Computing\*

# S. P. PERONE

Department of Chemistry, Purdue University, Lafayette, Indiana

| I.  | A Postgraduate Laboratory Course    | on   | Digita | al Co  | mpu      | iters | in  |    |

|-----|-------------------------------------|------|--------|--------|----------|-------|-----|----|

|     | OL : 1.7                            |      |        |        |          |       |     | 2  |

|     | A. On-Line Computerized Experime    | ntat | ion i  | n the  | <b>:</b> |       |     |    |

|     | Laboratory                          |      |        |        |          |       |     | 3  |

|     | B. An Educational Program in Com    | pute | erized | i      |          |       |     |    |

|     | Instrumentation                     |      | •      |        |          |       |     | 7  |

|     | C. Detailed Course Description      |      |        |        |          |       |     | 11 |

|     | D. Hardware for On-Line Experime    | enta | tion a | and 1  | nter     | face  |     |    |

|     | Design                              |      |        |        | ,        |       |     | 14 |

| II. | Introduction of Digital Computer To | echn | ology  | ' into | the      | Und   | er- |    |

|     | graduate Chemistry Laboratory .     |      |        |        | ٠,       |       |     | 17 |

|     | A. Approach                         |      |        |        |          |       |     | 18 |

|     | B. Purdue Real-Time Basic System    |      |        |        |          |       |     | 19 |

|     | C. Experimental                     |      |        |        |          |       |     | 27 |

|     | D. Results and Discussion           |      |        |        |          |       |     | 32 |

|     | References                          |      |        |        |          |       |     | 35 |

• Reprinted in part from Perone (1970) and Perone and Eagleston (1971), by permission of the copyright owner.

AND material in this document

PERMISSION TO REPRODUCE THIS COPY.

RIGHTED MATERIAL HAS BEEN GRANTED BY

THE OWNER FOR THE PERMISSION OF THE COPYRIGHT OWNER!

# I. A Postgraduate Laboratory Course on Digital Computers in Chemical Instrumentation

The chemist today finds himself in the midst of a dramatic revolution in scientific instrumentation. Digital electronics and laboratory-scale digital computers appear destined soon to dominate the whole area of chemical experimentation. This revolution has come about so abruptly that the practicing scientist recognizes a very real technological gap in his background. He realizes that computerized instrumentation can provide benefits in routine and research work-but he does not know how to get started. To compound his frustration, he even finds it difficult to communicate with the experts and computer manufacturers. Not only is the jargon of digital computer technology quite foreign to the uninitiated, but the fundamental concepts of digital instrumentation are basically unfamiliar. The scientist is accustomed to thinking of experimental data and instrumentation from an analog viewpoint, and the introduction to the digital world is not without some difficulty. Not that the material is difficult—it is really quite simple for the scientist trained in logic—but mastery of the material necessitates the generation of drastically different instrumental and experimental concepts than the scientist is generally accustomed to. The principles, methodology, and jargon of digital instrumentation are so different from those of analog instrumentation that even the instrument-oriented scientist has difficulty mastering the area independently. Moreover, the scientist's ability to use the large data processing computer is of little help in understanding on-line applications of the digital computer.

Because scientists have recognized this technological gap, many have taken steps to overcome it. This has required herculean efforts on their part, generally, since very little detailed information is available. Most of what is available is provided by computer manufacturers, and may require thorough familiarization with a particular computer for any appreciation. The most fundamental problem, however, is that an adequate appreciation of this new technology cannot be acquired through reading or attendance at technical meetings. Moreover, it is not sufficient to have a computer available in the laboratory which the scientist can play with in his

spare time. Nor is it sufficient to develop programming skills which are not oriented toward on-line experimental applications. The most efficient way to develop the technological skills necessary for the incorporation of the digital computer in laboratory experimentation is by total involvement in an intensive training program which includes substantial "hands-on" experience with digital instrumentation and the digital computer in an experimental on-line environment.

Thus, a need has existed for some time now to provide an educational program concerned with digital computer instrumentation for the chemistry laboratory. This type program is urgently sought by the practicing scientist—i.e., one who has completed his formal education. Moreover, this type program should be particularly valuable to our future scientists—the graduate and undergraduate students in our colleges and universities. Such a program has been instituted in the Chemistry Department at Purdue University under the direction of this author. It is the purpose of this article to describe the basic philosophy of this program as well as to provide the reader with many of the details of its operation. In addition, an evaluation of the results of this program will be presented.

#### A. On-Line Computerized Experimentation in the Laboratory

To put this entire presentation in perspective, it is necessary to provide some background regarding on-line digital computer technology. A common characteristic of the laboratory-scale digital computer is a relatively small core memory, usually providing 4 K or 8 K of random access storage of digital data and programs. A memory of this size, however, can be more than adequate for laboratory control operations, and with careful programming, some fairly sophisticated data processing.

A small digital computer may have an instruction set which includes the order of 50-100 machine language instructions. Each of these instructions corresponds to a specific binary coding which, when decoded by the computer, results in the execution of a fairly simple arithmetic or logical step. Examples of some simple machine operations are (1) binary addition of a datum in some memory location to the contents of an arithmetic register (accumulator);

(2) transfer of the contents of an accumulator to a memory location (and vice versa); (3) rotation of the binary digits ("bits") of the accumulator contents to the left or right; (4) and the application of logical tests such as determining if the accumulator is zero, non-zero, odd, even, positive, negative, etc.

Obviously, the repertoire of machine instructions includes some rather elementary operations. However, by developing appropriate "programs" composed of many of these elementary operations, the most sophisticated mathematical computations can be carried out. Since the computer can execute instructions so rapidly—the order of  $10^5$ – $10^6$  instructions per second—it can complete complex computations with fantastic speed. For example, a program to multiply two n-bit integer values might require a program including 50 or 60 statements, but may require only about 200  $\mu$ sec for completion. Thus, some 5000 multiplications per second could be accomplished. With hardware arithmetic units, perhaps 100,000 multiplications per second could be completed.

Thus, the digital computer is a very simple-minded device, which must be told how to accomplish even the most fundamental computations, but which can accomplish these operations with blinding speed. Moreover, it is a tireless machine that will be content to calculate endlessly and consistently. It is also a very versatile device, since it is programmable and capable of accomplishing an infinite variety of computational, logical, or control operations. Finally, it is a device that can (in fact, must) communicate in a variety of ways with the outside world. It is this characteristic that defines the computer as a general-purpose experimental device.

#### 1. Off-Line Computers

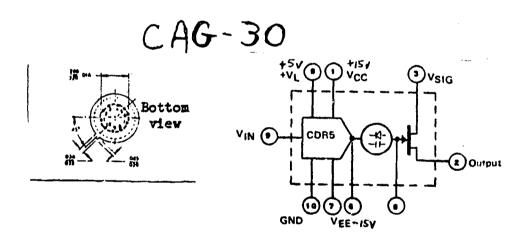

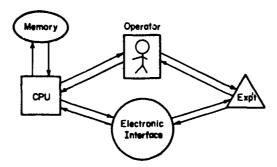

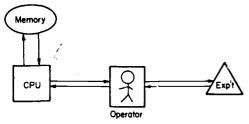

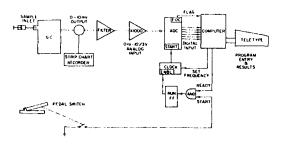

The computer configuration with which most scientists are familiar is the off-line system. This configuration is diagrammed in Fig. 1. To use the computer in this configuration, the scientist typically will write a data processing program in FORTRAN or some other higher level computer language, run the experiment(s), manually tabulate the data from a strip chart recorder or oscilloscope trace, transfer the tabulated data to punched cards, add the data cards to the deck of program cards, transport the combined card deck to the computer center for processing, and then wait until the program has been executed and the results printed.

Fig. 1. Typical off-line computer configuration.

Turn-around times may vary from a few minutes to a few days, depending on the capacity of the computer facility and the number of users.

There are many variations of the above description of off-line computer usage. For example, the experimental system may include automatic data acquisition and digitizing devices which might store data on punched card, punched tape, or magnetic tape buffers which can then be transmitted more conveniently to the remote computer center. Alternatively, the laboratory may be equipped with a remote terminal (such as a Teletype) through which the investigator may enter his programs and data, as well as receive a printout of results from the computer.

The important common characteristic of all off-line computer systems, however, is that the experimental data are transmitted to the computer through some intermediate storage medium, and they are processed after some finite time delay has occurred. Depending on the modes of data acquisition and transmission to the computer, the turn-around time of the computer facility, and the speed with which the investigator can interpret the resulting printout, the time delay for experimental modifications based on the results of previous experiments can be excessive. Should this reaction time be a critical factor, an off-line computer facility may be inadequate for the particular experimental studies.

# 2. On-Line Computers

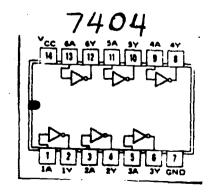

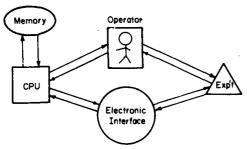

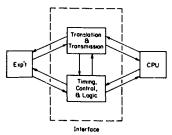

For the investigator who requires very rapid or instantaneous results from his computer system—for whatever reason—the solution may be to employ an on-line computer system. Figure 2 presents a block diagram for a typical on-line computer configuration. The most important distinction of this configuration is that there

Fig. 2. Typical on-line computer configuration.

is a direct line of communication between the experiment and the computer. The line of communication is through an electronic interface. Data are acquired under computer control or supervision, and the program for data processing is either resident in memory or immediately readable into memory to provide for very rapid completion of the computational tasks. Results may be made available to the investigator quickly by means of teletype, line printer, oscilloscope, or other form of printout. In addition, the computer may be programmed to communicate directly with the experiment by controlling electronic or electromechanical devices—such as solid state switches, relays, stepping motors, servo motors—or any other devices which can be activated by voltage level changes.

The advantages of on-line computer operation can be surumarized as the following: Elimination of the middle man, and the concomitant substitution of an electronic interface between the computer and the experimental system, which is much more compatible with the computer's characteristics and does not suffer from the inherent inadequacies of the human as a communication link. For example, the computer can accept input data at rates of the order of 10<sup>5</sup>-10<sup>6</sup> per second, and can instantaneously transmit control information or commands back to the experimental system. If this line of communication were handled through the human investigator, as in the typical off-line configuration, the response time of the overall experimental and data processing system would be many orders of magnitude slower. Moreover, the electronic communication link is generally a more reliable, tireless, objective, and accurate information transfer medium.

The possibility of direct computer control of the experiment is

a second advantage associated with on-line computer operation. This facility allows the complex logical and decision-making capabilities of the computer to be implemented for an infinite variety of laboratory automation or experimental design problems.

A third advantage of the on-line computer is that real-time interaction between computer and experiment is possible. That is, because the computer can make computations and decisions at speeds exceeding most ordinary data acquisition rates, it is possible for the computer to execute experimental control modifications before a given experiment has reached completion. These "real-time" operations allow the possibility of using the computer to monitor the progress of an experiment and modify that experiment to follow a pathway which provides more nearly optimum conditions and which could only have been arrived at as a result of some observation of the initial course of the experiment.

A breakdown of the logistical barriers of the remote computer system is an additional advantage of on-line computer operation. Because of the instantaneous, direct communication link between the experiment and the computer, the physical location of the computer with respect to the laboratory is relatively unimportant. Moreover, the mechanical and logistical roadblocks typically imposed by the computer facility toward the off-line introduction of data are irrelevant.

One very important aspect of using computers for on-line experimental work that should be emphasized here, however, is that some, if not all, of the programming must be done in machine (or assembly) language. That is, higher level languages, such as FORTRAN, do not have the capability for on-line operation with experimental systems. Moreover, higher level languages tend to be very inefficient in the use of memory space and in execution time. Both of these factors are critical when small computers are used for on-line work. Thus, the scientist wanting to use the small digital computer in the laboratory must become competent in programming in the fundamental machine language—a formidable task.

# B. AN EDUCATIONAL PROGRAM IN COMPUTERIZED INSTRUMENTATION

The widespread use of digital computers on-line in chemistry laboratories will certainly revolutionize routine laboratory method-

ology. Today's scientist must learn to live with the digital computer and to use it profitably for laboratory work. On this premise we have developed at Purdue an intensive 3-week summer short course entitled "Digital Computers in Chemical Instrumentation." The course is designed for practicing scientists in colleges, universities, industrial laboratories, government laboratories, and hospitals, to provide an introduction to digital instrumentation and the technology of digital computer implementation in the laboratory. It is the details of this summer program which will be discussed here.

#### 1. Objectives

The purpose of the 3-week intensive course developed at Purdue was to afford participants an opportunity to acquire a familiarity with digital instrumentation and digital computers in the laboratory. The course was designed such that students could develop, in a short period of time, the ability to write machine-language programs, to utilize the computer for typical laboratory input/output functions, and to design and implement software and hardware for interfacing real experimental systems to the computer for online operation. An essential feature of the course had to be the availability of several digital computers and many digital logic modules to provide a large amount of hands-on laboratory experience for each participant. To make the experience most worthwhile to the participants, the lecture and laboratory material were developed within the context of applications in chemistry and related sciences. (The course material was based on the assumption that participants had no previous experience with computers, digital logic, or electronics, but were generally familiar with chemical instrumentation and laboratory methodology.)

# 2. Approach

The basic philosophy of the 3-week summer course is simply to share with the participants the background, technique, and experience in computer instrumentation developed at Purdue and elsewhere by the faculty and graduate instructors of the course. For the participants to acquire the desired skills and background in the 3-week period, it is absolutely necessary to provide for as much individual access to computing equipment and digital instru-

mentation as possible and practicable. To provide this "hands-on" access to the equipment in the most efficient manner, a great deal of preparation outside the laboratory is required. Most importantly, a large ratio of teaching staff to students is provided, so that students can obtain help with a minimum of delay. At least one instructor for every four students in lab is the normal working ratio at all times.

The significance of the emphasis put on the efficient use of the available computing equipment cannot be overemphasized. The natural tendency of the novice programmer is to sit down at the computer console and try to compose a program. The students in our course learn very quickly that they must have their programs fully composed and punched on tape—with perhaps one or two alternates, in case the first does not work—before they even get to the computer console. When programs do not execute properly, they are encouraged to spend a minimum of formal lab time in time-consuming debugging operations. Thus, when a program is to be edited and reexecuted by the computer, a minimum of "hands-on" time will be consumed by the student trying to reason away the logical errors in his program.

Another important aspect of the course is that it is not limited to the concepts, principles, and techniques associated with the "small" digital computer. The formal lecture material discusses large, time-shared systems as well as small, dedicated systems. Moreover, one laboratory assignment involves writing a program and designing an interface to time-share several peripheral devices. The principles learned in this laboratory assignment are extended in lecture to describe the operation of larger time-shared computer systems.

#### 3. Requirements

Equipment. An essential requirement for the presentation of the short course on computers in chemical instrumentation is the availability of sufficient hardware to allow adequate hands-on access by each participant. The minimum equipment provided for a twelve-man laboratory session includes: three digital computers with 8 K-word core memories, ASR/33 teletypes, and high-speed paper tape readers. One of these computers is equipped with a high-speed paper tape punch. In addition, each computer is com-

pletely equipped for high- or low-speed computer-controlled digital data acquisition with three 10-bit analog to digital converters (ADC) (each capable of data acquisition rates up to 20 or 30 KHz), and three frequency-selectable gated clocks for precise timing and synchronization of data acquisition and other experimental events. Two computers are equipped with high-precision (16-bit), high speed (20  $\mu$ sec risetime) digital to analog converters (DAC). Two computers are equipped with oscilloscope display units interfaced to the computer through dual eight-bit DAC modules.

In addition to the computer equipment, each twelve-man laboratory has available six digital logic training stations. Each training station is equipped with versatile patchboard devices for assembling and testing digital logic circuits. Systems used for these stations include the Digital Logic Laboratory, Digital Equipment Corp., Maynard, Mass., and the Elite 3-a integrated circuit device tester, El Instruments, Inc., Derbyshire, Conn. Also with each station is a dual-trace wide bandpass oscilloscope. These stations are also used for assignments requiring interface design for computer-interfaced instrumentation.

Other items necessary to completely equip the laboratory include a variety of specially designed patchboard modules and associated electronics for instrumentation interface design, which are described in detail below. Also, at least one off-line ASR/33 teletype per every four students is provided for program preparation on punched paper tape.

Personnel. One of the most subtle, and yet most critical, requirements for presentation of the course described here is the availability of qualified individuals who understand the software and hardware aspects of computerized experimentation in the laboratory, and who can teach the material. At Purdue, we have been fortunate to find such personnel among our graduate students.

The explanation for the presence of qualified personnel here is twofold. We have several staff members who have become actively involved in on-line computer applications in their research, and we offer a formal one-semester course for graduate students designed to provide first-hand familiarity with on-line computer techniques in the chemistry laboratory. (This graduate level course, first offered informally in Spring 1968, formed the basis for the

present intensive 3-week summer course.) Thus, by offering both the graduate course and the 3-week summer course, we have developed a unique group of well-trained teaching assistants.

#### C. DETAILED COURSE DESCRIPTION

#### 1. Schedule

The summer course spans three weeks (or 15 working days). The first day is devoted to orientation and the first lab lecture. The next 13 weekdays are devoted to a rigorous schedule of laboratories, formal lectures, lab lectures, and open lab time. Each participant spends 1½ hours in lab lecture, 1½ hours at formal lecture, and 2½ hours in formal laboratory daily. In addition, each student has about two additional hours per day of "open" access to lab equipment so that he might work ahead or catch up. Labs also are open and supervised part-time on weekends. One day is devoted entirely to the demonstration of various on-line systems operating in the Chemistry Department at Purdue (including mass spectrometry, electrochemistry, flash photolysis, gas chromatography, and stopped-flow kinetic spectrophotometry). The last day is devoted to a "mini-symposium" on computer applications in chemistry, to which several expert outside speakers are invited.

#### 2. Content

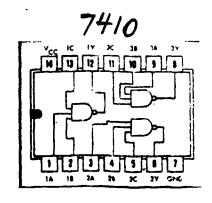

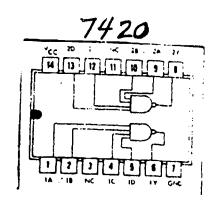

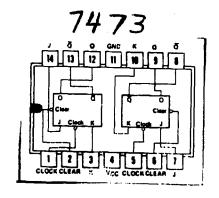

The formal lecture material covers the following three areas: digital logic and digital instrumentation; computer programming for on-line laboratory applications; and hardware and software design for instrumental interfacing, time-sharing, and computer control in the laboratory. A detailed lecture outline for the short course is given in Table I.

The formal laboratory assignments, likewise, were broken down into three categories: basic digital logic design and operation (4 days); basics of assembly language computer programming and operation (4 days); and interface design and computer programming for on-line applications (5 days). Lab lectures (1½ hours per day) were designed to prepare the student in advance for each laboratory assignment. Table II contains a detailed list of laboratory assignments.

TABLE I

#### SHORT COURSE LECTURE SCHEDULE

- I. Introductory Remarks

- II. Elements of Digital Logic

- III. Digital Functional Units

- IV. Number Systems; Binary Arithmetic, etc.

- V. Boolean Algebra-Applications to Digital Circuitry

- VI. Analog-to-Digital, Digital-to-Analog Conversion

- VII. Computer Organization and Machine Language

- VIII. Assembly Language Programming; Simple Arithmetic Routines

- IX. Chemical Data Processing Routines

- X. Programming the Computer for Input/Output with Standard Peripheral Devices

- XI. Applications of Digital Logic in Chemical Instrumentation

- XII. Digital Logic in Experimental Timing, Control, and Synchronization for Computer Interfacing

- XIII. Data Acquisition and Real-Time Computer Control in Experimental Systems

- XIV. Time-Sharing Systems; Combining Languages; Large Computer Systems

TABLE II

# SHORT COURSE LABORATORY ASSIGNMENTS

- A. Digital Logic

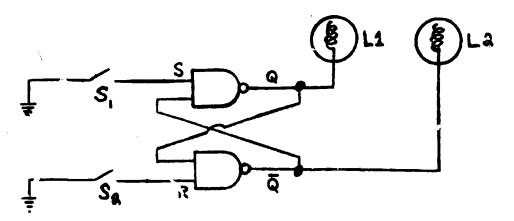

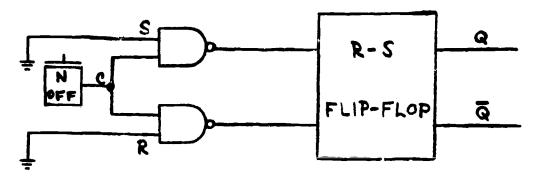

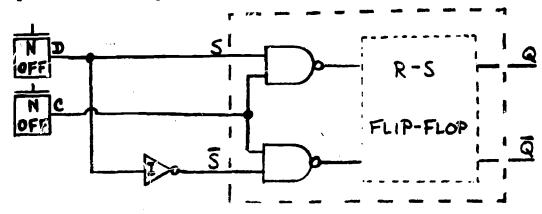

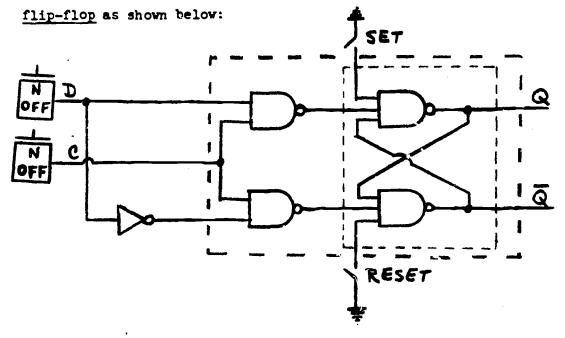

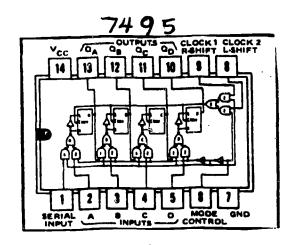

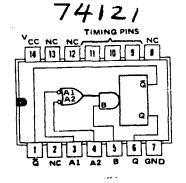

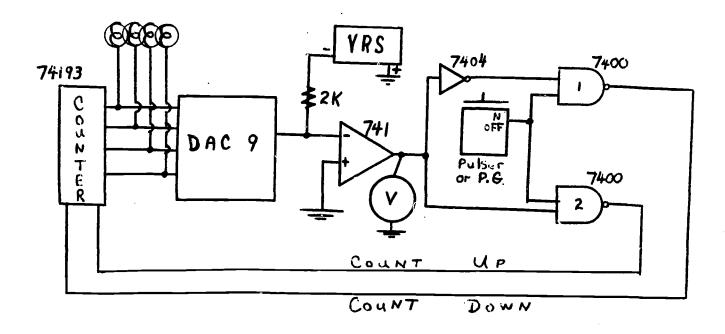

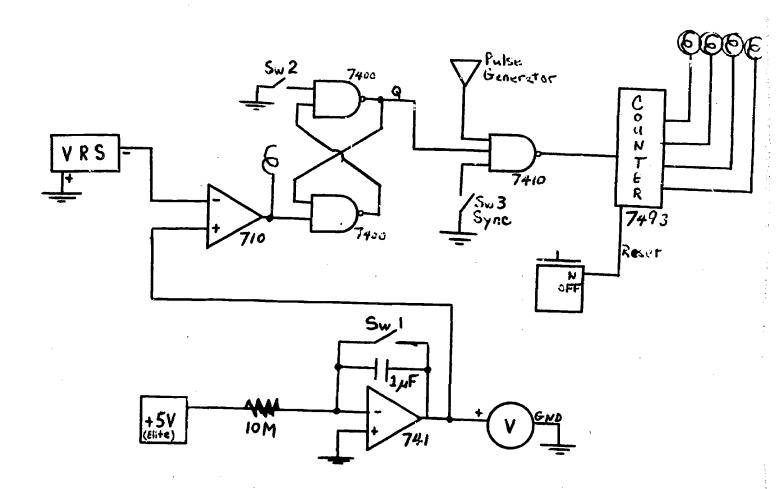

- I. Flip-flops and counters

- II. Gates and fundamental logic circuits

- III. Boolean equations and logic design

- IV. Digital control, timing, and synchronization

- B. Computer Programming Fundamentals

- I. Elementary machine, and assembly, language programming

- II. Simple arithmetic programs

- III. Chemical data processing algorithms

- IV. Input/output programming

- C. Interfacing and On-Line Computer Programming

- I. Data acquisition from a transient experiment

- II. Digital input/output

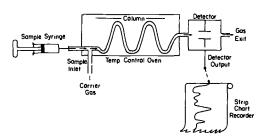

- III. Data acquisition and processing of gas chromatographic data

- IV. Ensemble averaging

- V. Time-shared service of several peripheral systems

- VI. Multiplexing and digital-to-analog operations

# 3. Laboratory Procedures and Organization

The organization of the laboratory and lab assignments is certainly most critical to the successful presentation of the short course.

With the available equipment providing the basic limitation on laboratory size, the labs were organized to make most efficient use of the hardware. This was accomplished by, first, dividing each lab into two groups: one-half start out working with the computer equipment; one-half start out working with digital logic equipment. Four days are required to complete the basic assignments in each group. Then, the two groups of students exchange equipment, and the basic set of assignments are repeated during the next four days. Two students are assigned to one computer per lab; one student is assigned to one logic station per lab.

While the basic sets of laboratory assignments are being carried out, the logic group attends lectures II-VI (Table I), while the computer group attends lectures VII-X. These basic lectures are primarily oriented towards the assigned laboratory material and are repeated when the two groups switch assignments.

After all participants have completed the basic sets of logic and computer programming assignments, five days of laboratory work follow which are oriented towards the development of programs and interfacing for on-life experimental applications. Students may continue to work in parts on these assignments using any of the hardware available in the lab to execute each assignment. The apportionment of the computer time must be carefully supervised by the lab instructors ouring this period so that the equipment is used efficiently. One approach found effective here was to make available a fourth computer system which was used only for assembling and editing of program tapes. This freed the other computer systems for program execution and experimental design.

An interesting innovation was introduced during one recent course. Through the generosity of several computer manufacturers (Hewlett-Packard, Palo Alto, Calif.; Digital Equipment Corp., Maynard, Mass.; and Varian Data Machines, Palo Alto, Calif.) several different computer systems were made available during the last week of the course so that students might have the option of working with alternative equipment. The only requirement imposed was that they complete all normal course assignments up through

at least the basic set of on-line experiments (C-I, C-II, Table II). Thus, confident that they had been exposed to all the basic technology we would hope to provide, we could turn students loose on unfamiliar equipment. Our objective was to prove to students that the operational differences between systems are not so great as they appear, once the fundamental principles have been mastered.

To make this possible, the additional equipment made available included two DEC PDP-8L computers with high-speed paper tape input/output, interfaced 12-bit ADC and four-channel multiplexer, and ASR/33 teletype; two DEC PDP-12 computers with full standard interfaced experimental input/output facilities (ADC, DAC, etc.), two LINC tape decks, oscilloscope display, and ASR/33 teletype; a Varian 620-i computer with provision for experimental I/O, oscilloscope display, and an ASR/33 teletype. In addition, two Hewlett-Packard computers (2116B and 2115A) with high-speed paper tape input and ASR/33 teletype were provided by the manufacturer for use along with the University-owned Hewlett-Packard systems.

The results of using the alternative computer equipment were very gratifying. Nearly all of the students who switched to the unfamiliar equipment were able to quickly master the new assembly language software and operating procedures. In fact, many were able to develop programming and interfacing for on-line operation. All this was accomplished with only a total of three days exposure to the equipment! These results seemed to prove that the necessity for exposure to one type of computer equipment in the laboratory part of the course is certainly no hindrance to the later use of other systems.

# D. HARDWARE FOR ON-LINE EXPERIMENTATION AND INTERFACE DESIGN

Because it was unrealistic to assume that all students would be skilled in electronics, the development of lecture and laboratory material on interfacing experimental systems for on-line operation was particularly challenging. However, by building on the fundamentals of digital logic learned in the éarly part of the course, it is possible to adequately cover the topic of interface design.

The basic approach used involved recognizing that the digital computer communicates with the outside world by the execution of instructions which either cause binary voltage level changes to occur at specific external terminals, or which recognize voltage level changes effected by external devices. This understanding, coupled with the fact that the digital computer can neither accept nor output normal analog (continuously variable) signals, determine the type of interface functions required.

One primary group of interface elements to be considered are translational modules, such as analog-to-digital converters and digital-to-analog converters. In addition, such devices as level converters and analog amplifiers contribute to translational functions. Also important for consideration are multiplexers and signal transmission problems.

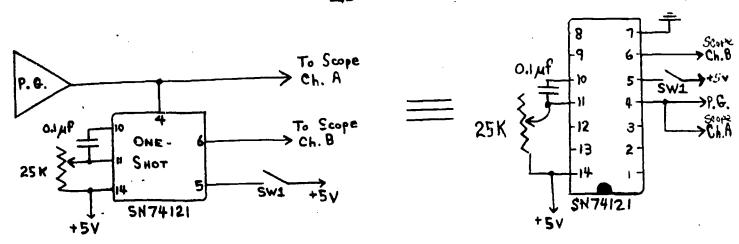

Those elements essential to proper communications are the logic, timing, and control components. These include flip-flops, gates, one-shot delays, Schmitt triggers, clocks, counters, analog switches, and electromechanical devices like relays and stepping motors. The student is made aware of the functional characteristics of all of these interface elements. (Many are actually used and tested individually in the laboratory.) He is then responsible for designing interfaces for assigned experiments by selection and combination of appropriate elements to provide both the translational and logical functions required. This means that he must be able to provide for the coordination and synchronization of the computer's program execution with the experiment and with the data acquisition system.

To implement these principles in the laboratory, we provide students with the building blocks with which the actual interface can be constructed in patchboard fashion, once the logical design is complete. Included in the patchboard interfacing package are a 10-bit (30 KHz) externally controlled ADC; a gated 10 MHz crystal clock with sealed outputs available in decade steps from 1 MHz to 0.01 Hz; a four-channel multiplexer; two sample/hold amplifiers; and 8 bits of binary control and logic I/O. Another type of patchboard interface panel is available which provides for 16-bit digital I/O only. The digital logic stations are available to allow incorporation of logic and timing elements (gating, time-delays, etc.) not included in the basic interface panel. All interconnections can be made externally with plug-in leads. (See Section II for a detailed view of interfacing hardware.)

# 1. On-Line Experiments

The ultimate objective of the laboratory work is for students to be able to carry out experiments on-line with the digital computer. Thus, the final set of laboratory assignments requires the student to design and implement the programming and interfacing for a variety of on-line experimental systems. Only the detailed characteristics and data acquisition requirements for each experiment are specified for each assignment.

Basically, two types of experimental systems were provided for laboratory assignments: synthetic and real. The synthetic systems were electronically simulated experimental outputs where the control, synchronization, and signal-handling problems were made nearly identical to several real systems. These electronic simulators were constructed on printed-circuit cards that could be plugged into the patchboard logic devices. Thus, patchboard interfacing could be implemented easily.

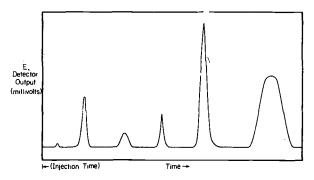

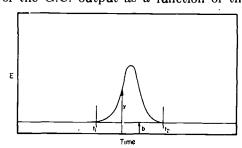

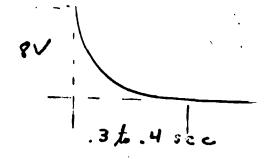

Simulated experimental output included an externally triggered rapid exponential transient decay voltage (time constant of 0.1 sec); an externally triggered repetitive voltage waveform with superimposed large amplitude random noise for signal-averaging studies; simultaneously generated multiple voltage waveforms for multiplexing experiments; and a synthetic typical gas chromatographic output including several peaks of varying shape and size.

The above-simulated systems provided convenient, reliable, and realistic on-line experimental experience for each student. The most obvious advantage was the freedom from chemical and instrumental uncertainties invariably associated with real chemical laboratory systems. On the other hand, it was desired to provide some experience with real laboratory systems, since this appears to make the most lasting impression on students. Thus, laboratory gas chromatographs and a variety of sample mixtures were made available for students to apply their on-line data acquisition and processing skills. Appropriate amplification of the normal GC outputs could be provided by the selection of an operational amplifier-based plug-in module. The rest of the interface design was left to the student.

The minimum of assignments expected to be completed by all students included data acquisition from a simulated transient experiment, using computer-controlled constant or variable data acquisition rates, and computer-controlled data acquisition from an

external digital counter. Beyond these minimal assignments students could carry out ensemble averaging, multiplexing, and gas chromatographic experiments. In addition, assignments involving computer-controlled digital-to-analog waveform generation and time-sharing of multiple external systems could be executed.

Many of the above described assignments required that real-time data analysis be incorporated into the programming. That is, some assignments required data analysis during data acquisition. Mastery of this type of programming is indicative of an accomplished experimental programmer.

#### 2. Results

The primary result of the development and presentation of the course described here has been to make available to practicing scientists, regardless of background or previous experience, a rapid, effective introduction to computer technology in the laboratory. In addition, the instrumentation and educational techniques developed for the short course have been incorporated into a graduate-level chemical instrumentation course offered at Purdue.

Moreover, many of the university and college professors taking the summer course have been encouraged to develop similar computer-oriented course work at their respective institutions. Thus, the development of curricula which include the on-line implementation of computers in undergraduate and graduate scientific work has been fostered in a most efficient manner.

# II. Introduction of Digital Computer Technology into the Undergraduate Chemistry Laboratory

It should be clear that the chemist of the near future will be required to understand and properly use digital instrumentation and digital computers in the laboratory. Furthermore, educators at colleges and universities will need to develop undergraduate curricula providing the required background in computerized chemical instrumentation. This section describes the first steps in a long-range program involving the introduction of on-line computer applications in the undergraduate chemistry laboratory at Purdue. The introduction has been made as part of an introductory analyti-

cal chemistry course dealing with quantitative chemical measurements (Junior level at Purdue). A primary objective was that none of the chemical and instrumental principles normally developed in the course be climinated, but rather that these be augmented by the incorporation of the on-line computer into many of the laboratory experiments. The manner in which such a program may be made feasible is described below.

#### A. Approach

It was our intention to introduce computer technology into the undergraduate chemistry laboratory without slighting the chemistry content. The approach has been to continue to include the same basic set of laboratory experiments—except that many are now designed to require on-line communication with the digital computer. The student is required to understand and execute the laboratory experiment as usual—but, in addition, he is required to design the appropriate programming and communication elements for optimum interaction between the computer, experiment, and experimentalist. Thus, we envision the student's achievement to be one of experimental design, and the proper utilization of computing equipment in the solution of measurement problems in chemistry. Specific aspects emphasized include the general-purpose nature of the digital computer (i.e., how it can be applied to a large variety of experimental problems with modifications in programming); the computer as a control element in experimentation; the rapid response of the computer, allowing real-time interaction with experiments-with reaction times several orders of magnitude faster than the human operator; and the computer as an integral part of the chemical instrumentation.

To accomplish these objectives, it was necessary to recognize, first of all, what could not be expected within the scope of this course. (1) We could not educate our students in the intricacies of machine-language programming, and (2) we could not provide them with the electronics background requisite for the sophisticated design and construction of interfacing between computer and experiment.

What could be done is to take advantage of students' previous exposure to off-line computer programming (with FORTRAN

usually), which many, but not all, students have obtained before the Junior year at Purdue. We could also take advantage of their exposure to the fundamentals of electrical measurements in physics courses to instill in them the most elementary concepts of amplification, response, and noise. We could expect to provide them with the essential principles of digital logic required for interface design.

The most important requirement for the success of the program, however, was the development of two items: (1) a modified highlevel programming language, which includes versatile data acquisition and experimental control subroutines with conversational mode calling sequences; and (2) a general-purpose hardware package for interface design. This apparatus would provide for patchboard incorporation of those digital and analog modules required to complete the interface between computer and experiment. The general-purpose interface package requires only that the student be able to lay out the basic logic design, timing sequence, and the analog amplification or attenuation required. He can then select appropriate pre-packaged plug-in units to implement his design. He does not have to tend to such details as level conversion, logic conversion, noise rejection, and other subtle design parameters. Yet, he will accomplish the most important part of the interface development—logic design.

#### B. PURDUE REAL-TIME BASIC SYSTEM

The high-level programming language chosen for development in this work was the BASIC language (Kemeny and Kurtz, 1967). There were several reasons for selecting this language: (1) It is easy to learn, generally requiring on the order of half a day exposure to develop a good working knowledge. (2) It is an algebraically oriented conversational language. (3) It is interactive. That is, the compiler is interpretive, and therefore compiles and executes programs line-by-line. This allows programs to be entered, executed, and edited on-line through a teletype terminal. It also provides for immediate turn-around and rapid error diagnostics. (4) BASIC is rapidly becoming a universally acceptable language. (5) BASIC is currently readily available at commercial time-share terminals. This allows the convenient and economical learning of

the language by large numbers of students for later on-line experimental applications.

It should be noted that other languages (e.g., FOCAL¹) are available which have comparably desirable characteristics. Even languages such as FORTRAN or ALGOL which are generally considered strictly for off-line applications may be appropriate, particularly for systems with "load-and-go" capability.

The software system developed at Purdue will be referred to as "Purdue Real-Time BASIC" (PRTB). The software includes, fundamentally, the BASIC compiler available from Hewlett-Packard Co., which manufactured the computers used in the undergraduate laboratory program (see Section II,C). The modifications generated here at Purdue have involved the development of a series of machine-language subroutines which are directly callable from the BASIC software, and which are designed to communicate in a variety of ways with experimental systems. The PRTB data acquisition and control software are described below.

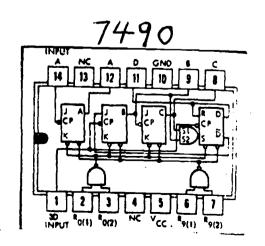

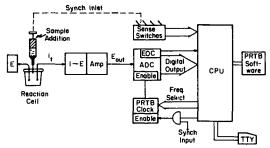

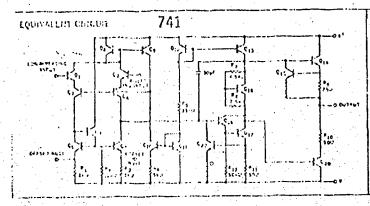

# 1. General Description of PRTB System

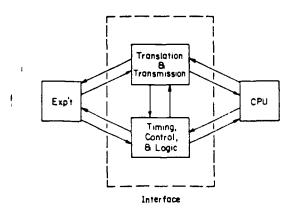

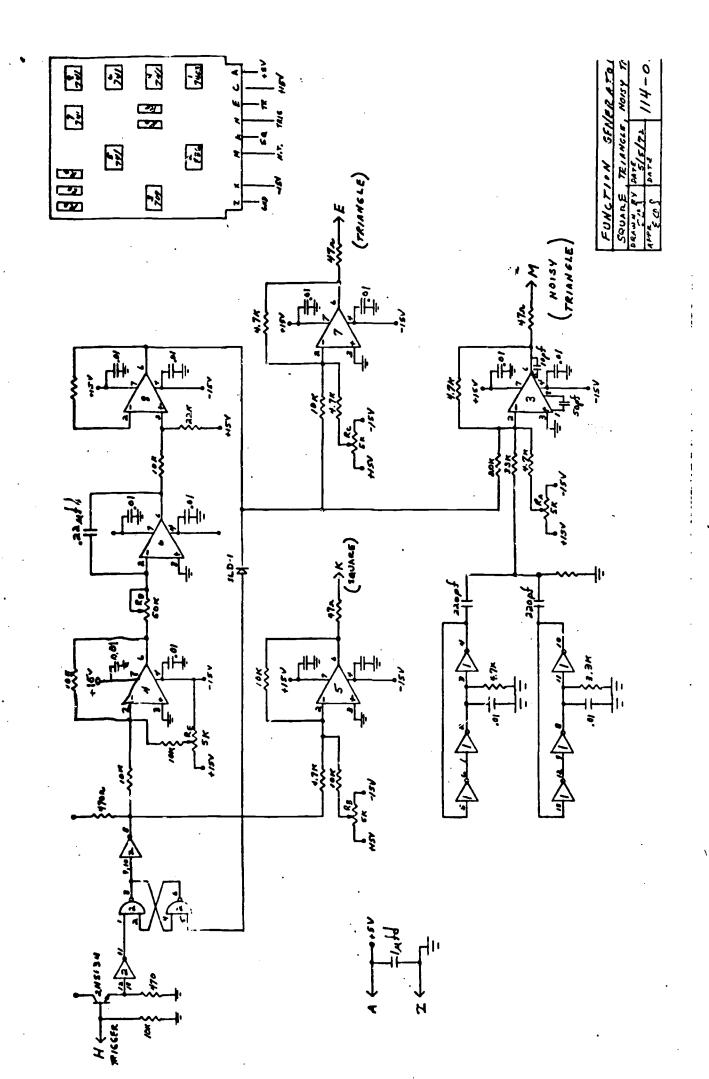

Figure 3 illustrates the general nature of an on-line computer system. There is the laboratory experiment—the data from which the student desires to present to the computer for data processing—and the digital computer itself, which is capable of high-speed

Fig. 3. Schematic diagram of on-line computer configuration.

<sup>&</sup>lt;sup>1</sup> Trade-mark, Digital Equipment Corp., Maynard, Mass.

programmed computational and control functions. To operate the communication link between the computer and the experimental system, an electronic interface must be established. This interface accomplishes the functions of translation (analog-to-digital, digital-to-analog, decoding, logic conversions, etc.), timing, synchronization, and logical control. The programming language must take into account the nature of the electronic interfacing, and the interfacing must be designed with the fundamental characteristics and capabilities of the programming language in mind. The following section describes the subroutines developed for on-line experimentation within the PRTB system. A summary of these subroutines and characteristics is given in Table III.

#### 2. Experimental Input/Output Subroutines for PRTB

Data Acquisition. Two different types of data acquisition subroutines are available within PRTB. They both work in conjunction

with an external clock-controlled analog-to-digital converter. One

is a subroutine (SB3) which should be called by the user's program

whenever the computer should be waiting for the next data point

to become available. When the next datum is digitized, SB3 takes

the data point from the data acquisition device (ADC), converts

the datum to floating point format, and stores it in the appropriate

memory location for subsequent reference by the BASIC program.

When SB3 is exited, the computer returns to the next statement

in the BASIC program for execution. The new datum can be

operated on; but, before the next data point can be acquired, SB3

must be called again.

A second type of data acquisition subroutine (SB7) is one that allows for the acquisition of a complete block of data before exit. The external clock is started and synchronized with data acquisition within the subroutine. The basic difference between SB7 and SB3 is that SB3 is called to acquire one data point at a time, and therefore allows for program statements to be executed during the time between acquired data points. Thus, an experimenter could devise a program that could process experimental data while the experiment was in progress and data were being acquired. This is referred to as "real-time" data processing. However, because the computer program must involve the relatively inefficient execution of BASIC statements between data points, there is a more severe limit on the speed with which data can be acquired without the computer

TABLE III

DATA ACQUISITION AND CONTROL SUBROUTINES FOR PRTB

| Subroutine | Function                                                                                                                                                                                                                                                                                                           | CALL Format     |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| SB1        | Initialize I/O. Set up data storage address and acquisition rate for other subroutines. " $X(I)$ " data variable. " $F$ " = data acquisition frequency.                                                                                                                                                            | CALL (1,X(I),F) |  |

| SB2        | Used to start the CLOCK. The output control bit (ENCODE) can be connected to some external logic preceding the CLOCK ENABLE input. (NOTE: SB2 must be preceded by SB1.)                                                                                                                                            | CALL (2)        |  |

| SB3        | Waits for ADC FLAG, indicating conversion completed. One datum is then taken from the ADC, converted to floating point, and saved as X(I).                                                                                                                                                                         | CALL (3)        |  |

| SB4        | When called this subroutine waits for switch 0 of the console switch register to be set to a "1" before continuing with the next statement in the BASIC program.                                                                                                                                                   | CALL (4)        |  |

| SB5        | Outputs one control bit (ENCODE) and then waits for an event FLAG on the specified I/O channel, "C," before continuing. FLAG and ENCODE are cleared before exit.                                                                                                                                                   | CALL (5,C)      |  |

| SB6        | Waits for FLAGS on the ADC channel. When FLAG is set, the next statement in the BASIC program is executed. (Must be preceded by SB1 and SB2 if internal CLOCK is used to generate r'LAGS.)                                                                                                                         | CALL (6)        |  |

| SB7        | Takes in complete block of data before returning to BASIC program. (Max. of 250 points. Must be preceded by SB1 each time it is called.) "T" sets total No. of data points taken. Synchronized with start of experiment through external gating of the ENCODE output. Up to 20 KHz data acquisition rate possible. | CALL (7,T)      |  |

| SBS        | Causes output bit No. "Z" to be set TRUE on specified I/O channel, "C." Z, C specified in decimal. All other bits will be cleared.                                                                                                                                                                                 | CALL (8,Z,C)    |  |

| SB9        | Causes output of analog voltage through the DAC, " $D$ " = $mV$ output,                                                                                                                                                                                                                                            | CALL (9,D)      |  |

TABLE III (Continued)

| Subroutine | Function                                                                                                                                           | CALL Format             |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| SB10       | Clears ADC channel. External Flip-flop<br>driven by ENCODE will be cleared also.<br>This can be used to turn off clock, stop ex-<br>periment, etc. | CALL (10)               |  |  |

| SB11       | Causes output of binary voltage pattern, "Z," on specified output channel, "C."  Binary pattern and channel specified in decimal.                  | CALL (11,Z,C)           |  |  |

| SB12       | Inputs status of 16-bit register on channel "C." The floating point equivalent is saved in memory as "Z."                                          | CALL (12,Z,C)           |  |  |

| SB13       | Inputs status of a specific bit (No. "Z") on channel "C." Value of "S" is made "1" or "0" accordingly.                                             | CALL (13, <b>Z,S,</b> C |  |  |

getting out of synchronization with the experimental timing. In fact, SB3 is designed to detect when the computer got out of synchronization; an error message will be typed, and the computer will halt. The user will then have to revise his program to require less real-time processing. With SB7, on the other hand, a complete block of data points is acquired before the subroutine is exited and control returned to BASIC. Therefore, the timing is limited by the efficiency of the machine-language programming developed within SB7. For our computer systems and software, it is possible to acquire data at rates as great as 20 KHz with SB7, but no real-time data processing is possible.

The limiting data rate when using SB3 is about 500 Hz, with a minimum of real-time data handling. If several BASIC computations are to be executed between data points when using SB3, the limiting data acquisition rate may be the order of 1 to 50 Hz. However, this is generally more than adequate for most experiments in the chemistry laboratory.

Experimental Control and Logic. In addition to data acquisition, there are several other ways in which the computer can communicate with the experimental system. One of these is through a digital-to-analog converter (DAC), where the digital output of the computer is converted by the DAC to an equivalent analog voltage level. One of the PRTB subroutines (SB9) provides the capability

for driving the DAC, the output of which can be connected to external experiments. It is possible to generate a continuous voltage waveform output from the DAC by mathematical generation within BASIC of the discrete points making up the waveform and transmitting these through SB9 to the DAC in a repetitive fashion synchronized with an external clock.

Subroutines SB8 and SB11 allow the programmer to utilize specific output bits on a selected I/O channel to control external devices. There are 16 output bits available for this function. With SB8, the user can select which bit he wants to set by specification of the bit number. The setting of one of these output bits causes a corresponding binary voltage level change at the specified output terminal, and this can be used to close or open switches, start or stop experimental events, light indicator lamps, etc. SB11 allows the programmer to output a 16-bit binary voltage pattern with any simultaneous combination of "1"s and "0"s he chooses. This binary pattern is selected by including in the subroutine call the decimal equivalent of the binary number to be generated. Thus, more than one event can be controlled simultaneously.

SB12 and SB13 provide digital *input* information for program "sensing" of external situations. Thus, 16 binary voltage input terminals are available to the user, the status of which are acquired by either subroutine. SB12 transmits to the BASIC program the numerical equivalent of the input 16-bit binary voltage pattern. Because the status of these bits can be set by external events, the computer could use this information to make appropriate changes in the data processing or control programming.

SB13 is similar to SB12, except that only the status of a single specified input bit is determined. This subroutine is useful to the student because he need only specify a bit number in the call statement to check the status of a bit.

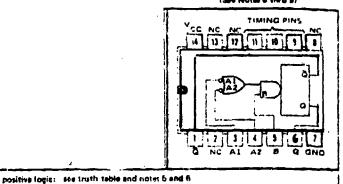

Timing and Synchronization. The most fundamental operation which must be accomplished by the PRTB system is the generation of a time base for all experimental functions. This is accomplished by the incorporation of a fixed frequency crystal clock (10 MHz) into the interface hardware. Also included is electronic countdown logic to scale the output clock pulses down to a usable frequency range for chemical experimentation (100 KHz to 0.01 Hz). The countdown logic can be modified under program control to select

any frequency within this which can be generated by a decadeand/or a 1,2,5-countdown sequence. The programmed clock output pulse train is then available to control the timing on the ADC, DAC, or any other external hardware. Also available simultaneously are synchronous clock pulses representing frequencies at the various stages of countdown. (These details are described in Section II,C.)

The clock is controlled by the PRTB software through subroutines SB1, SB2, and SB10. SB1 is the *initialization* subroutine. Through it the programmer specifies the clock frequency, within the limits outlined above. (SB1 is also used to specify the symbol assigned to the variable which will take on the values of the digital data acquired in SB3 or SB7.)

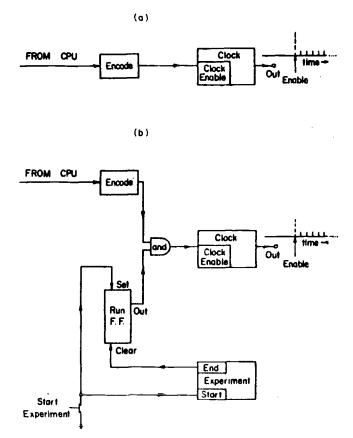

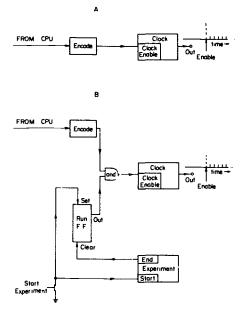

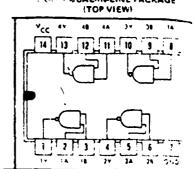

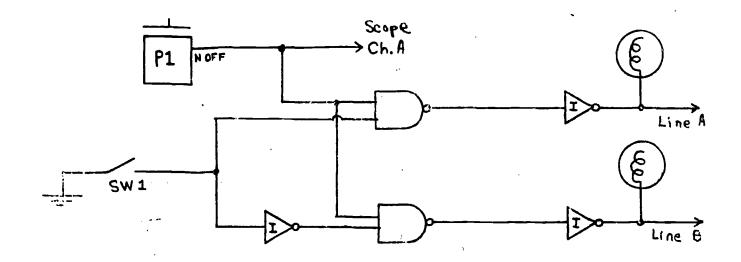

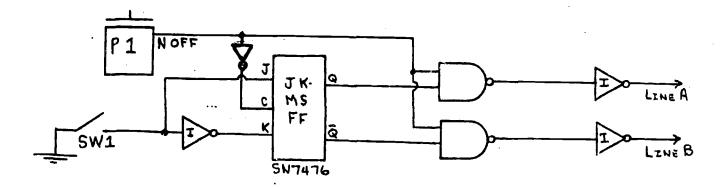

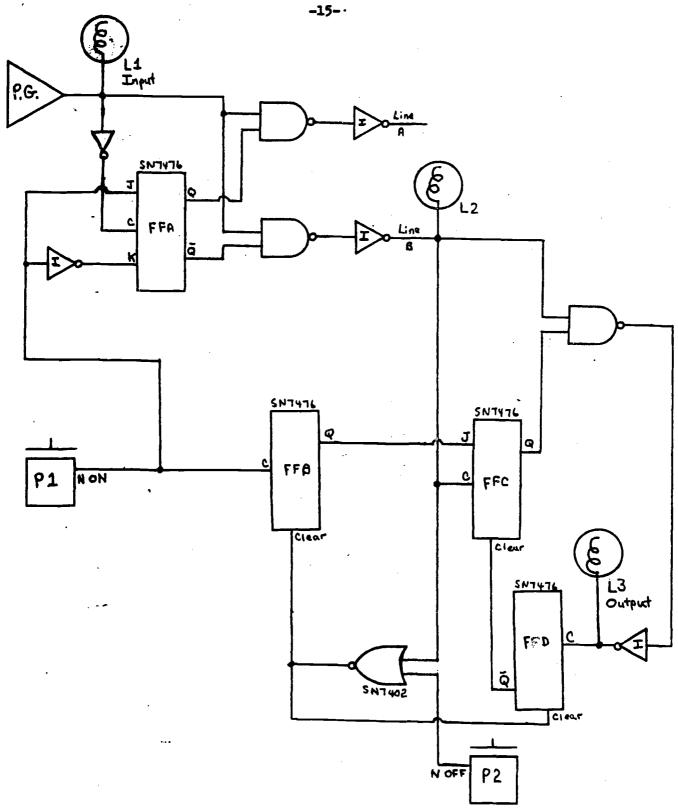

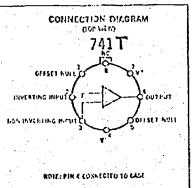

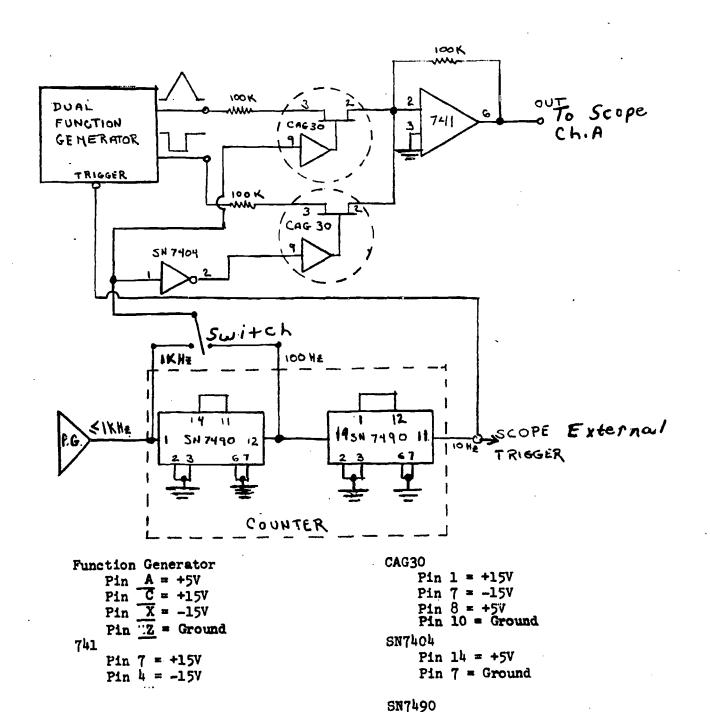

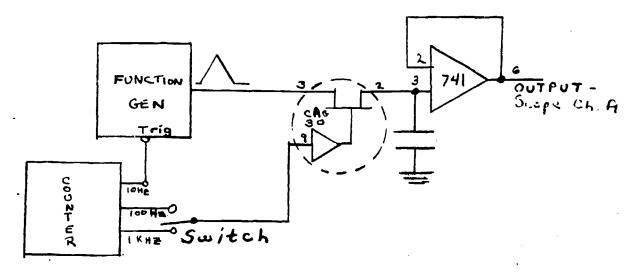

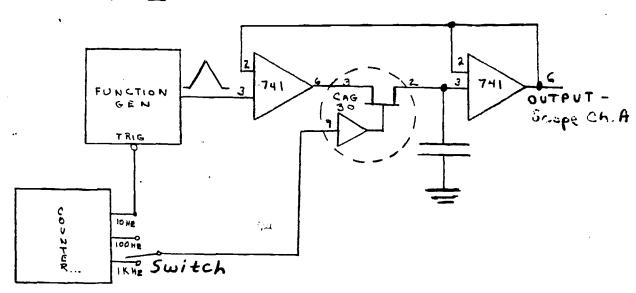

SB2 is called when the computer program decides that it is time to enable the clock. That is, an ENCODE bit is set to a "1" state on the data acquisition channel. This bit can be connected externally with a patchcord to the ENABLE terminal on the clock module (see Fig. 4a). Alternatively, the ENCODE bit may be brought to some external logic, the output of which will set the ENABLE clock input when other external events have occurred—like the start of the experiment. One possible external logic configuration is shown in Fig. 4b, where the ENCODE bit conditions one input of an AND gate. The other gate input is conditioned "TRUE" when the experiment has been initiated. The AND gate output will then enable the clock. At that point the countdown logic will be enabled and programmed clock pulses will begin to appear at the available outputs.

SB10 is called to disable the clock when the time base is no longer required. It simply "clears" the ENCODE bit on the data acquisition channel which has been used externally to enable the clock.

Another type of communication required between the experiment and computer is associated with *synchronization* between computer operations and external events. For example, if the computer has completed all preliminary program execution required before being able to accept experimental data, the user may choose to receive an output from the computer which may not only tell the experiment to start, but may also initiate external events associated with the experimental system. One subroutine available for this kind of operation is SB5. SB5 causes the output of an ENCODE bit on a selected I/O channel to change state (go to the "TRUE" level)

Fig. 4. Synchronization of clock output with computer and experimental events. (a) Direct computer control of clock enable input. (b) Clock enable controlled by AND gate output. Clock enabled when both computer command and experimental start are seen at AND gate inputs. The "RUN" flip-flop output follows the status of the experiment; it is set "true" when the experiment starts and "false" when the experiment ends. Thus, the clock is disabled when the experiment ends.

when SB5 is called. Then the computer waits within SB5 for an external event to occur which will cause a FLAC bit on the same I/O channel to change to a TRUE state. The subroutine detects this event and then allows the next sequential program statement to be executed. This next statement might conceivably be a call to SB2 which initiates data acquisition.

A simpler, but less precise, means of communication with the computer for the purpose of synchronization is provided by SB4. When this subroutine is entered, the computer simply waits until the operator flips a toggle switch corresponding to bit 6 on the computer console switch register. The computer then exits SB4 and executes the next program statement, which might be to call SB2 and start data acquisition.

Finally, a subroutine (SB6) is available which allows general-purpose timing functions. This routine simply waits for the FLAG bit to be set on the data acquisition channel, clears the FLAG, exits the subroutine, and the next sequential program statement is executed. The purpose of this subroutine is synchronization of program segments with the external time base. (Note that SB5 can be used, also, for general-purpose timing functions if the data acquisition channel is needed for other purposes. The user must simply connect the clock output to the FLAG input of the alternative I/O channel.)

#### C. Experimental

#### 1. Computer Instrumentation

The digital computer system used in this work was a Hewlett-Packard 2115A, equipped with 8 K core memory, high speed paper tape input, ASR/33 Teletype, a 16-bit 20 µsec DAC, and an interfaced Tektronix Model 601 oscilloscopic display. In addition, the computer has an interfaced data acquisition system and a general-purpose experimental interface capability. (These are described in detail below.) The complete computer system is mounted in a cabinet which has roll-around capability. The software used for laboratory on-line operation (PRTB) utilized the Hewlett-Packard BASIC compiler, Hewlett-Packard No. 201112A. This software is made available from the computer manufacturer. The program listings of the additions to the Hewlett-Packard BASIC compiler made here to implement PRTB are available from the author upon request.

#### 2. Data Acquisition and General-Purpose Interface Hardware

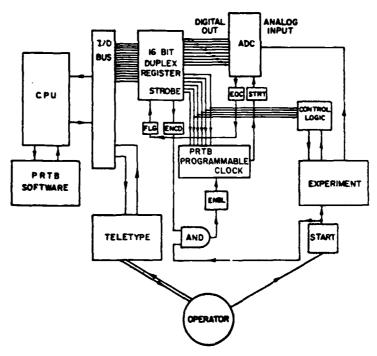

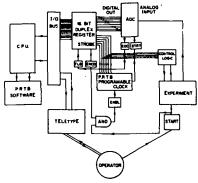

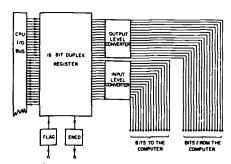

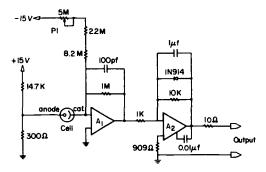

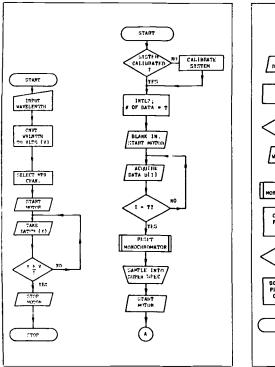

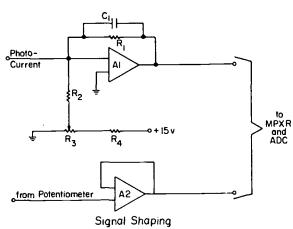

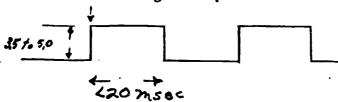

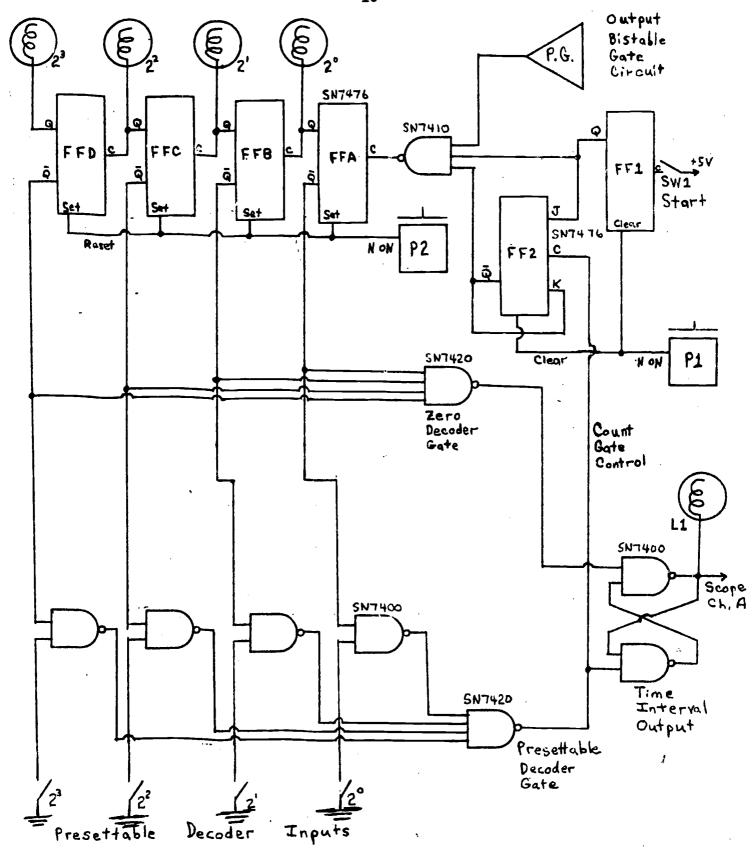

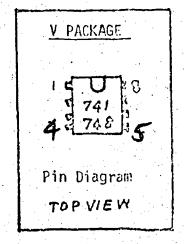

A schematic diagram of the data acquisition system operated in conjunction with PRTB is shown in Fig. 5. The analog-to-digital

Fig. 5. Typical PRTB experimental data acquisition setup. Previously undefined symbols include: I/O Bus, Input/Output hardware of the computer, one channel of which is used for data acquisition system; 16-bit duplex register, a Hewlett-Packard #02116-6195 16-bit duplex interface buffer register card, also providing output ENCODE command and input FLAG signal.

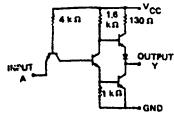

converter used in the data acquisition system was manufactured by Digital Equipment Corporation (DEC), Maynard, Massachusetts (No. C-002, 10-bit 33  $\mu$ sec conversion time, 0 to -10.23 V input range).

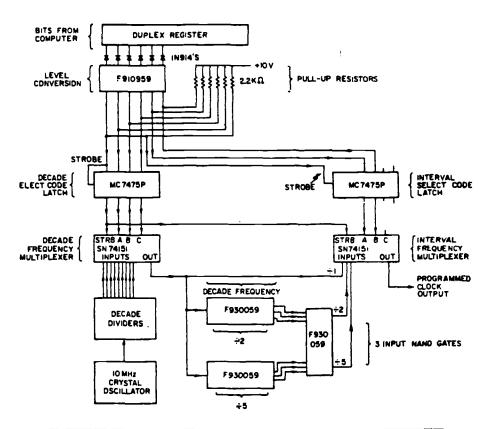

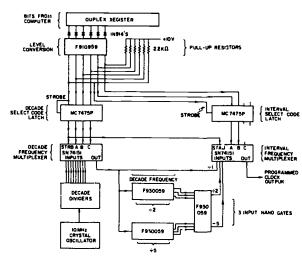

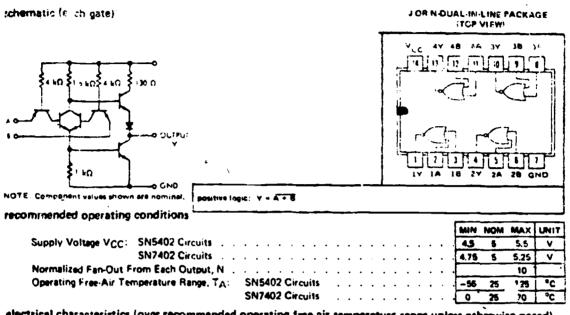

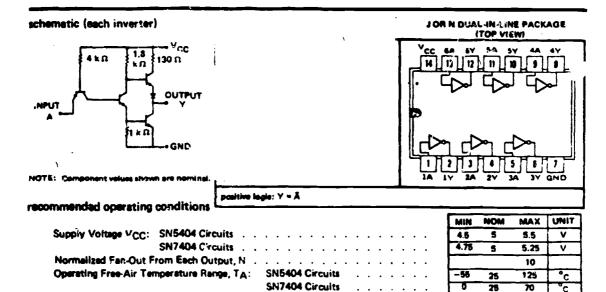

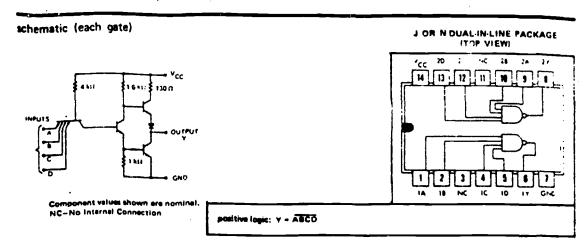

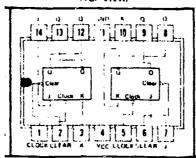

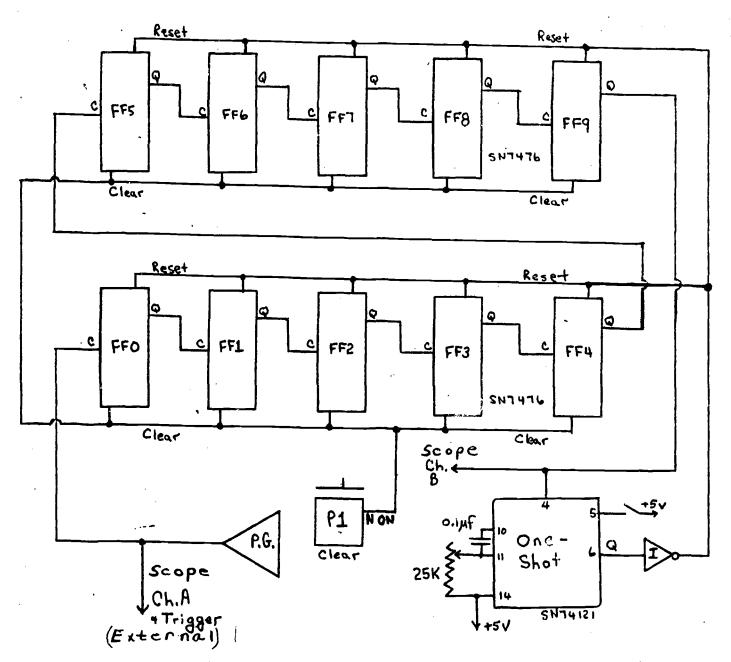

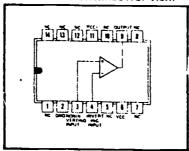

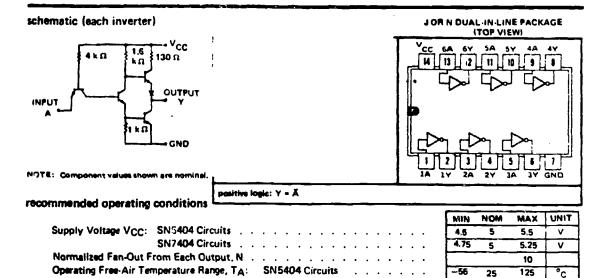

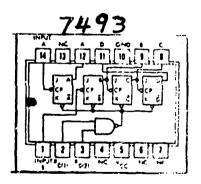

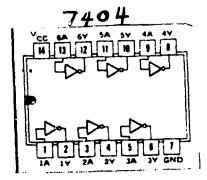

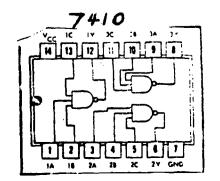

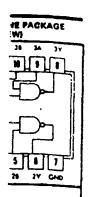

The programmable clock is constructed from a 10 MHz crystal-controlled oscillator scaled down to usable frequency ranges with medium-scale integrated circuit (MSI) programmable countdown logic. A schematic diagram of this module is given in Fig. 6, with a complete list of hardware components. Programmed clock pulses are available from 100 KHz to 0.002 Hz. Each decade frequency can be divided by 2 or 5. The specific frequency is selected by a 5-bit output word which is decoded in the clock module by two Texas Instrument SN74151 digital multiplexers. In addition to the pro-

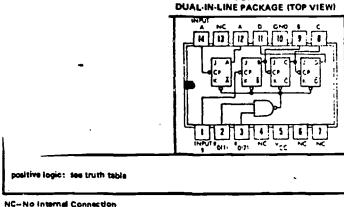

| Device No. | Manufacturer     | Description                                                      |  |  |  |

|------------|------------------|------------------------------------------------------------------|--|--|--|

| F910959    | Fairchild        | Hex inverter-six level converters, high<br>level to +4 to +20 V. |  |  |  |

| MC7475P    | Motorola         | Quad latch (4 bistable latches)                                  |  |  |  |

| SN74151    | Texas Instrument | Data selector/multiplexer                                        |  |  |  |

| F930059    | Fairchild        | 4-bit shift register                                             |  |  |  |

| F900359    | Fairchild        | Triple 3-input NAND gate                                         |  |  |  |

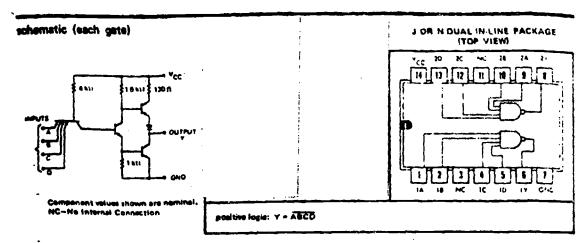

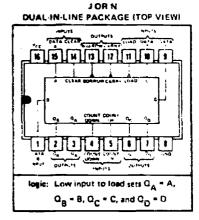

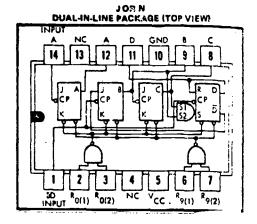

Fig. 6. Schematic diagram for PRTB programmable clock.

grammed output, each decade output from 1 MHz to 0.001 Hz is available externally by patchboard connection.

Also available on the data acquisition panel were an ENCODE output bit which could be set and cleared by the computer, and a FLAG input terminal to allow external setting of the FLAG bit

on the computer I/O channel used for data acquisition. The end-of-conversion (EOC) flip-flop of the ADC was normally connected to the FLAG input; however, it was possible to connect any appropriate externally generated signal to the FLAG input. Six bits of digital information could be transferred to or from the computer through the data acquisition panel using patchboard connections on the panel. Other generally useful functions available on the data

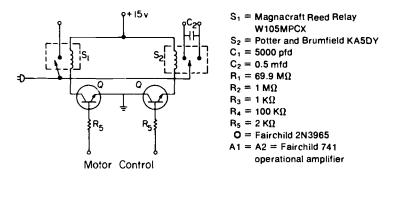

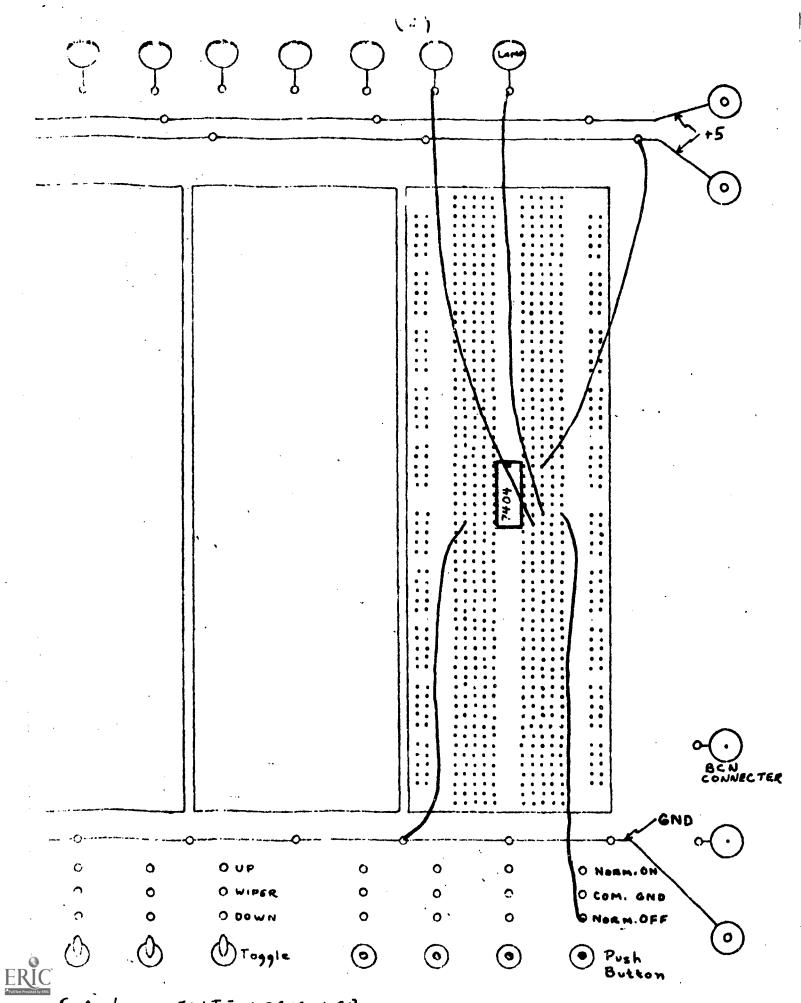

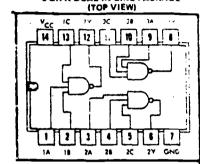

Fig. 7. View of general-purpose data acquisition and interfacing panels for PRTB system.

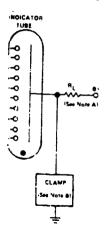

acquisition panel included patchboard connected to various logical devices such as 16 AND, OR, and NOT gates, four flip-flops, two one-shots, four analog switches, four relay drivers, a Schmitt trigger, a track-and-hold amplifier, six indicator lamps, and two push button switches with Schmitt trigger outputs. Figure 7 provides a view of the general-purpose data acquisition and interface panel used by the students. [See Malmstadt and Enke (1969) for a general discussion of characteristics of control logic nodules.] DEC R-series logic (Digital Logic Handbook, 1968). Flip-Chip cards and power supplies were used for logic functions. For interface design which required more sophistication or more logic elements than could be obtained on the data acquisition panel, a DEC patchboard R-series Logic Lab (Digital Logic Handbook, 1968) was available, Most experiments did not require interface hardware beyond that available on the data acquisition panel. All input and output to the computer were buffered with level conversion devices on the H.-P. 2115A system so that all external connections are compatible with DEC R-series positive logic (Digital Logic Handbook, 1968). DEC W601 and W510 level conversion cards were used.

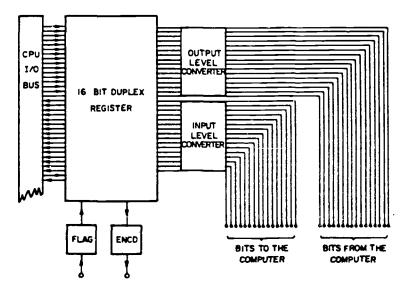

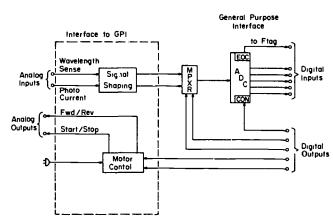

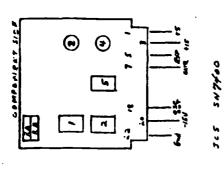

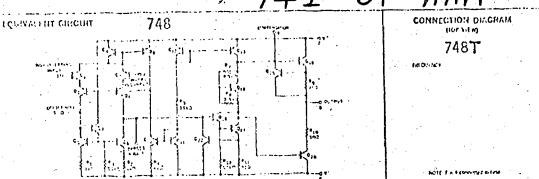

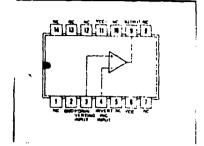

An interfaced digital I/O module was also available for generalpurpose digital communication between computer and experiment.

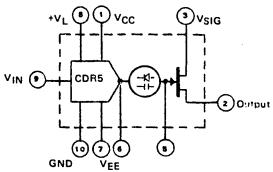

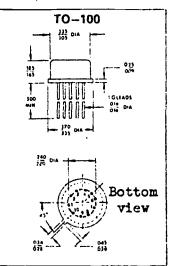

Fig. 8. Digital I/O interface module for PRTB.

32 S. P. Perone

The characteristics of this module are illustrated in Fig. 8. This digital I/O module was connected to a different I/O channel than the data acquisition panel. Thus, a separate independent ENCODE output and FLAG input were available through this module. The use of the digital I/O capability has been described above.

#### D. RESULTS AND DISCUSSION

#### 1. Evaluation of the PRTB System

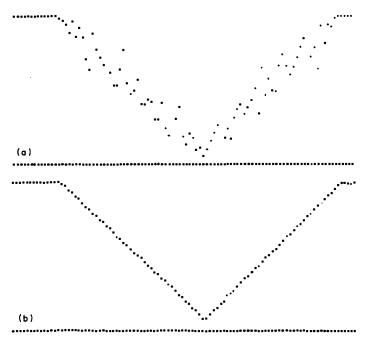

For the purpose of illustrating the capabilities of the PRTB software, the laboratory computer systems and software were tested with a synthetically generated experimental output which simulated typical experimental data. The illustration involved application of ensemble averaging to the analysis of an experimental output which provided a repetitive voltage waveform with superimposed large amplitude random noise. The waveform for the ensemble averaging experiment had a fundamental frequency the order of 10 Hz, with superimposed large amplitude random noise. The experiment was

```

PEADY

LIST

I PEM THIS PROGRAM IS AN ENSEMBLE AVERAGING ROUTINE--FOLLOW

PEM THE DIRECTIONS PRINTED OUT FTER PRESSING RUN. THE

REM FREQUENCY OPIGINALLY SPECIF ED IS 1000 HZ.

ID DIM X(100), Y(100)

20 LET F=1000

30 PRINT "THE # OF PTS EACH RUN =";

31 INPUT T

40 PRINT THE # OF PUNS =";

41 INPUT C

50 MAT Y=ZER

60 FOR I=1 TO C

70 CALL(1, X(1), F)

82 CALL(1, X(1), F)

83 CALL(1, X(1), F)

84 CALL(1, X(1), F)

85 CALL(1, X(1), F)

86 CALL(1, X(1), F)

87 CALL(1, X(1), F)

88 CALL(1, X(1), F)

89 CALL(1, X(1), F)

80 LET Y(J)=Y(J)+X(J)

110 NEXT J

120 NEXT I

200 FOP K=1 TO T

210 LET E=Y(K)/(C+10)

220 IF E>72 THEN 300

230 PRINT "+" 1 TAR(E); "+"

240 NEXT K

250 STOP

300 LET E=71

310 GOTO 230

```

Fig. 9. Program for ensemble averaging experiment.

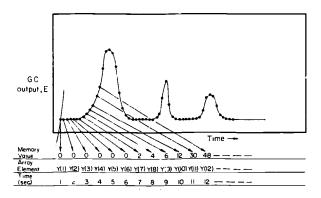

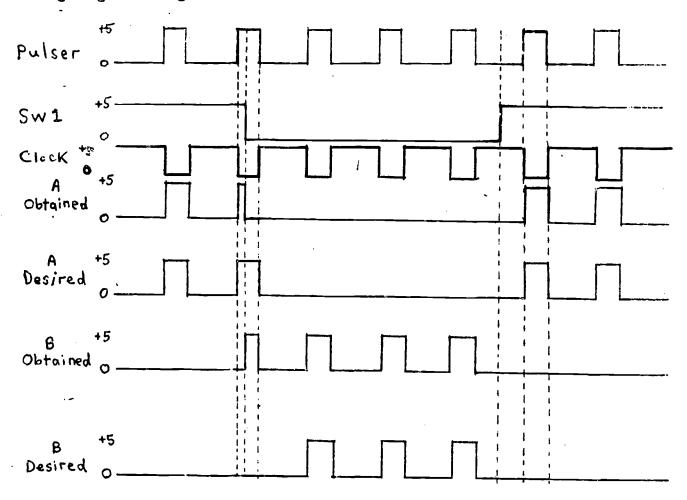

Fig. 10. Data from ensemble averaging experiment, plotted on teletype. (a) Original data (single cycle). (b) Data after 100 averaging cycles.

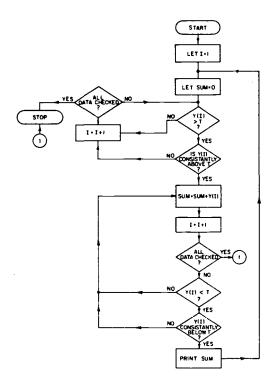

repeatable and could be triggered by computer output. The programming objectives included repetitive initiation of the experiment, synchronization of data acquisition with experimental output, and repetitive coherent summation of the digitized waveforms to accomplish ensemble averaging. Finally, when the experiment was completed, the averaged data were normalized and plotted on the teletype terminal. The computer program used is given in Fig. 9. Figure 10 shows the original output waveform and the results of ensemble averaging.

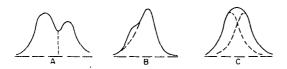

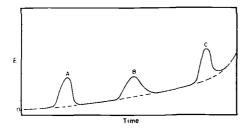

The above experiment is executed by students in the laboratory. Other experiments include data acquisition and processing with synthetic experimental signals as described in Section I; gas chromatography (Perone and Eagleston, 1971); kinetic enzymatic analysis; differential kinetic analysis; and computer-controlled spectrophotometry. These and other experiments will be described in detail elsewhere (Klopfenstem et al., 1972).

#### 2. Observations

It can be seen from the above examples that actual implementation of the PRTB system is relatively straightforward. Moreover, for all its simplicity, considerable experimental measurement capability exists in the system.

The requirements for implementing the PRTB system in the undergraduate laboratory include the following.

- (1) An introduction to the BASIC language for computational purposes. This requires 1 to 2 hours of lecture time. It also requires that students have access to the laboratory computer (or other computer facilities providing BASIC capability) during the first few weeks of the semester to handle homework and laboratory computations.

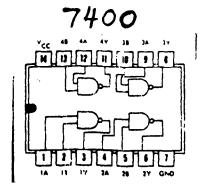

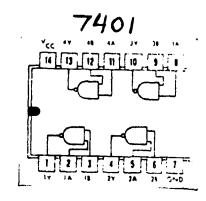

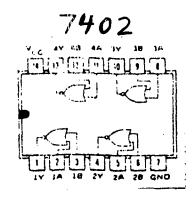

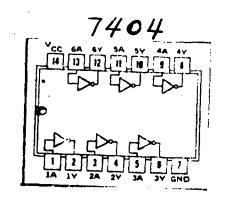

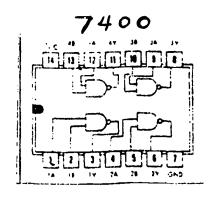

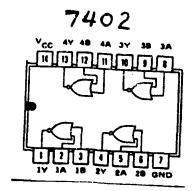

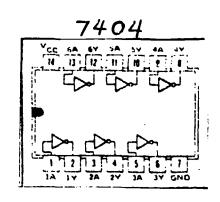

- (2) An introduction to the fundamental concepts of on-line computer operation. This requires about 6 hours of lecture. These introduce the student to the whole field of on-line computer applications and the technological details with which they must be familiar to implement this approach in the laboratory. These details include an introduction to the fundamentals of digital logic, timing, and synchronization. This involves the discussion of simple gates (AND, OR, NOT), the flip-flop, the one-shot, and the analog switch. The functional characteristics of these devices, as well as of analog-to-digital and digital-to-analog converters and voltage amplifiers, for interface design are defined. No attempt is made to provide a rigorous understanding of the electronic principles or detailed circuitry for these devices. The emphasis is on the student's being able to recognize and use the fundamental characteristics of these devices for interface design.

- (3) Finally, the actual laboratory assignments are carried out. These assignments are designed to introduce the student to the analytical technique and methodology, just as would be done in the absence of the laboratory computer instrumentation. In addition, the student is expected to utilize the on-line computer as a data acquisition and data processing tool.

The final question to be considered here is what specific benefits are derived by the student from the use of the laboratory computer in on-line experimentation. First of all, the student is obviously exposed to state-of-the-art technology in laboratory experimentation. Second, the student is encouraged to use more rigorous data

processing approaches than previously feasible for laboratory assignments. Third, the student becomes keenly aware of the factors that limit and define experimental accuracy and precision. (This is a direct result of the fact that the computerized experiments can be re-run conveniently with modified parameters, and the results can be evaluated rapidly with the laboratory computer.) Fourth, the student is able to make a first-hand comparison of the effectiveness of conventional and computerized laboratory methodology. And, finally, the student's interest in the science of quantitative che nical experimentation is strongly stimulated.

#### Acknowledgments

The contributions over several years of the National Science Foundation for the development of the short course and the graduate and undergraduate educational programs are gratefully acknowledged. Pertinent NSF grants include GP-8528, GP-8677, GJ-190, GJ-403, and GJ-428.

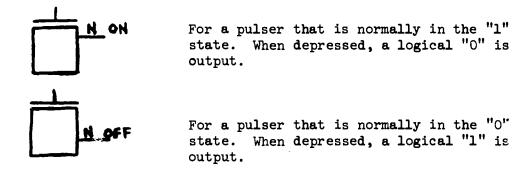

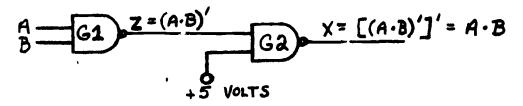

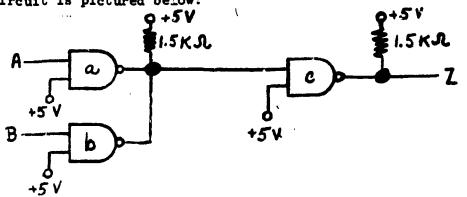

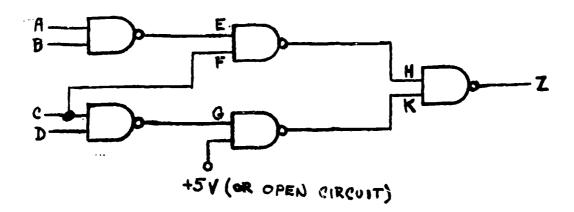

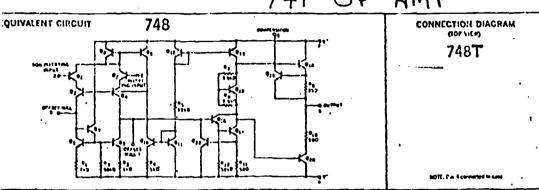

The author also wishes to acknowledge the invaluable assistance of Dr. David O. Jones who provided the design concepts for instructional interface modules, Professors H. L. Pardue and Stuart P. Cram who have taught the digital logic section of the short course, and Professor J. W. Amy who has provided instrumentation support and advice.