#### ED 031 274

By-King, Paul Allen, Jr.

A Novel Solid State Character Generator.

Massachusetts Inst. of Tech., Cambridge, Electronic Systems Lab.

Spons Agency-Council on Library Resources, Inc., Washington, D.C.

Report No-ESL-TM-386

Pub Date Jun 69

Note-109p.

EDRS Price MF-\$0.50 HC-\$5.55

Descriptors-\*Display Systems, Information Systems, \*Input Output Devices, \*Man Machine Systems, \*Media Technology, \*Orthographic Symbols

Identifiers-Project Intrex; \*Sinusoidal Scan

This thesis describes a character generator which was built for a refreshed cathode-ray tube (CRT) display and demonstrates the feasibility of displaying high quality dot-matrix characters using the low-band width sinusoidal scan. The CRT used was a low-cost entertainment-quality television tube, and hence had a very poor deflection band width. Settling time for the CRT system was about 10 microseconds. A technique was developed and made operational which displayed a whole dot-matrix character in a time which was less than one settling time of the display system. It is an application of the existing technique called sinusoidal scan to the display of dot-matrix characters. A data compression technique was also invented and implemented. It allows up to a 75 percent reduction in the size of the stored character tables which are normally associated with dot-matrix displays. The technique involves a digital algorithm which fills in dots between given dots in a matrix. This technique proved quite effective in producing good quality characters, and is economically attractive. (Author/RM)

#### ESL-TM-386

#### A NOVEL SOLID STATE CHARACTER GENERATOR

by

Paul Allen King, Jr.

June, 1969

Research Grant from Council on Library Resources

This Technical Memorandum consists of the unaltered thesis of Paul Allen King, Jr. submitted in partial fulfillment of the requirements for the degree of Master of Science at the Massachusetts Institute of Technology in June, 1969. The research reported herein was made possible through the support extended the Massachusetts Institute of Technology, Project Intrex, at the Electronic Systems Laboratory under a research grant from the Council on Library Resources, Inc. This grant is designated as M.I. T. DSR Project Number 27808.

# U.S. DEPARTMENT OF HEALTH, EDUCATION & WELFARE OFFICE OF EDUCATION

THIS DOCUMENT HAS BEEN REPRODUCED EXACTLY AS RECEIVED FROM THE PERSON OR ORGANIZATION ORIGINATING IT. POINTS OF VIEW OR OPINIONS STATED DO NOT NECESSARILY REPRESENT OFFICIAL OFFICE OF EDUCATION POSITION OR POLICY.

Electronic Systems Laboratory

Department of Electrical Engineering

Massachusetts Institute of Technology

Cambridge, Massachusetts 02139

# A NOVEL SOLID STATE CHARACTER GENERATOR

bу

PAUL ALLEN KING, JR.

S.B., Massachusetts Institute of Technology (1969)

SUBMITTED IN PARTIAL FULFILIMENT OF THE

REQUIREMENTS FOR THE DEGREE OF

MASTER OF SCIENCE

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June, 1969

| Signature  | of        | Author   | tment of | Q                                   | Clem    | - //w    | w.        |       |

|------------|-----------|----------|----------|-------------------------------------|---------|----------|-----------|-------|

|            |           | Depar    | tment of | Electrics                           | l Engir | neering, | May 23,   | 1969  |

| Certified  | Ъу        |          |          | Jame                                | 1K.     | Robe     | 19L       |       |

|            |           |          |          |                                     |         | Thesi    | s Superv  | isor  |

| Accepted 1 | <b>bу</b> |          | `        | , and an add when the last well the | 1       |          |           |       |

|            |           | Chairmar | Denerta  | ental Con                           | mittee  | on Grad  | luate Stu | dents |

# A NOVEL SOLID STATE CHARACTER GENERATOR

bу

#### PAUL ALLEN KING JR.

Submitted to the Department of Electrical Engineering on May 23, 1969 in partial fulfillment of the requirements for the Degree of Master of Science.

#### ABSTRACT

This thesis describes a character generator which was built for a refreshed cathode-ray tube display. The CRT used was a low-cost entertainment-quality television picture tube, and hence had a very poor deflection bandwidth. Settling time for the CRT system was about 10µs.

A technique was developed and made operational which displayed a whole dot-matrix character in a time which was less than one settling time of the display system. It is an application of the existing technique called sinusoidal scan to the display of dot-matrix characters.

A data compression technique was also invented and implemented. It allows up to a 75 percent reduction in the size of the stored character tables which are normally associated with dot-matrix displays. The technique involves a digital algorithm which fills in dots between given dots in a matrix. This technique proved quite effective in producing good quality characters, and is economically attractive.

THESIS SUPERVISOR: James K. Roberge

TITIE: Assistant Professor of Electrical Engineering

#### ACKNOWLEDGMENT

The research reported herein was made possible through the support extended the Massachusetts Institute of Technology, Project INTREX, at the Electronic Systems Laboratory under a research grant from the Council on Library Resources, Inc. and designated as M.I.T. DSR Project Number 27808.

The author wishes to express his sincere thanks to Professor James K. Roberge for his gu dance during the course of this work. Thanks are also due to Alfred DiPillo, who built the circuits involved, to Mrs. Arlene Zamagni, who typed the manuscript, and to Norman Darling who drew the figures.

# TABLE OF CONTENTS

| CHAPTER I.   | THE PROBLEM                                            | page<br>9  |

|--------------|--------------------------------------------------------|------------|

|              |                                                        | 9          |

| 1.1          | Intrex System                                          | 11         |

| 1.2          | Character Generator for the Console                    |            |

| 1.3          | Advantage of Sinusoidal Scan                           | 12         |

| 1.4          | Scanning Character Generators                          | 13         |

| 1.5          | Weaknesses of Scanning Generators                      | 19         |

| CHAPTER II.  | DISPLAYING DOT-MATRIX CHARACTERS USING SINUSOIDAL SCAN | 26         |

| 2.1          | Segmenting a Sinusoid                                  | 26         |

| 2.2          | Sinusoid Distortions                                   | 27         |

| 2.3          | Horizontal Double Frequency                            | 27         |

| 2.4          | Correcting Vertical Distortion                         | 30         |

| CHAPTER III. | CHARACTER SMOOTHING                                    | <b>3</b> 5 |

| 3.1          | Size of Matrix                                         | <b>3</b> 5 |

| 3.2          | Smoothing Algorithm                                    | <b>3</b> 9 |

| 3.3          | Interpolation Algorithm                                | 40         |

| 3.4          | Simple Interpolation                                   | 41         |

| 3.5          | Strong Interpolation                                   | 45         |

| CHAPTER IV.  | HARDWARE IMPLEMENTATION                                | 48         |

| 4.1          | Data Section                                           | 48         |

| 4.1.1        | Simple "Formattor"                                     | 48         |

| 4.1.2        | Column Interpolation                                   | 50         |

| 4.1.3        | Simple Interpolation                                   | 52         |

| 4.1.4        | Order Reversing                                        | 59         |

| 4.1.5        | Strong Interpolation                                   | 60         |

| 4.2          | Timing Chain                                           | 71         |

ERIC A diabat Pondata I, tilic

|             |                                                  | page |

|-------------|--------------------------------------------------|------|

| CHAPTER IV. | HARDWARE IMPLEMENTATION (Con't.)                 |      |

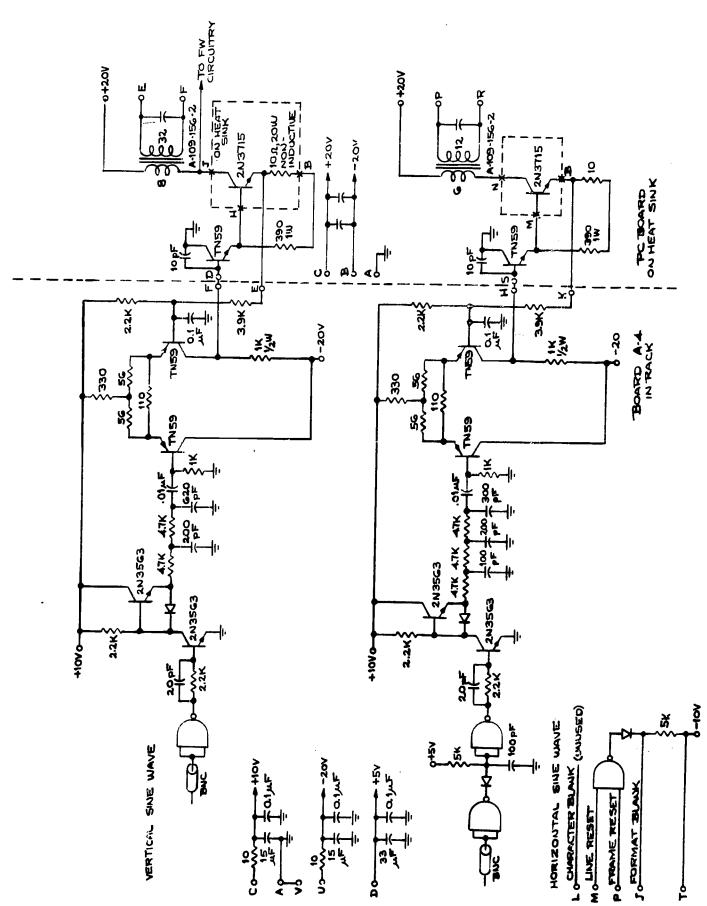

| 4.2.1       | Horizontal Timing                                | 73   |

| 4.2.2       | Phase-Locked Loop                                | 74   |

| 4.2.3       | Vertical Deflection Circuits                     | 78   |

| 4.2.4       | Vertical Timing                                  | 83   |

| 4.3         | Read-Only Memory                                 | 85   |

| 4.3.1       | Memory of the Scanning Generators                | 85   |

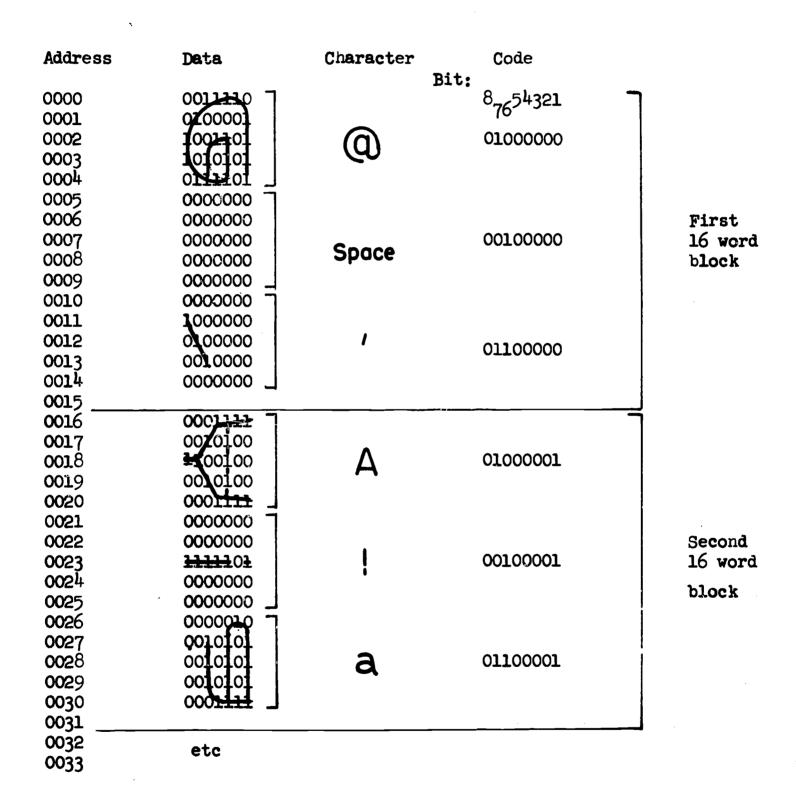

| 4.3.2       | Storing Skeletal Matrices                        | 86   |

| 4.3.3       | Modified ASCII Code                              | 87   |

| 4.3.4       | Address Map                                      | 88   |

| 4.3.5       | Key Word                                         | 89   |

| CHAPTER V.  | CONCLUSION                                       | 94   |

| 5.1         | Comparison of Dot-Matrix and Scanning Generators | 94   |

| 5.2         | Evaluation of the Interpolation Algorithms       | 99   |

## TABLE OF FIGURES

| CFAPTER I.   | THE PROBLEM                                            | page       |

|--------------|--------------------------------------------------------|------------|

| 1.1          | Sinusoidal Scan                                        | 14         |

| 1.2          | Monoscope                                              | 16         |

| 1.3          | Flying Spot Scanner                                    | 17         |

| 1.4          | Complete System                                        | 18         |

| 1.5          | Jitter Mechanism                                       | 50         |

| 1.6          | Omission Mechanism                                     | 20         |

| 1.7          | Fidelity of Scanned Characters                         | 22         |

| 1.8          | Mask Designed for a Specific Scan Pattern              | 24         |

| CHAPTER II.  | DISPLAYING DOT-MATRIX CHARACTERS USING SINUSOIDAL SCAN |            |

| 2.1          | Order of Displaying Dots                               | <b>2</b> 8 |

| 2.2          | Matrix Displayed Using Sinusoidal Scan                 | 29         |

| 2.3          | Family of Scan Patterns                                | 31         |

| 2.4          | Derivation of Maximum Frequency                        | 33         |

| 2.5          | Matrix Displayed with Corrected Scan                   | 34         |

| CHAPTER III. | CHARACTER SMOOTHING                                    |            |

| 3.1          | Typical Dot-Matrix Characters                          | 36         |

| 3.2          | Most Probable Patterns in a 9 by 7 Matrix              | <b>3</b> 8 |

| 3.3          | Type of Display Points                                 | 41         |

| 3.4          | Simple Interpolation                                   | 44         |

| <b>3.</b> 5  | Moving the Vertex of an Oblique Angle                  | 46         |

| <b>3.</b> 6  | Examples of Interpolation                              | 47         |

| HAP | rer iv. | HARDWARE INTERPOLATION PAGE                               | e          |

|-----|---------|-----------------------------------------------------------|------------|

|     | 4.1     | Dot-Matrix Generator Block Diagram                        | 49         |

|     | 4.2     | Digitally Controlled Switch                               | 51         |

|     | 4.3     | Shift-Register Converter                                  | 51         |

|     | 4.4     | Effect of Rule No. 1 and No. 2                            | 53         |

|     | 4.5     | Interpolator for Rule No. 1 and No. 2                     | 53         |

|     | 4.6     | Interpolator for Rules No. 1 - No. 4                      | 54         |

|     | 4.7a,b  | Effect of Rules No. 1 - No. 4                             | 56         |

|     | 4.7c    | Contents of Shift Registers                               | 57         |

|     | 4.7d    | Patterns in the Window Matrix for Simple Interpolator     | r 58       |

|     | 4.8     | Bit-Reversing Shift Registers                             | 61         |

|     | 4.9     | Shift-Register Network for Rules No. 1 through No. 5      | 63         |

|     | 4.10    | Data Present in Interpolator                              | 64         |

|     | 4.11    | Undefined Values in Window Matrix                         | 64         |

|     | 4.12    | Window Matrices Definition                                | 66         |

|     | 4.13    | Logic Diagram of Shift-Register Network                   | 67         |

|     | 4.14    | Patterns in the Window Matrix for Strong<br>Interpolation | 69         |

|     | 4.15    | Interpolation Logic Diagram                               | 70         |

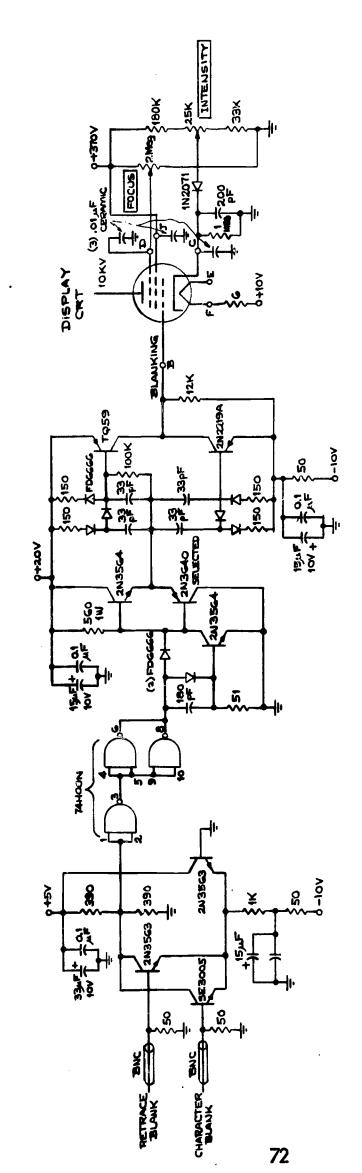

|     | 4.16    | Blanking Amplifier                                        | 72         |

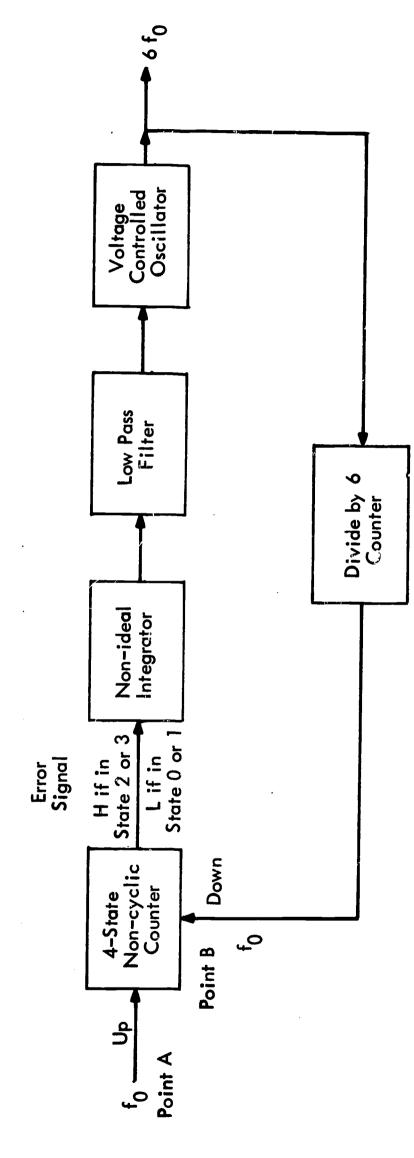

|     | 4.17    | Phase-Locked Loop                                         | <b>7</b> 5 |

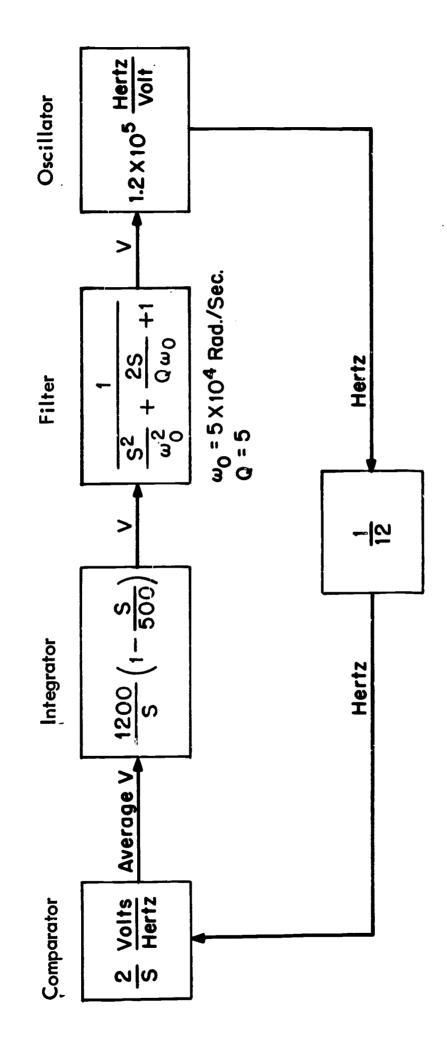

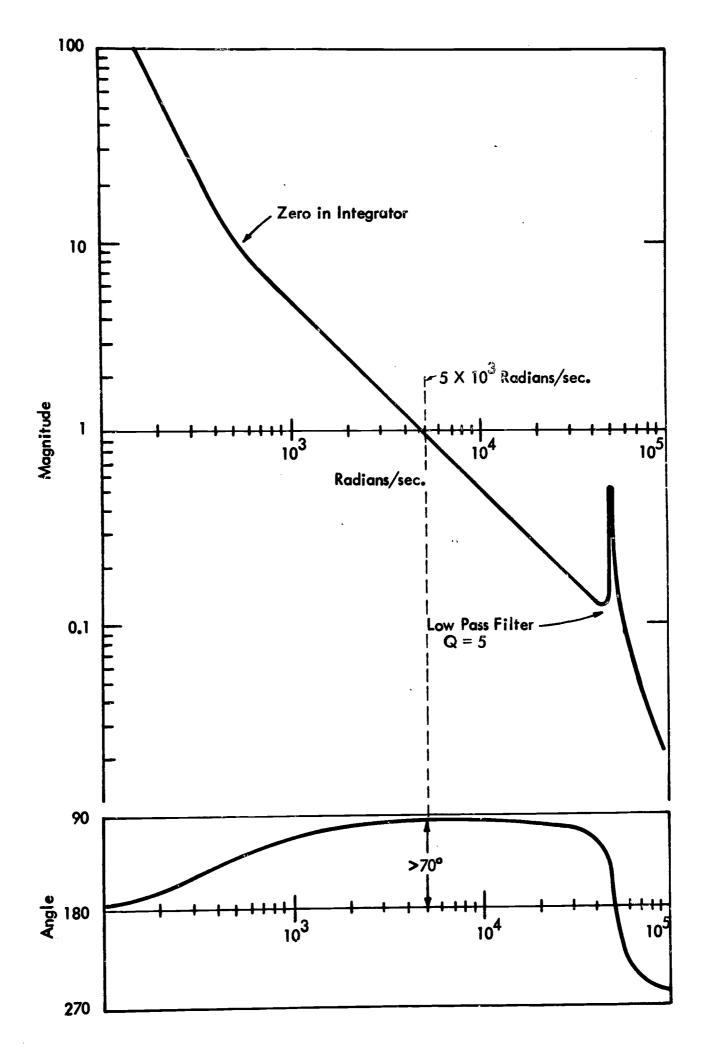

|     | 4.18    | System Response of Phase-Locked Loop                      | <b>7</b> 7 |

|     | 4.19    | Open Loop Frequency Response                              | <b>7</b> 9 |

|     | 4.20    | Horizontal Generator                                      | 80         |

|     | 4.21    | Tuned Amplifiers                                          | 81         |

|     | 4.22    | SHIFT Oscillator                                          | 84         |

|     | 4.23    | Contents of ROM                                           | 90         |

| 1   | 4.24    | ROM-Interpolator Interface                                | 92         |

ERIC Fut has Provided by ERIC

| CHAPTER V.  | CONCLUSION                                       | <u>p</u> q          | age |

|-------------|--------------------------------------------------|---------------------|-----|

| 5.1         | Intrex Console                                   |                     | 95  |

| 5.2         | Dot Matrix Character Generator:<br>Interpolation | Simple and Strong   | 96  |

| 5•3         | Monoscope with Interlace                         |                     | 97  |

| 5.4         | Monoscope without Interlace                      |                     | 98  |

| 5•5         | Dot Matrix Character Generator:                  | Strong Interpolator | 100 |

| 5.6         | Dot Matrix Character Generator:                  | Simple Interpolator | 101 |

| <b>5.</b> 7 | Dot Matrix Character Generator:                  | No Interpolator     | 102 |

| 5.8         | Sample Text Using Dot-Matrix                     |                     | 105 |

| <b>5.</b> 9 | Sample Text Using Monoscope                      |                     | 106 |

#### CHAPTER I

#### THE PROBLEM

#### 1.1 INTREX SYSTEM

ŧ

ERIC

The primary objective of Project Intrex is to evolve a functional design for an automated library system that could become operational at M.I.T. and elsewhere during the 70's. The core program encompasses four major areas of activity:

- 1. The Augmented Catalog The development of a computer-assisted bibliographic search system.

- 2. Guaranteed Full Text Access The development of a system to make the full text of every document available at remote stations.

- 3. Network Integration The investigation of methods of exchanging information between libraries.

- 4. Fact Retrieval The development of a system for retrieving data from very large files.

Of these, only the Augmented Catalog will be considered here. There are three areas of activity with the Augmented Catalog program:

- 1. Augmented-Catalog Inputting

- 2. Storage and Retrieval

- 3. The Display Console

In the Augmented Catalog Inputting phase, a large base of literature cataloged according to author, title, subject, etc. is being developed and translated into digital form. In the Storage and Retrieval phase, catalog input data is being transferred into disk-file storage. Programming techniques are being developed for rapid computer searches, through the liter-

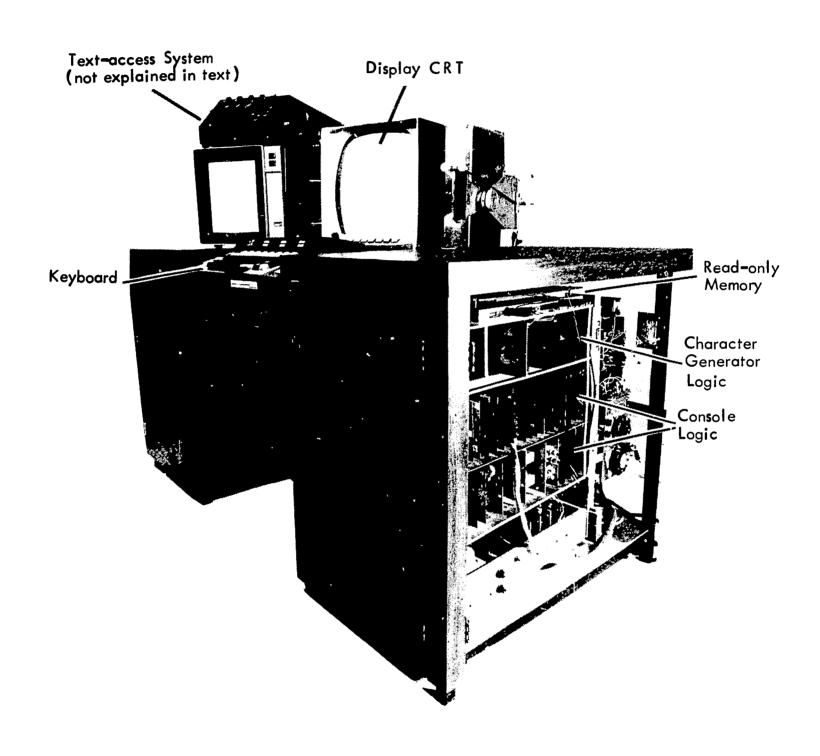

The Display Console is a special purpose on-line computer terminal that allows the catalog user to communicate with the processor and to direct the computer searches in an interactive mode. The Display Console consists of a keyboard, with which the user sends information to the computer, and a display device, by which the computer conveys information to the user. It is the Display Console, in a sense, that makes the Augmented Catalog useful. If the user had to communicate with the computer by means of punched cards and computer printout, there would be little point in utilizing a computer search: he could probably find the necessary information more quickly by the conventional methods in a library.

In operation, the user types in appropriate descriptor words, subject heading, or author names. The computer then searches the literature base for articles categorized under these headings and indicates to the user the number of articles found. If this number is too large, the user can reduce it by typing in additional constraints. When the search is complete, the user may elect to have titles or abstracts of the articles displayed at the console.

The display element at the console is a large screen cathode-ray tube (CRT). This type of output medium is desirable because it eliminates the long and noisy delays associated with mechanical typewriter terminals. Considerations of system requirements led to the existing display system which has the following specifications:

- 1) The display capacity is approximately 1700 characters -there are 31 lines of 56 characters per line.

- 2) The character set includes both upper and lower case

English letters (the standard 96 character ASCII code).

- 3) The character set also includes an additional 96 symbols including Greek letters and mathematical symbols.

- 4) The character set is alterable, so that characters or character styles can be changed.

- 5) The Display Console must be economically reproducible.

- 6) The display system has the provision for selective erasure, to facilitate editing and making corrections.

This last feature imposes a heavy burden on the console electronics. Since storage tubes cannot be selectively erased, a conventional cathoderay tube had to be employed. Information must be constantly refreshed on the face of the tube, one frame after another, in a manner similar to a television set. There are problems associated with regenerating the 1700 character display rapidly enough to prevent noticeable flicker.

## 1.2 CHARACTER GENERATOR FOR THE CONSOLE

ERIC

The character generator is one of the most important parts of the console. The characters are the only thing the user sees: If the characters are not clear, all the elegant features of the system are lost because they cannot be read easily. Two previous attempts at generating readable characters have resulted in only mediocre characters. This thesis involves a third character generator which was designed to give much better performance. To understand the design, it is first necessary to understand the Intrex display system. The following paragraphs explain how the current configuration was chosen, and what effects that structure has on the possible design of a character generator.

The console system consists of a small computer and a magnetic drum which services up to ten indivdual display consoles. The local computer

services the demands of the ten consoles. It is capable of reading a console keyboard, reading and writing on the magnetic drum, and communicating with the time-sharing computer. All information displayed on the CRT of each console is stored on the magnetic drum. Thus the cost of refresh storage and centralized data processing equipment is amortized over ten consoles. The data on the drum passes through the character generator located at the console and is displayed on a screen in the following manner: A format generator produces a raster of over 1700 character positions every 17 milliseconds. The generator is synchronized to the magnetic drum so that one complete revolution of the drum corresponds to one complete raster on the CRT. Consequently, drum addresses correspond to specific positions on the CRT screen, resulting in a savings of hardware. 3 Note that this scheme requires the character generator illuminate a whole character on the CRT screen every time the drum sends one (every 8.5 µs). The character generator is constantly a slave to the codes coming from the drum.

#### 1.3 ADVANTAGE OF SINUSOIDAL SCAN

ERIC

Much of the expense of a large capacity refreshed alphanumeric display is taken up by the CRT and its associated deflection circuits. 1 To reduce this cost, an inexpensive television picture tube is being used. The tube is magnetically deflected, with a deflection-system settling time of about 10µs. This means that the beam cannot be moved quickly to an arbitrary point on the screen since time has to be allowed for the beam to settle. The current solution is to selectively intensify a fixed scan pattern. The pattern, which was chosen because it is immune to the settling time of the beam, is generated by adding a sine wave to the vertical deflection signal,

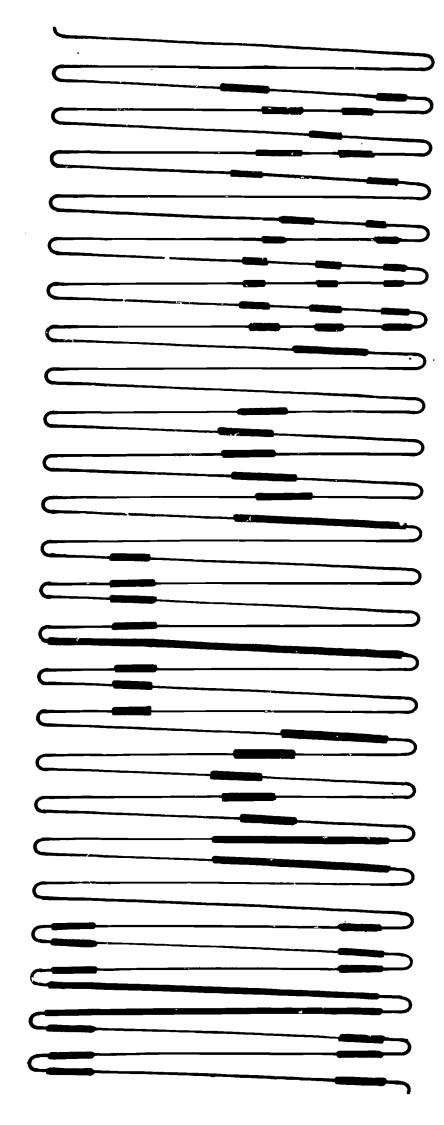

and applying a ramp to the horizontal deflection. Both patterns can be implemented easily with hardware because they both have very narrow bandwidth. Figure 1.1 shows the pattern with the correct intensification to produce the word "Intrex".

The vertical scan pattern is immune to settling time because in the sinusoidal-steady-state analysis, a time delay is merely a phase lag. This lag, if it is constant, can be corrected in theory by an appropriate phase advance of the signal to the deflection circuit, although in practice, it is effected by a phase delay in an alternate path. The ramp, which is applied to the horizontal deflection, sweeps a full line of 56 characters without stopping. Since ample time (about 20µs) is allowed at the beginning of each line for the beam to stabilize its transient response, limited horizontal deflection bandwidth is tolerable.

It is quite compelling to stay with this sinusoidal scan pattern for its simplicity and ease of implementation. It is also the only effective way in which one can display characters with deflection circuits that require  $10\mu s$  to settle. Thus vector generators (which have variable scan patterns) and the type of dot matrix generators which rely on digital spot positioning are truly not feasible.

Constrained to using the sinusoidal scan pattern, there are two major ways to generate the necessary blanking signal. One way involves electrically scanning an image of the character set which has been physically constructed in the device. The other method, described here, stores the intensity patterns in a digital read-only memory. The patterns for both are, of course, displayed on the sinusoidal scan.

#### 1.4 SCANNING CHARACTER GENERATORS

There are three types of scanning generators, the flying spot scanner,

Fig. 1.1 Sinusoidal Scan

the monoscope, and the vidicon tube. Much work has been done at Intrex by Paul McKenzie to develop the flying-spot scanner, 5 and by Professor James K. Roberge and the author to develop the monoscope. The vidicon tube was not developed because of its short operational lifetime. The following paragraphs explain each type of scanning generator and present the causes for their partial failure.

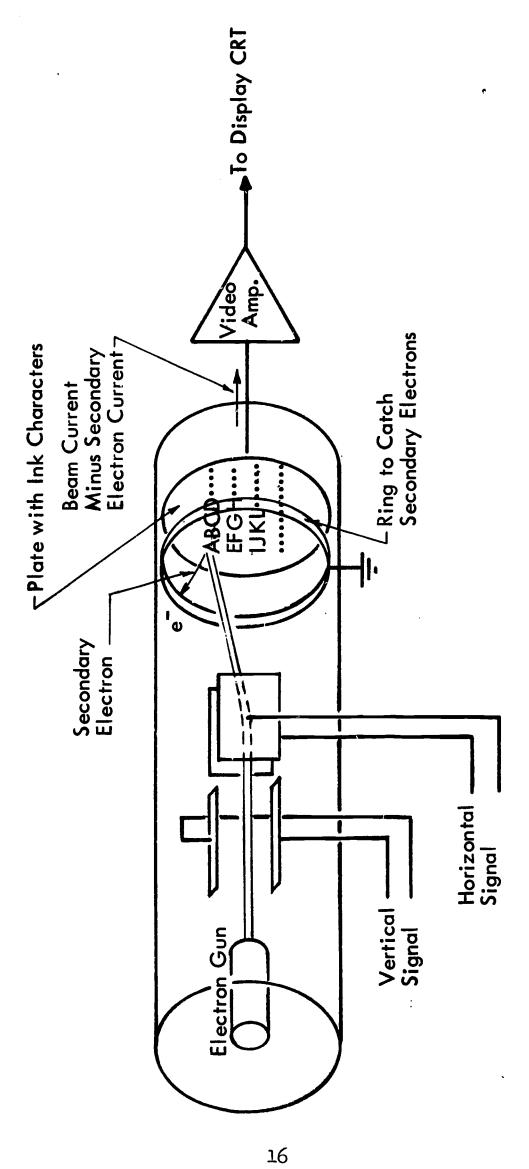

The monoscope generates the intensification pattern from ink characters on a metal plate. An electron beam is electrostatically deflected to the desired spot in the desired character. If the beam strikes ink, the secondary emission of the plate is less. A ring collects the secondary electrons—the current they produce is amplified and used as the video signal. The process is shown diagrammatically in Figure 1.2.

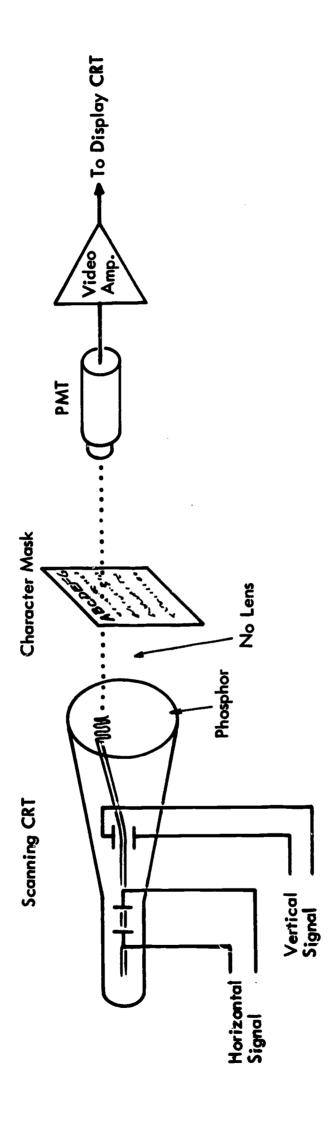

A flying-spot scanner in its simplest form, consists of a small electrostatically deflected CRT, a Photo Multiplier Tube (PMT), and a character mask between them. (See Figure 1.3.) The beam is directed to the desired position of the appropriate character, and a spot of light is produced on the phosphor, directly behind the character. If the position of the character is clear, light is picked up by the photo multiplier tube. The PMT signal is amplified and is used as the blanking signal for the display tube.

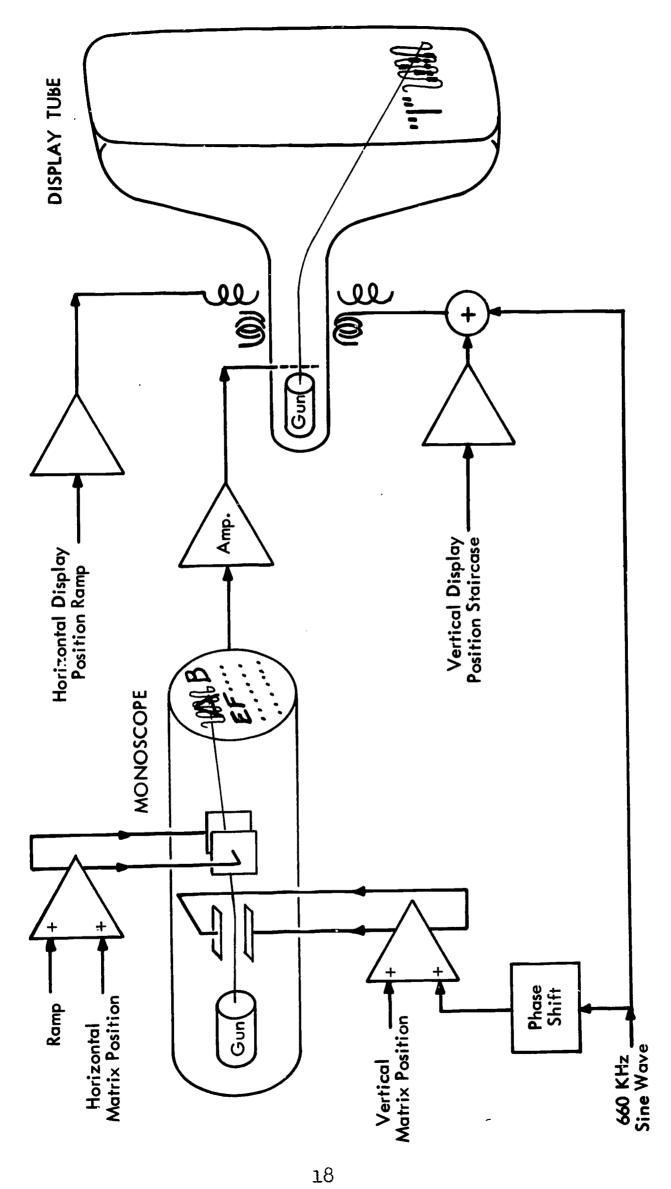

The video signal from either generator is used to form characters on the display CRT in the following manner. The character code from the drum directs the beam in the scanning generator to the desired character. At the same time, the beam of the display CRT is positioned where the character is to be illuminated. (See Figure 1.4.) The sinusoidal scan pattern is formed concurrently on both the scanning generator and the

Fig. 1.2 Monoscope

Fig. 1.3 Flying Spot Scanner

Fig. 1.4 Complete System

display CRT. Throughout the scan, the coordinates of both beams are the same, relative to the starting point of the scan. The video signal which is produced from the scanning generator is used as the blanking signal for the display. Consider the monoscope system for example.

Wherever the monoscope plate has an ink spot, there is less secondary emission and less current in the collector ring. This signal is amplified to produce a voltage which intensifies the beam at the spot corresponding to the position of the ink on the monoscope character. Thus every dark area (on the monoscope plate) which is traversed by the beam produces a corresponding bright area on the display screen. Characters are transferred by the scan from a position on the mask to a position on the screen.

The characters generated by the scanning generator tend to flicker.

If the beam passes too close to the edge of the character, it may or may not intensify during that scan. (See Figure 1.5.) Magnetic fields bend the electron beam of the character generator and change the relative position of the character. Thus a scan line which falls just on the edge of a character might be pushed off the edge and not intensify the display. Any power supply ripple or noise which finds its way into the deflection input or the anode of the generator tube will have the same shifting effect.

The shifting will cause one element of the character to flicker on and off.

The effect can be quite annoying since some of the pickup is due to the 60 cycle power line frequency. Because the refresh rate is 57 cycles, the noise will beat with the refresh rate to produce a 3 cycle per second flicker.

Noise in the video amplifier may boost a marginal signal over the threshold. The monoscope in particular has a low level output (lmV) and

Fig. 1.5 Jitter Mechanism

Fig. 1.6 Omission Mechanism

thus noise can be a problem. Since some of the noise is correlated with the 60 cycle line frequency, 3 cycle beating occurs.

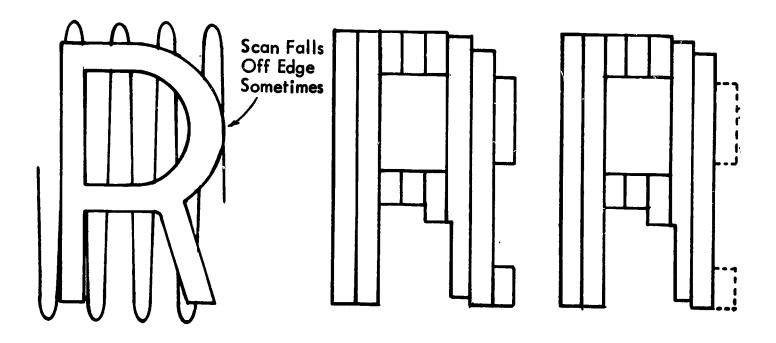

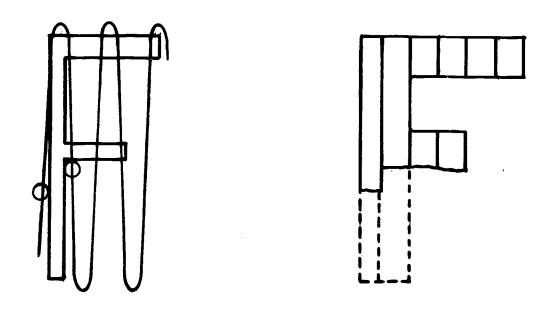

There seems to be another inherent weakness in scanning generators. The character set for any scanning generator must be constructed so that good characters will result no matter what scan pattern is used, or how it is positioned over the character. It is possible to have a coarse scan pattern in which two consecutive scan lines straddle some vertical feature of a character (e.g. the vertical bar of the letter "F" as in Figure 1.6). The result is that the vertical feature would not be displayed. This symptom is noticed when the monoscope is used to generate characters on the display console.

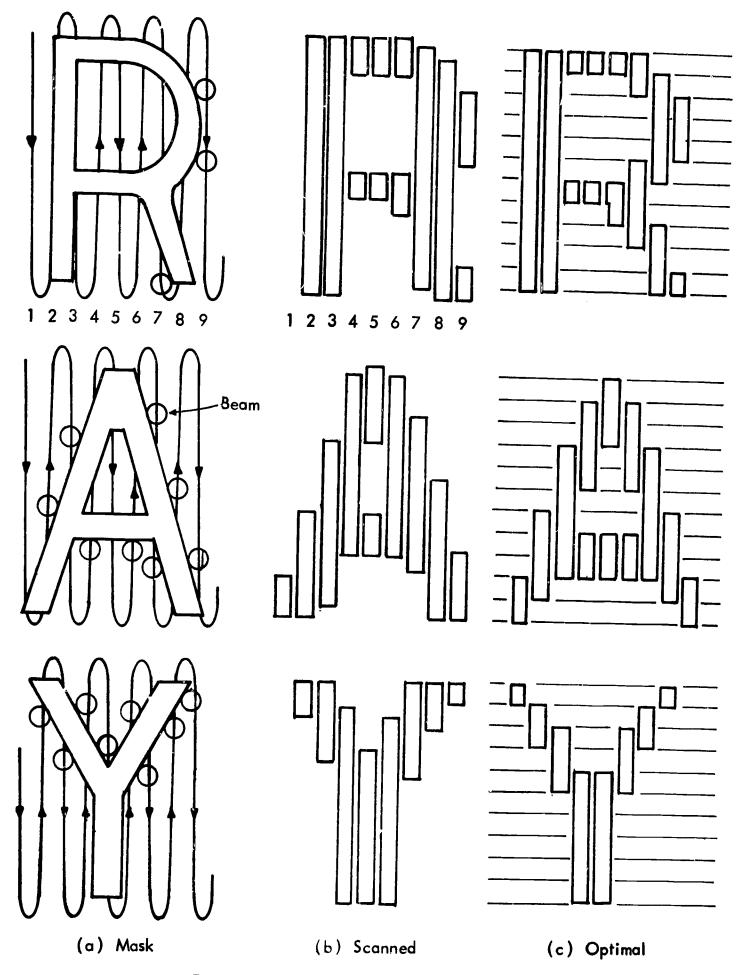

The usual adjustment which one makes when the above omissions occur is to brighten the scanning beam. This has the effect of making the scanning spot larger (as well as increasing the signal to noise ratio). The larger spot causes less precise scanning information. Many little details of the letter, such as corners and curves, are filled in by the larger beam. Figure 1.7 shows the letters "R", "A", and "Y" as they appear on the character mask with the sinusoidal pattern superimposed. Circles indicate the beam diameter. This diameter is chosen so that an intensify signal is sent to the display if the beam is closer than this diameter to an edge. Figure 1.7b shows the display produced by the scan of Figure 1.7a. Figure 1.7c shows an intensify pattern which was chosen to produce the most readable characters possible. It seems apparent that operated in this manner, the scanning generators do not always generate the optimum blanking signal.

The persistence of the phosphor on the flying-spot scanner degrades

Fig. 1.7 Fidelity of Scanned Characters

the image in a similar manner. The moving spot has a tail of glowing phosphor which makes the spot appear to be shaped like a comet.

One might try to custom tailor the character set to the particular scan pattern used. Figure 1.8 shows the mask characters with choppy edges to compensate for the distortion caused by finite beam size. The problem with this idea is that there is no mechanism for positioning of the beam over the character set. Beam position is a function of anode and accelerating voltages, magnetic fields in the tube, and amplifier gains and offsets. In addition, since the basic timing for the Intrex display is derived from the magnetic drum which varies speed slightly, the phase and amplitude of the sine wave used for the sinusoidal scan varies. Thus the pattern is not constant.

The display pattern is actually alternated between two sine waves 180° out of phase. The idea is similar to interlacing on a television, and is necessary to achieve enough resolution to produce readable characters. Yet if the two scans produce different intensities for the same general area, an annoying 30 cycle flicker is produced.

Digitally stored images do not have these disadvantages because all processing is done digitally. One problem which does exist is that transitions are allowed to occur only at specified places in a sweep of the sine wave. This limitation is not present in the scanning generators, which can make an intensity transition at any place in a scan. Yet both methods, the image scanning and the digitally stored, do limit the horizontal resolution to the number of lines scanned. Thus the limited vertical resolution of the dot pattern might not be as critical as supposed. Note that the "optimum" characters of Figure 1.7 were actually generated

Fig. 1.8 Mask Designed for a Specific Scan Pattern

from a 9 by 11 digital matrix. In addition, the digital generator is fast enough to display more sine waves per character. Thus the horizontal resolution is actually better than the scanning generator.

#### CHAPTER II

### DISPLAYING DOT-MATRIX CHARACTERS USING SINUSOIDAL SCAN

The digitally-stored character generator offers tremendous possibilities for Project Intrex. MOS read-only memories are becoming available, and should be economically feasible before any large-scale production of the console is undertaken. As argued in the previous chapter, and demonstrated in Chapter 5, digitally stored images produce better characters than scanning generators do.

The design of the character generator was strongly biased by the necessity to display the matrix using the sinusoidal scan pattern compatible with the Intrex console. In this chapter, the features of the sinusoidal scan relevant to the design will be discussed.

One essential feature of this type of scanning is that it is a fixed scan pattern which does not change from character to character. The only way in which two characters can be made to look different on the screen is to intensify the beam in different portions of the pattern.

#### 2.1 SEGMENTING A SINUSOID

The following observation allows one to plot a matrix using the sinusoidal scan: A sine wave can be crudely divided into display sections and adjoined curved sections. Where the display region is defined to end and the curved region begins is a subjective question, and depends on the arguments to be developed. The display region includes all zero-crossings where the second derivative of the sine wave is zero, and thus it is reasonably straight. This linear display region can be segmented by the character generator into discrete equal intervals of time. Each interval

corresponds to one dot of the matrix, and is intensified if that dot is on. Note that line segments, not points, are displayed on the CRT. The beam does not stop moving to display a dot.

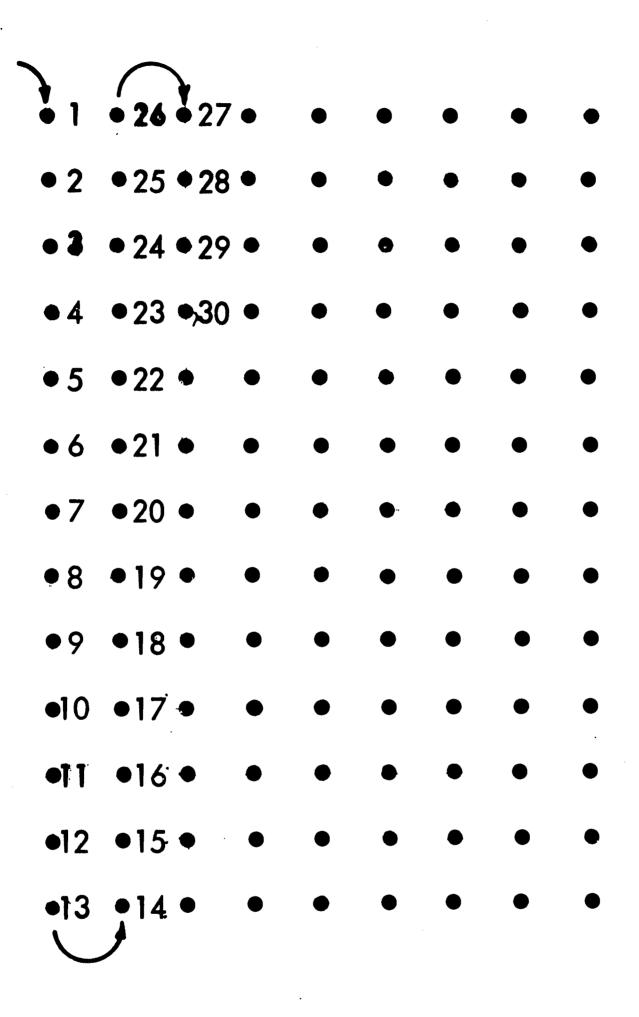

One column of a matrix can be displayed in each display region of the sine wave. An <u>m</u> column matrix can be displayed in m/2 cycles of the sine wave since one cycle has 2 linear regions. Figure 2.1 shows a 13 by display matrix with some of its points numbered in the order in which they will be displayed using the sinusoidal scan.

#### 2.2 SINUSOID DISTORTIONS

There are two characteristics of a sine wave which tend to distort

the squareness of a matrix displayed in the above manner. First, adjacent

display regions do not have the same slope, and thus they are closer together in either the top or the bottom of the scan. Therefore the horizontal

distance between two dots varies in the displayed matrix. Secondly, the

sine wave moves more slowly near the top and bottom in its curved sections.

The dots tend to get bunched up near the top and bottom of the scan, and

spread out in the center, causing the vertical distance between two points

to vary. The magnitude of these aberrations are a function of how much of the

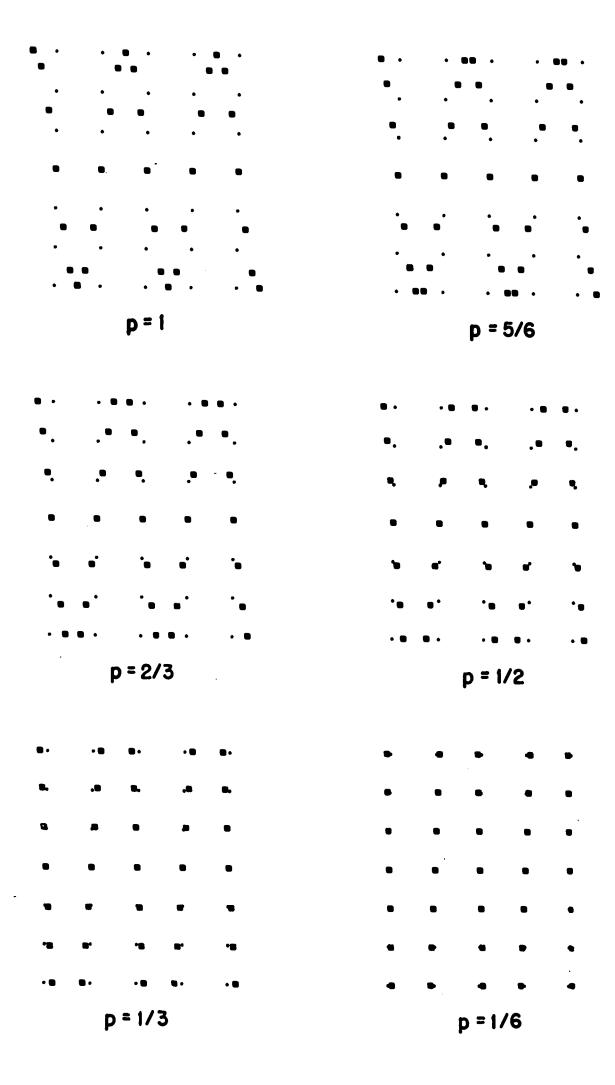

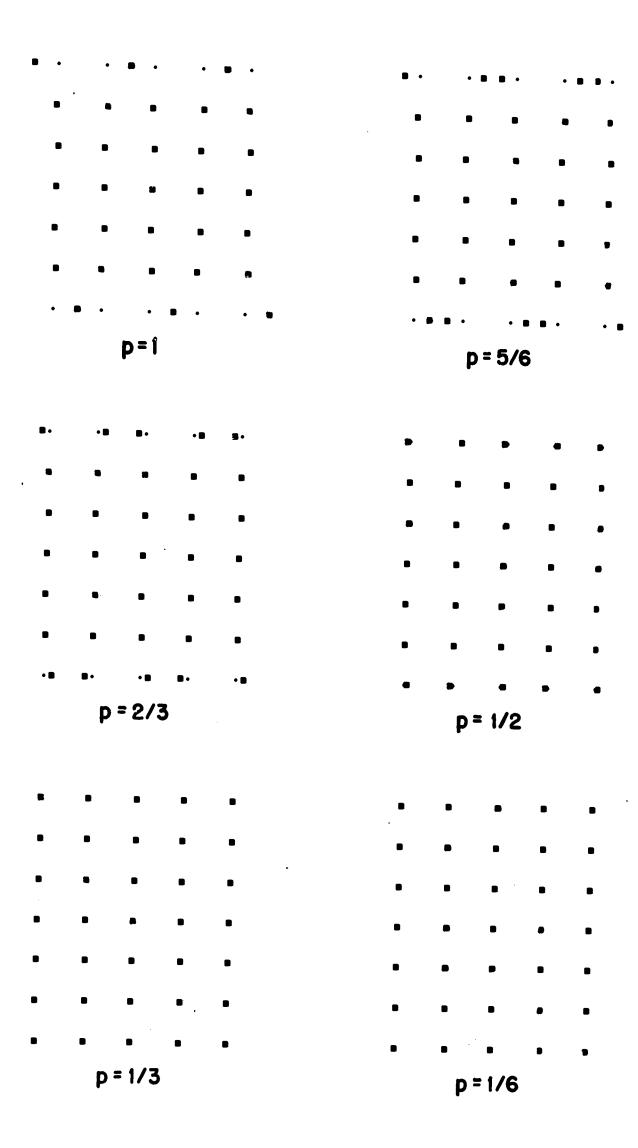

sine wave is used to plot the matrix. Some 7 by 5 matrices are shown in

Figure 2.2 as they would appear on the CRT screen for various values of p,

the fraction time used for display. The squares represent the actual

position used for display, and the dots are arranged in a rectangular grid

for reference.

#### 2.3 HORIZONTAL DOUBLE FREQUENCY

The first of the distortions can be reduced significantly. The solution is to change the scan pattern slightly by superimposing another sine wave onto the horizontal ramp signal. If the horizontal sine wave is twice

Fig. 2.1 Order of Displaying Dists

Fig. 2.2 Matrix Displayed Using Sinusoidal Scan

amplitude, the scan pattern produced will have display regions which are almost vertical. Figure 2.3 shows the parametric curves generated by:

$$x = \sin(\omega t)$$

$$y = t + a \cdot \sin(2\omega t + b)$$

A family of curves is plotted for various values of a and b. The waves in each column have the same values of a, the amplitude, and the waves in each row have the same value of b, the phase. One very desirable scan along with many poor ones can be produced.

It should be noted in passing that these patterns have little to do with a two-termed Fourier expansion of a square wave. That expansion requires a sine wave of three times the fundamental to be added to the vertical signal. The undesirable result of this addition is that the beam has twice the velocity in its "linear" regions. This doubles the required operating frequencies of the generator.

## 2.4 CORRECTING VERTICAL DISTORTION

The vertical distortion can also be reduced. The most obvious solution is to use only the center portion of the sine wave where the beam velocity is relatively constant. The major problem is that it forces the operating frequency of the character generator to be higher. If one plots an m by n matrix in  $8.5\mu s$  using the fraction p of the sine wave to display, then the frequency  $f_1$  at which the dots must be displayed is given by:

$$f_1 = \frac{m \cdot n}{p \cdot (8.5 \mu s)}$$

Frequency is inversely proportional to the fraction of time used to scan, p. Consider displaying a 13 by 9 display matrix. If p is assumed to be 2/3, f is 20MHz. Since the matrix with p = 2/3 does have substantial vert-

Amplitude -Best Pattern

Fig. 2.3 Family of Scan Patterns

ical aberrations, consider reducing p to 1/3. This doubles the display frequency to 40MHz, out of the range of ordinary logic.

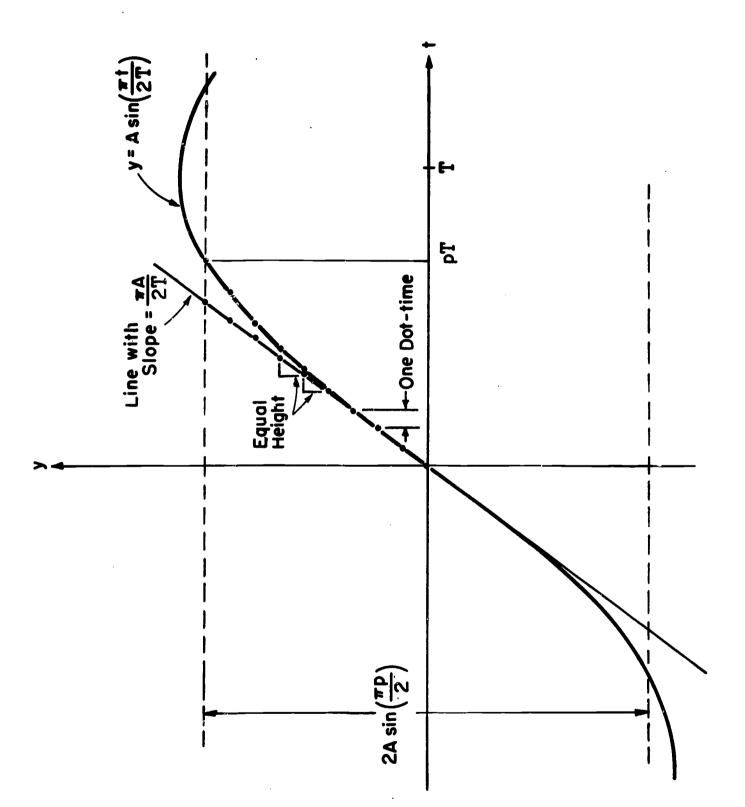

A better solution to the vertical distortion problem is to divide each linear region into segments of equal <u>length</u> on the CRT screen. Thus the time to plot each dot is not constant throughout a scan. Figure 2.4 is used in the derivation of the maximum frequency at which dots are displayed. Assume the matrix is displayed using a fraction p of the time in each cycle. Then the height of the displayed region is  $2 \cdot A \cdot \sin(\pi p/2)$ . Assume for the moment that the scan was not a sine wave, but a ramp whose velocity was the maximum vertical velocity of the sine wave. This maximum is d/dt of  $A \cdot \sin(\pi t/2T)$  evaluated at  $t = n_{T}$  and is  $\pi A/2T$  (distance per time). The rate necessary to display m dots on a ramp of length  $2 \cdot A \cdot \sin(\pi p/2)$  is given by:

$$f_2 = \frac{\pi \cdot m}{4 \cdot T \cdot \sin(\pi p/2)} = \frac{\pi \cdot m \cdot n}{2 \cdot \sin(\pi p/2) \cdot (8.5 \mu s)}$$

This is also the maximum rate of display of dots for the sinusoidal scan, because the number of dots per vertical distance is the same, and the maximum slope is the same. As would be expected, flapproaches f2 when p becomes small and thus the vertical distortion vanishes.

In this section, a scan pattern has been developed which requires very simple deflection circuitry, and is capable of displaying reasonably square dot matrices quickly.

Figure 2.5 shows the same set of 7 by 5 matrices as does Figure 2.2, except the vertical and horizontal corrections have been applied. For values of p up to 2/3, the distortion is negligible, and does not affect the quality of the characters generated.

The following section will explain the circuitry which intensifies the portions of the scan pattern necessary to form a character.

$\mathcal{J}_{i_{0}}^{d_{k_{0}}}.$

Fig. 2.5 Matrix Displayed with Corrected Scan 34

### CHAPTER III

### CHARACTER SMOOTHING

### 3.1 SIZE OF MATRIX

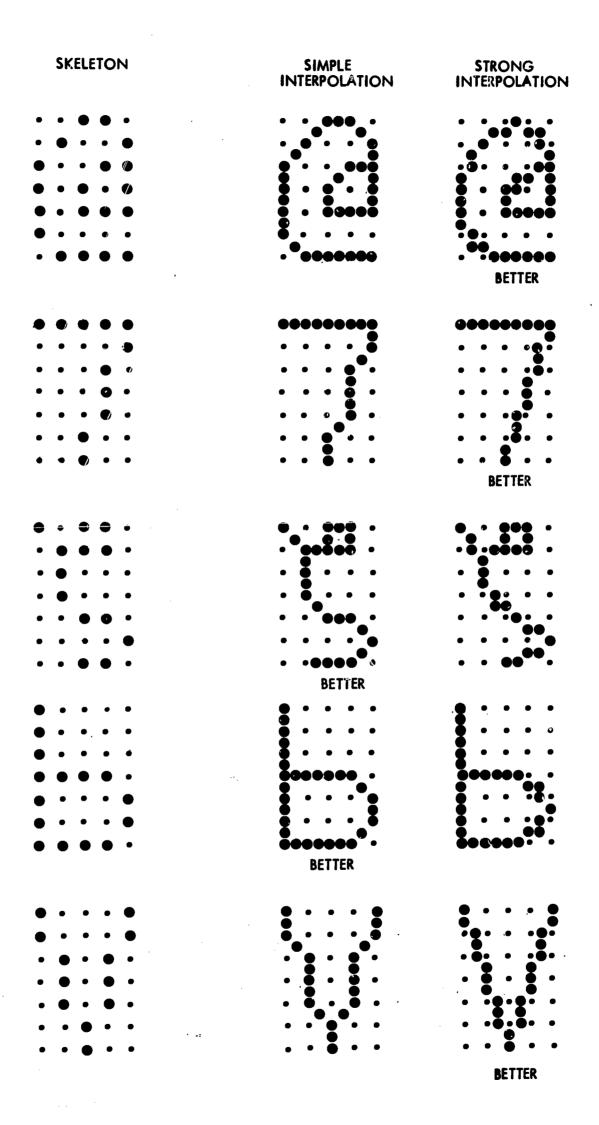

The quality of the digitally stored image is strongly dependent on the number of points displayed per character. It is assumed that the information about the shape of each character is stored in a dot matrix.

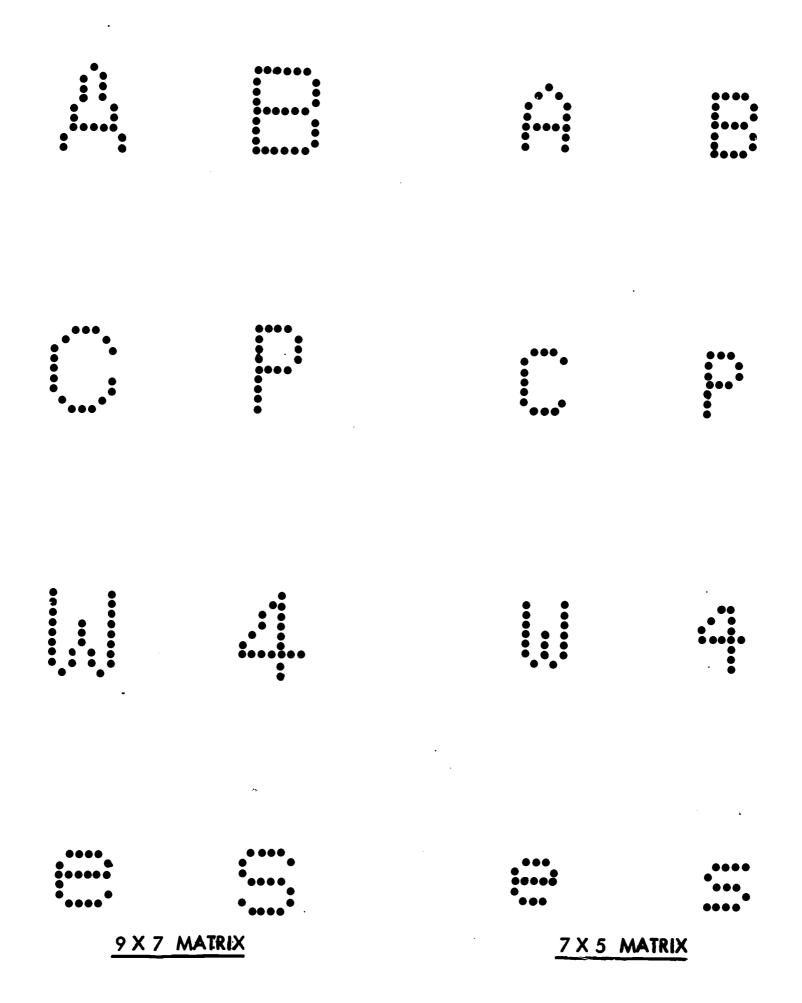

As shown in Figure 3.1, a 7 by 5 dot matrix gives fair quality capital letters, while a 9 by 7 matrix gives good upper and lower case letters.

Because complicated Greek letters are desired, and because the users of the console will not be used to dot-like characters, better than the 9 by 7 must be generated.

A 9 by 7 matrix has roughly twice as many dots to be stored per character as does a 7 by 5. Increasing the size even further would increase the cost of the digital memory used to store the tables. It would be a costly brute-force solution to go to a larger matrix.

If cheracters are plotted in a 9 by 7 matrix, there are  $2^{63}$ , or approximately  $10^{19}$  different dot patterns which can be displayed. This is in striking contrast with the fact that there are at most  $10^3$  characters which can be recognized if displayed in that format. Make the rational assumption that there are less than  $10^5$  ways to display a given character on the matrix in readable form. It then follows that less than one dot pattern in  $10^{11}$  can actually be recognized as a character. 99.99999999 percent of all patterns which can appear in a 7 by 9 matrix are meaningless.

35

<sup>\*</sup>Throughout this thesis, the size of a vertical column (or position in a column) is noted first, followed by the size of a horizontal row (or position in a row). This convention is adopted to conform with matrix notation. Unfortunately, it does not conform to the usual notation of placing the smaller number first, followed by the larger number.

Fig. 3.1 Typical Dot-Matrix Characters

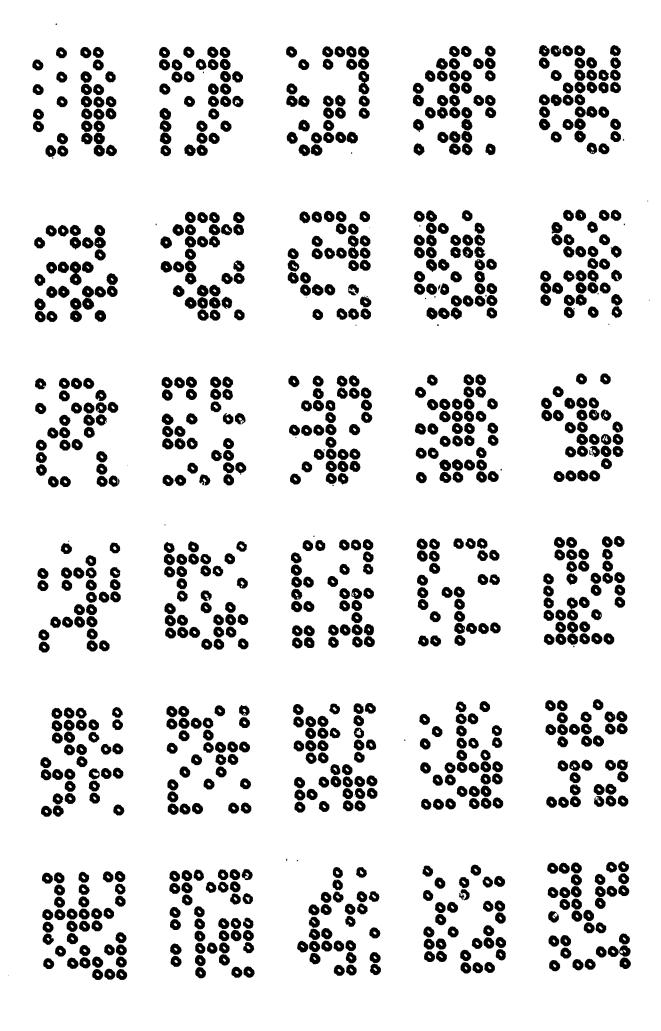

What characteristic separates the 10<sup>8</sup> meaningful patterns from the 10<sup>19</sup> meaningless ones? Consider how characters are chosen: They have evolved over the ages under the necessity that they be readable. If the human eye is not constructed to easily recognize a character, that character is probably meaningless. The eye is probably good at recognizing lines and curves, but is poor at recognizing sets of dots randomly sprinkled into a matrix. A large fraction of the 10<sup>19</sup> meaningless patterns were found to resemble dots randomly scattered into a matrix. The rest of the matrices resemble backward characters, or conglomerations of character parts. Figure 3.2 shows some matrices which were generated by computer using a random number generator. They represent a random sampling of the 10<sup>19</sup> patterns which could be constructed. None of them even closely resemble any character.

If one could weed out all the random patterns, and never allow them to be stored in the memory, the memory could be made smaller. In particular, it might be possible to store the m-bit matrices for all readable characters in less than m bits of memory, say n bits. This means that most of the m bit matrices, cannot be stored in the memory. If the n bits are coded in a way not yet defined, most of the non-representable codes will be the random patterns. More importantly, there will be at least one n-bit code for each readable character.

All of the above is obviously possible. The ASCII code is one such 7-bit code which can specify one of 128 "m-bit" matrices. The problem is that there is no simple way to map a given ASCII character into the appropriate m-bit matrix. If the map plus the storage of the n-bit codes involves more logic than storing the m-bit matrix directly, clearly nothing is gained.

Fig. 3.2 Most Probable Patterns in a 9.X 7 Matrix

The task is to find some simple mapping which will save memory. Many schemes were investigated. Line and curve drawing techniques tend, in the final implementation, to require many bits to specify endpoint, slope and curvature information. In addition, they are not compatible with the Intrex fixed sinusoidal scan pattern.

If one looks at one column at a time of the display matrix, an interesting fact is evident: Certain combinations of bits just never occur. It might therefore be possible to code the ones which can occur in fewer bits, using a column by column application of the principle described above for matrices. The technique is promising for capital letters, but gets involved for lower case and Greek letters. No simple map could be found to reduce the number of permissible columns.

# 3.2 SMOOTHING ALGORITHM

One would surmise that smoothing should best be done on a "two-dimensional" basis, since the characters exist on flat surfaces. A simple two-dimensional algorithm becomes evident if one compares characters generated on different size matrices. (See Figure 3.1.) The advantage which one gains when a larger matrix is used seems to be that the corners of the characters are more rounded and oblique lines are less ragged. Being able to finely position the parts of a letter (e.g. the middle bar of an "E") does not seem to be very critical. The eye is accustomed to recognizing both handwriting, which has inherently variable dimensions, and printing, which is done in many different fonts. Little information is conveyed by the exact placement of a character's parts.

The above observation seemed to suggest a method to economize on the size of the character matrix table. Suppose only the basic shape of the

character is stored in a small skeletal matrix. This matrix, if displayed, would look roughly like the desired characters, but because the matrix is small, the character would have many jagged features. It is possible to add additional dots between the skeletal points to make the letter "well rounded". This smoothing occurs just before the matrix is displayed. Thus a much larger matrix can be displayed than is stored in the read-only memory. The memory reduction would be advantageous since Project Intrex is interested in a very large symbol set. The dot matrix for approximately 200 symbols, including upper and lower case Greek and English letters, along with many scientific symbols, will have to be stored in digital memory.

# 3.3 INTERPOLATION ALGORITHM

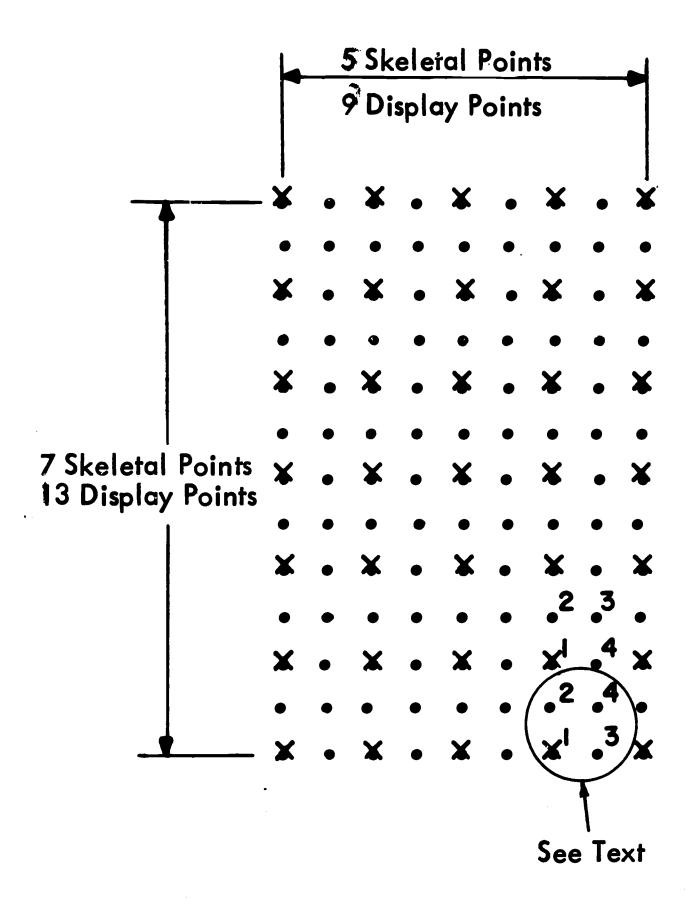

The simplest type of expansion from the skeletal matrix is to add a new row (column) between each of the specified rows (columns). Figure 3.3 shows the matrix with skeletal points marked with "x" and displayed points marked with ".". If the stored matrix is n by m, the displayed matrix will be (2n-1) by (2m-1). With large values of n and m, the displayed matrix has roughly four times as many dots as are in the skeletal matrix, leading to a 75% saving in memory.

It is now necessary to specify a smoothing algorithm which works well on characters and also has an economical realization. The following paragraphs attempt to derive the algorithm.

One recognizes a specific shape in a certain area of a character independently of the shape of the rest of the character. To detect the curved bottoms of the letters "O" and "U" for example, a person does not have to look at the top half of the characters. The smoothing algorithm should therefore be able to determine the smoothness of a particular feature of a letter using only the information in a small area of the skeletal matrix.

Fig. 3.3 Type of Display Points

Points Marked X are in the Skeletal Matrix Points Marked • are in the Display Matrix The smoothing algorithm will be given only those skeletal points which are within a certain distance of the point being computed. There is a window centered about each point which contains all the information necessary to specify the value of that point.

The curves and diagonals which need smoothing on a character can occur on any area of the character. Thus the type of smoothing is invariant to translation. The smoothing algorithm should use the same rules for smoothing no matter where in the image the window is placed.

It is possible to form a set of all the patterns which can appear in the window around a given point. A certain subset of this set will always cause the given point to be "on". Thus the smoothing consists merely of combinational logic driven by the values of the skeleton points inside the window.

A computer program was written for the PDP-1 computer to test various transformations of the type described. Using the light pen and oscilloscope of the computer, the operator is able to input a skeleton matrix and specify a set of rules for smoothing. The computer applies the smoothing to the skeleton matrix to form the display matrix.

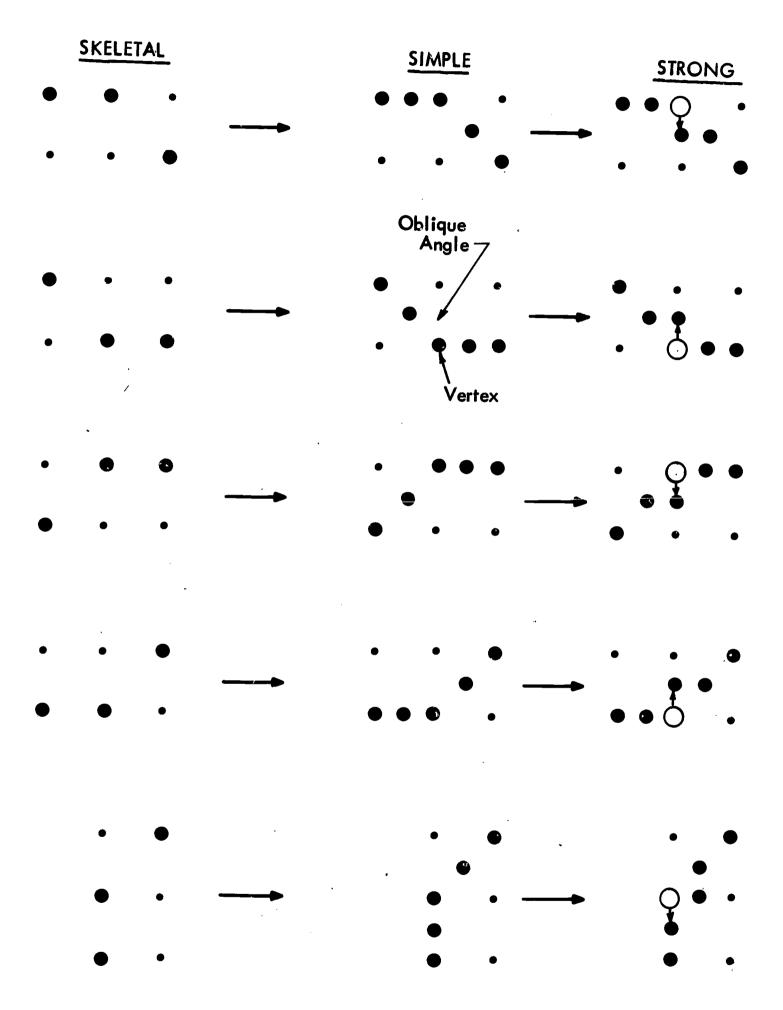

# 3.4 SIMPLE INTERPOLATION

Two interpolation algorithms were verified by simulation. The second is a refinement of the first. The problem of explaining the smoothing is complicated because there are four classes of display points which must be handled differently. They are:

- Type 1: Those which coincide with a skeletal point

- Type 2: Those which are one unit above a skeleton point

- Type 3: Those which are one unit right of a skeleton point

Type 4: Those which are one unit above and to the right of a skeleton point.

A different combinational logic net must be made for each of them. The more simple type of interpolation can now be described in tabular form. The first column of the table below tells the type of point being described by that line, and the second specifies the condition necessary for that point to be on.

### SIMPLE INTERPOLATION

# Type point Condition to be on

Rule 1. (on skeleton) -corresponding skeleton point is on.

Rule 2. (above skeleton) -both skeleton points above and below are on.

Rule 3. (right of skeleton) -both skeleton points to left and right are on.

Rule 4. (right and above) -two two closest skeletal points on one diagonal are on and the two closest skeleton points on the other diagonal are off.

Each of the four interpolation rules above is illustrated in the simple character in Figure 3.4a. The matrices shown in the left column are skeletal matrices. The matrix to the right of each skeletal matrix is the display matrix which was derived from it.

Interpolation rule number 4 (on points of type 4) is composed of two conditions which must both be met. If the second condition (Rule 4, above "...the two closest skeleton points on the other diagonal are off") is not enforced, the resultant interpolation yields characters like the one shown in Figure 3.4c. The problem is that the interpolator is trying to connect points 1 and 2 (see diagram) along the diagonal, and simultaneously along the square-cornered route from points 1 to 3 to 2. It is the job of the second condition in rule 4 to inhibit diagonal interpolation if there is a "square

(a) Simple Interpolation

(b) Filtered Letter

(c) See Text

Fig. 3.4 Simple Interpolation

ERIC

interpolation" possible. Thus the square corners of characters are not rounded.

### 3.5 STRONG INTERPOLATION

A second set of interpolation rules is illustrated in the simple patterns of Figure 3.5. This set of rules contains all the rules previously stated plus one more rule:

### STRONG INTERPOLATION

Rule 1 through Rule 4 plus:

Rule 5:

If a skeletal point is part of both a diagonal pattern and a vertical (or horizontal) pattern, then that skeletal point is moved to an adjacent display point as shown in Figure 3.5.

The skeletal point mentioned in rule 5 is the point which is at the vertex of the obtuse angle formed by the diagonal pattern and the vertical (or horizontal) pattern. To a certain extent, this point sticks out. The intention of rule 5 is to soften that point's effect by moving it inwards.

Rule 5 helps in many cases, but it also produces the undesirable patterns of lone dots in a row, and square shaped patterns in curved areas. These are evidenced in the characters of Figure 3.6.

The hardware implementation for the two smoothing algorithms described above is indicated in the following chapter, while Chapter 5 discusses their success in forming smooth characters.

Fig. 3.5 Moving Vertex of Oblique Angle

Fig. 3.6 Examples of Interpolation

### CHAPTER IV

### HARDWARE IMPLEMENTATION

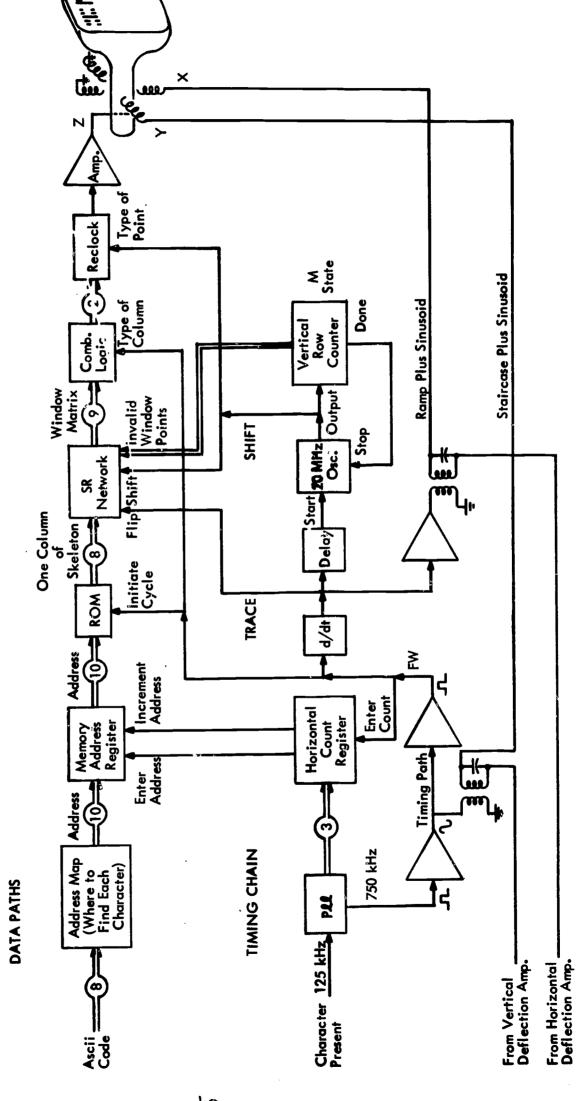

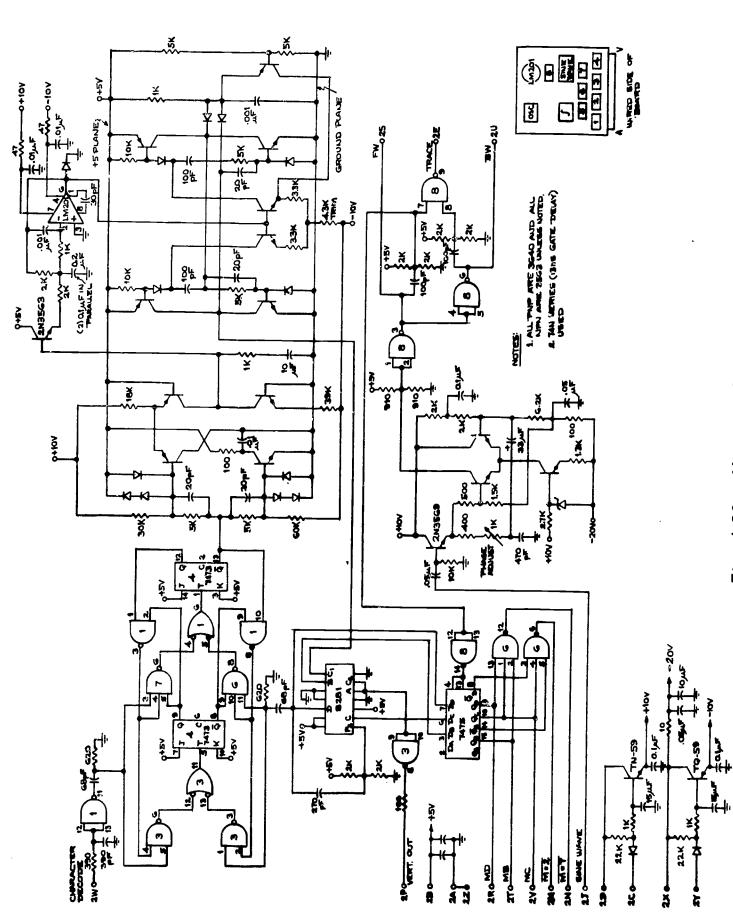

Like many other digital systems, the character generator is composed of a section which processes the matrix data, and a control network which directs the data processing. Figure 4.1 shows a block diagram of the whole system. The top half of the diagram is the data section.

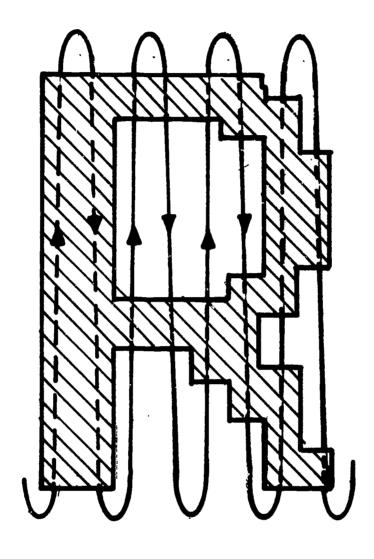

The third box in the top row is a commercially available "wire-rope" read-only memory. It stores the skeletal matrix for each of the 192 characters in the character set. Upon receipt of an ASCII code from the console, the read-only memory looks up the 7 by 5 skeletal matrix which corresponds to the code received. Details of the lookup process are discussed in Section 4.3. It sends that matrix to the interpolator, which is represented by the fourth through the sixth box in the top row of Figure 4.1. interpolator expands the 7 by 5 matrix to a 13 by 9 matrix, using the interpolation algorithm of Chapter 3. While the matrix is being expanded, it is put in the proper format to be displayed using the sinusoidal scan pattern. Since the interpolator is the heart of the thesis, it will be discussed first.

# 4.1 DATA SECTION

The intensity pattern in the display matrix must be presented to the CRT sequentially in order to be displayed using the sinusoidal scan. This serial nature of the output of the interpolator can be exploited to improve design. To better understand this relation, a series of examples which lead up to the complete data section of the interpolator will be discussed.

# 4.1.1 SIMPLE "FORMATTOR"

consider the simple problem of displaying an existing m by n ma

Fig. 4.1 Dot-Matrix Generator Block Diagram

without interpolation. Suppose the matrix is divided up into n m-bit words which are presented to the formattor one word at a time. To simplify matters, assume for the moment that only every other display region is being used to display dots. In this case all scans used for displaying are in the same direction. For purposes of discussion this direction will be considered down the columns of the matrix.

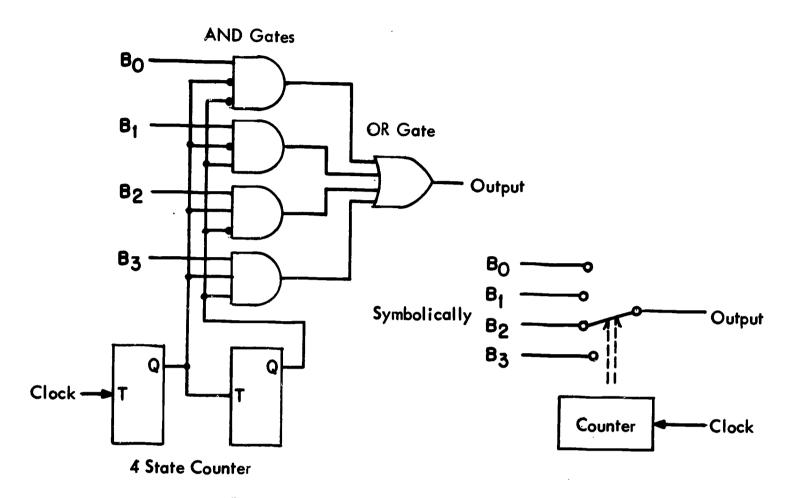

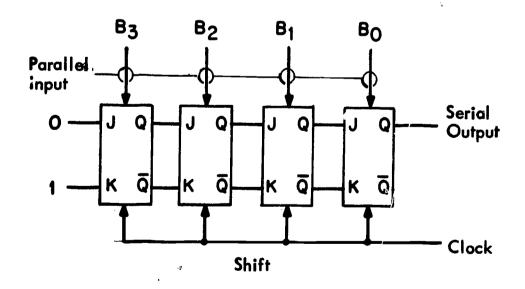

The formattor described here is nothing more than a parallel to serial converter. The converter accepts one m-bit word of the matrix at a time. It converts that word to a serial string before accepting the next word. Two possible implementations exist. The first is an m-position digitally controlled switch. (Figure 4.2 shows a 4-position switch.) When the control bits form a binary k, the k'th input is presented at the output. The control bits are generated by a counter, sequenced from 0 to m-1 by a clock which occurs whenever another bit of the serial output is desired. The second conversion method uses a parallel-in, serial-out shift-register. (Figure 4.3 shows a four-bit shift-register converter.) First, the information is transferred in parallel into the m bits of the register. Then the m bits are serially shifted out of the register by the output clock. The "switching" method is less complex, but the shift-register method has the advantage that it can be used as a memory unit also. Both methods will be used in the final interpolator.

## 4.1.2 COLUMN INTERPOLATION

Consider augmenting the formattor to do a simple type of interpolation described in interpolation rules no. 1 and no. 2 of Chapter 3. A new dot will be added by the interpolator directly after each dot of the row being formatted. Two values are generated on one output line for each

Fig. 4.2 Digitally Controlled Switch

Fig. 4.3 Shift-Register Converter

bit  $B_k$ . They are presented one after another, one at time k and the other at time  $k + \frac{1}{2}$ . A mathematical description of the output follows:

Output (k) =

$$B_k$$

Output (k +  $\frac{1}{2}$ ) =  $B_{k+1} \wedge B_k$

These rules cause "display points" to be added if they are between two "skeletal points". Figure 4.4 shows a matrix under this interpolation.

Although this interpolator could be implemented using two digitally controlled switches, it is much simpler to design it using a shift-register converter as shown in Figure 4.5. The converter presents the last bit of the shift-register when the signal PRIMARY DOT is true, and it presents the logical AND of the last bit and the next to the last bit when the signal SECONDARY DOT is true. The shift register is shifted on the trailing edge of SECONDARY DOT.

# 4.1.3 SIMPLE INTERPOLATION

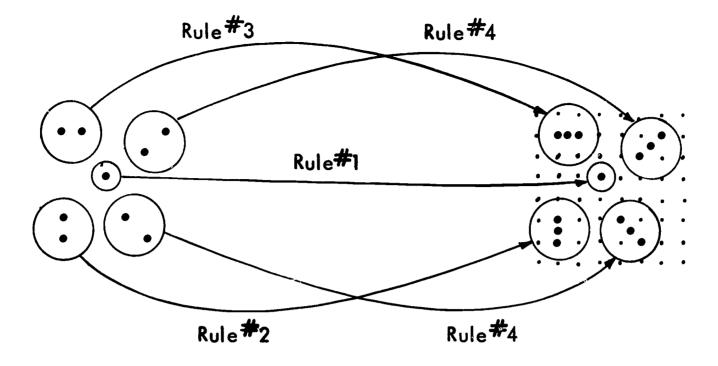

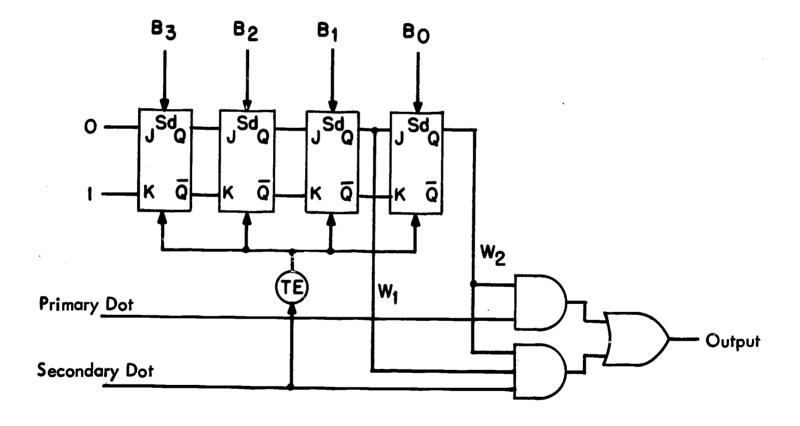

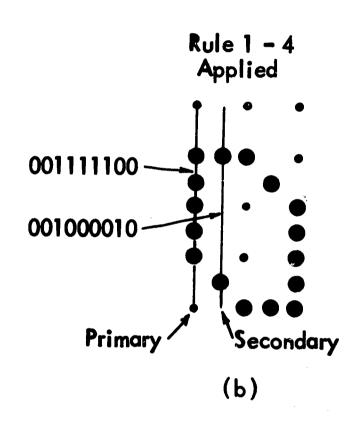

Interpolation rules no. 1 and no. 2 have been effectively implemented. Additional problems are encountered in adding rules no. 3 and no. 4, which allow for adding dots in horizontal or diagonal rows. The extra dots generated by these rules all fall into an extra column which must be added between the columns of the skeletal matrix. The interpolator must generate this "secondary row" after it generates each "primary row" described by the first type of interpolator. Another problem is that these rules involve the comparison of points in two adjacent rows. Both rows must be present in the interpolator at the same time.

One way to have both rows present is to add another m-bit shift register as shown in Figure 4.6. This register is used to hold the row previously processed. When the interpolator is generating a primary row, the input B<sub>k</sub>'s are converted to signals on the lines W<sub>11</sub> and W<sub>21</sub>. They

Fig. 4.4 Effect of Rule#1 and#2

Fig. 4.5 Interpolator for Rule#1 and #2

Fig. 4.6 Interpolator for Rules #1 Through #4

are used as before to perform type no. 1 and no. 2 interpolation. While this interpolation is being performed, shift register 2 is being loaded with the serial output of shift register 1.

When the interpolator is generating a secondary column, a new word of  $B_k$ 's are converted to signals on lines  $W_{11}$  and  $W_{21}$ . In addition,  $W_{12}$  and  $W_{22}$  scan the values of the previous column in the same manner that  $W_{11}$  and  $W_{12}$  do for the new columns.

The outputs W<sub>11</sub>, W<sub>12</sub>, W<sub>21</sub>, W<sub>22</sub> are named with subscripts because they can be thought of as a matrix. This matrix is actually the window matrix centered about the dot being generated. The shift register structure described in Figure 4.6 causes the window to slide down the rows of the matrix covering two columns at a time. At any instant, the window contains all the information necessary to do the desired interpolation. The values in the window, along with the type of row (primary or secondary) and type of point (primary or secondary) are fed to a combinational logic net to determine whether that point is on.

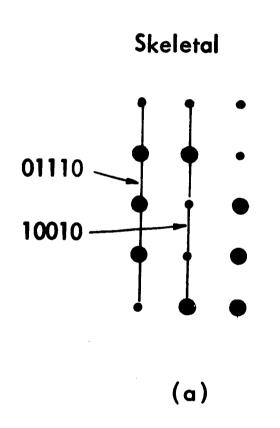

An example may be helpful at this time. Figure 4.7a shows a skeletal matrix, and Figure 4.7b shows the corresponding interpolated matrix. Figure 4.7c shows the contents of the two shift registers as the first two columns of the interpolated matrix in Figure 4.7b are being generated.

The first entry in Figure 4.7c labeled "example", shows the two shift registers containing the arbitrary literals A,B,...J. The last two outputs of SR1, (D and E) and SR2 (I and J) are used to form the window matrix. In the columns labeled "Primary" and "Secondary", the literals, A,B,...J have been replaced by specific values 0, 1, or  $\phi$ . The symbol " $\phi$ " represents the don't care condition: the interpolation is independent of its value. The purpose of the literals is to show the relation between the bits of the

Fig. 4.7 Effect of Rule#1 - Rule#4

| Type column | Contents<br>of SR1 | Contents<br>of SR2 | Window<br>matrix | Output<br>time | Output<br>value | Rule<br>used       |

|-------------|--------------------|--------------------|------------------|----------------|-----------------|--------------------|

| example:    | ABCDE              | FGHIJ              | JE<br>ID         |                |                 |                    |

|             | load word          |                    |                  |                |                 |                    |

| Primary:    | 01110              | ффффф              | Ø0<br>Ø1         | 1.0<br>1.5     | 0               | -                  |

|             | Ø0111              | oøøøø              | ø1<br>ø1         | 2.0<br>2.5     | 1               | #1<br>#2           |

|             | <b>øø</b> 011      | 10 <b>øø</b> ø     | ø1<br>ø1         | 3.0<br>3.5     | 1               | #2<br>#12          |

|             | <b>øøø</b> 01      | 110 <b>ø</b> ø     | Ø1<br>Ø0         | 4.0<br>4.5     | 1 0             | #1<br>=            |

|             | øøøøo              | 1110Ø              | Ø0<br>0Ø         | 5.0            | 0 .             | •                  |

|             | øøøøø              | 01110              |                  |                |                 |                    |

|             | load new word      |                    |                  |                |                 |                    |

| Secondary:  | 10010              | 01110              | 00<br>11         | 6.0<br>6.5     | 0               | -                  |

|             | <b>ø</b> 1001      | 00111              | 11<br>10         | 7.0<br>7.5     | 1<br>0          | #3<br>-            |

|             | <b>¢\$</b> 100     | 10011              | 10<br>10         | 8.0<br>8.5     | 0               | -                  |

|             | <b>øøø</b> 10      | 01001              | 10<br>01         | 9.0<br>9.5     | 0               | <del>-</del><br>#4 |

|             | øøøøl              | 00100              |                  | 10.0           | 0               | <del>#**</del>     |

|             | <i></i>            | 01001              |                  |                |                 |                    |

Fig. 4.7c Contents of Shift Registers

# W11 • W12 Rule#1 W21 • W22 Primary Column, Secondary Dot Rule#2 Secondary Column, Primary Dot Rule#3 Secondary Column, Secondary Dot Rule#4

Fig. 4.7d Patterns in the Window Matrix for Simple Interpolator

shift registers and the bits of the window matrix.

Before output time 1.0, the binary word 01110 (the first column of Figure 4.7a) is entered into SR1. As the primary scan progresses, this word is shifted into SR2. In the process, consecutive pairs of bits in the word are present in the window matrix.

Figure 4.7d shows the patterns which must be present in the window matrix if the output value is to be a 1. A heavy dot indicates that the bit must be a 1, a circle indicates that the bit must be a 0, and a light dot indicates that the value of that bit has no effect on the decision. Given that a certain type of dot (primary or secondary) is to be generated in a certain type of column (primary or secondary), one can look in the appropriate portion of Figure 4.7d. If there is a pattern in that portion which matches the pattern in the window matrix, then the output of the interpolator is a 1. In this manner the binary string 001111100 is produced by the primary scan. This is the first column in Figure 4.7b. The last column in Figure 4.7c shows which rules were used to generate each 1 in the string.

After the primary scan, a new word (binary 10010) is loaded into SR1. This is the second column of Figure 4.7a. Another scan is performed except this time the rules for interpolation are for a secondary row. The string produced, 001000010, is the second column of Figure 4.7b.

4.1.4 ORDER REVERSING

It is possible to remove the restriction that only scans down a column are used for displaying dots. Dots can be displayed in every display region, whether the beam is scanning upward or downward. The problem encountered is that the display matrix points must be generated in reverse order when the beam is scanning upward. Since the interpolation rules operate equally well on matrices whose columns are upside down, the column can be generated in

reverse order, by sliding down a skeletal matrix whose columns have been turned upside down. Thus all one needs to do is to insure that the matrix is upside down when generating an upward column. The interpolation can then be carried out in the same manner as a downward column.

It is necessary to have the matrix in its upside down form every odd scan, and in its right side up form every even scan. The contents of the shift registers must therefore have their order reversed between each scan. Bit 1 is swapped with Bit n, Bit 2 with Bit n-1,etc. This feat can be accomplished in one parallel operation as shown in Figure 4.8. When shifting, information is entered into each cell through its input A. When flipping, information is entered through its input B. (An additional parallel entry path for the B<sub>k</sub>'s has not been shown because it is not needed in the next section.)

An alternative approach to the problem is to have bi-directional shift registers. The registers would shift forward during one scan, and backward during the next scan. Bi-directional shift registers and order flipping shift registers in themselves require the same logic to implement. Formation of the window matrix using bi-directional shift registers is more complicated because different bits of the shift register must be used when shifting in different directions. They were not employed for that reason.

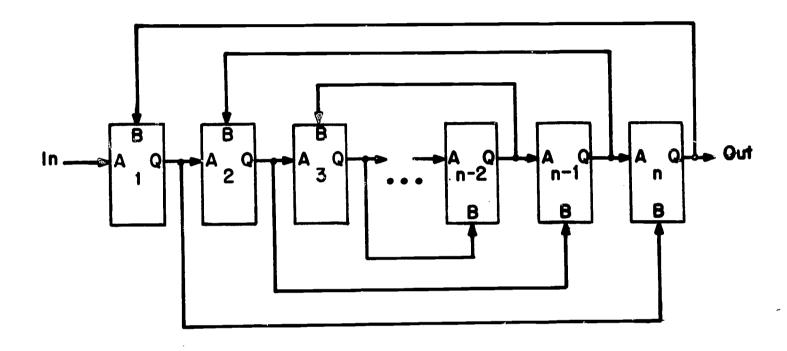

4.1.5 STRONG INTERPOLATION

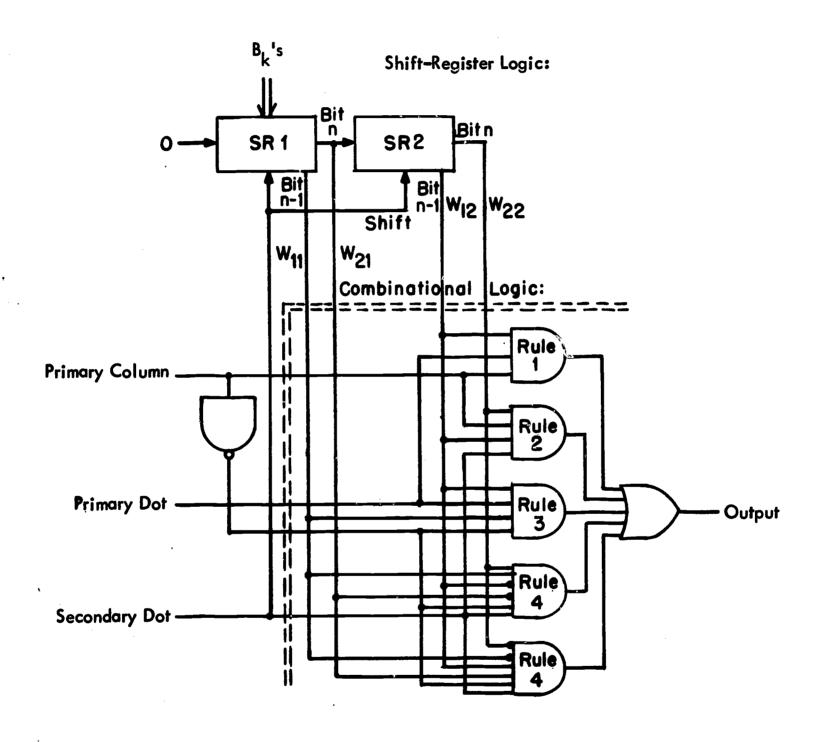

This is the final example in the series of machines: this is the description of the machine which was built for the Intrex console. Interpolation rules no. 1 through no. 5, which do all the previous filtering and, in addition, move the vertex of an obtuse angle inwards, can now be implemented. These rules require a 3 by 3 window matrix for generation of the primary columns, and a 3 by 2 matrix for the generation of secondary columns.

Fig. 4.8 Bit-Reversing Shift Register

This requirement will be substantiated in a few pages.

It is necessary to form a configuration of shift registers which will produce the larger window matrix. The goal is basically an extension of the 2 by 2 configuration. To obtain an extra column in the window matrix, another shift register is added. To obtain an extra row, one clocked delay is added and one more output is taken from each shift register. In addition, part of SRI has been replaced by a digitally controlled switch to reduce logic. The data structure, shown in Figure 4.9, is a little more complicated, and is described in the following paragraphs.

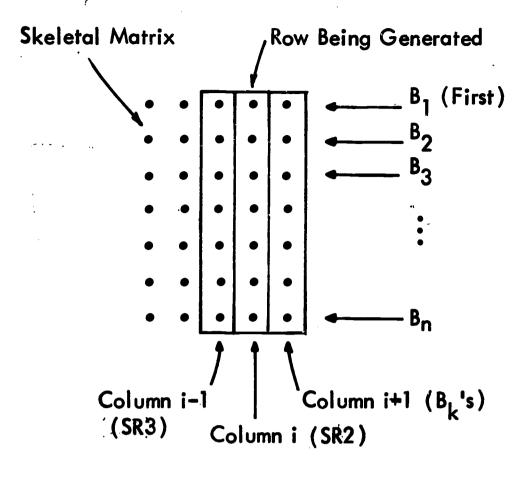

During the primary scan, one m-bit word is presented in parallel on lines  $B_k$ . Figure 4.10 defines the process explicitly. If the column of the display matrix corresponding to column i in the skeletal matrix is about to be generated, then column i+1 is present on the  $B_k$ 's at this time. This advance allows the interpolator to look one column ahead of the column it is generating. SR2 is assumed to contain column i, and SR3 is assumed to contain column i-1. These assumptions will be justified shortly.

Before the scan is started, B<sub>1</sub> is loaded into one of the one bit delays shown in Figure 4.9. Before shifting is started, W<sub>21</sub>, W<sub>22</sub>, and W<sub>23</sub> are the first bits in column i+1, i, and i-1 respectively of the skeletal matrix. W<sub>31</sub>, W<sub>32</sub> and W<sub>33</sub> contain the second bit of their respective columns. W<sub>11</sub>, W<sub>12</sub>, and W<sub>13</sub> contain incorrect values. This error corresponds to the situation depicted in Figure 4.11. Part of the large window matrix falls outside the skeletal matrix into an undefined area. To prevent any points from being incorrectly added to the interpolator's output, these values are defined to be zero during the first shift state. The AND gates in Figure 4.9 perform this function.

During the primary scan, the data switches are set so that SR2 is

Fig. 4.9 Shift-Register Network for Rules #1 Through #5

Fig. 4.10 Data Present in Interpolator

Fig. 4.11 Undefined Values in Window Matrix

shifted into SR3 and the  $B_k$ 's are converted to a serial string and shifted into SR2. The clocked delay is always driven by the output of SR3. It is used to generate  $W_{33}$ . Once the registers have been shifted once, all the windows contain correct values. For example,  $W_{31}$  contains bit 1 of column i+1,  $W_{21}$  contains bit 2 of that column, and  $W_{11}$  contains bit 3. After each shift-pulse, the bits advance in the shift registers, and the window appears to slide down the columns of the skeleton matrix. Until the last shift pulse, all the values of the window matrix are valid. Then part of the window matrix extends below the skeletal matrix. The remedy is again to AND out the invalid levels during the last shift time.

After the primary scan is completed, SR2 contains column i+1, and SR3 contains word i. Now the interpolator is ready to generate a secondary column between column i and column i+1. Since this column is displayed on the upswing of the scan, it must be generated in the opposite direction. The shift registers must have their order reversed at this time.

During the secondary scan, the data flow switches cause the shiftregisters to recirculate upon themselves. The undefined conditions caused

by the window matrix extending outside the skeletal matrix exist in this

scan as before and are treated using the same logic.

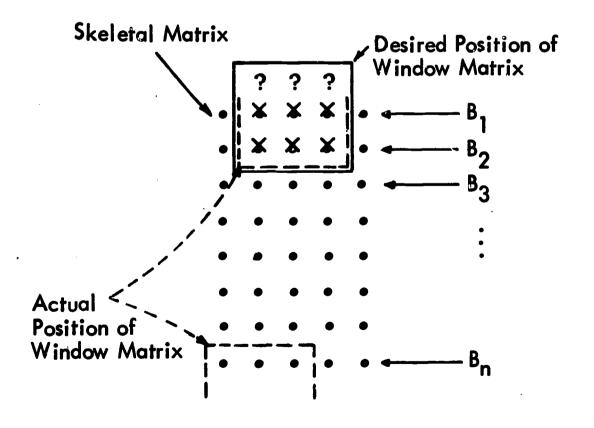

Because only a 3 by 2 window matrix is needed to do this secondary interpolation, only two shift-registers, SR2 and SR3, take an active part in producing the window matrix at this time. The digitally controlled switch is not used during this scan. The 3 by 2 window matrix is shown in Figure 4.12. Unfortunately, the indices of the W's do not coincide with their position in the window matrix. This is only a conceptual problem - the combinational logic can be wired around it.

Secondary Scan

Primary Scan

Fig. 4.12 Window Matrices Definition

After the secondary scan is completed, SR2 contains word i+1, and SR3 contains word i. It is now necessary to re-flip the bits of the shift-registers back to their forward order, since the next scan is in the forward direction. The net effect of advancing and flipping the columns during the primary scan, and recirculating and flipping them during the secondary scan is to put SR2 into SR3 and to put the B<sub>k</sub>'s into SR2, both in unreversed form. It is easy to see that after a few cycles SR2 will always contain the previous column processed, and SR3 will contain the column processed before that. Thus our original assumption to that effect was justified.

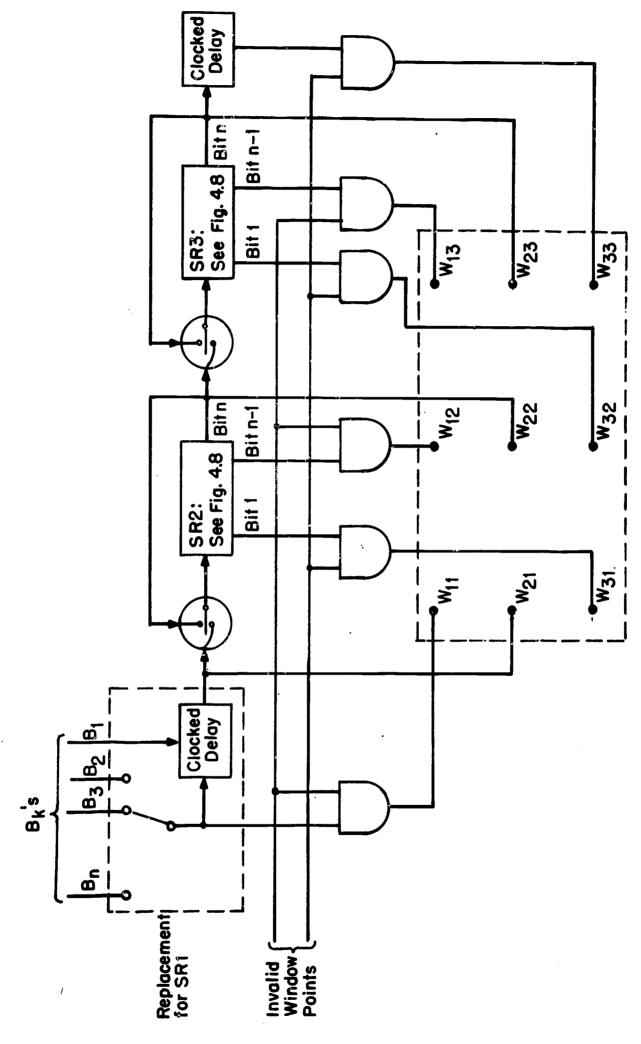

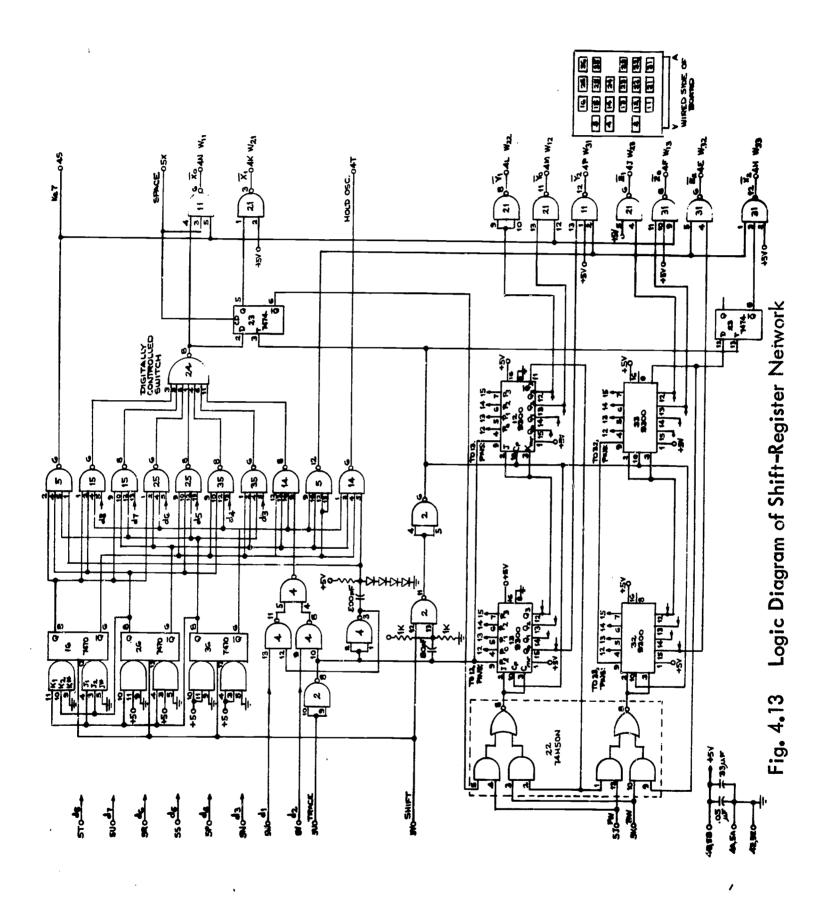

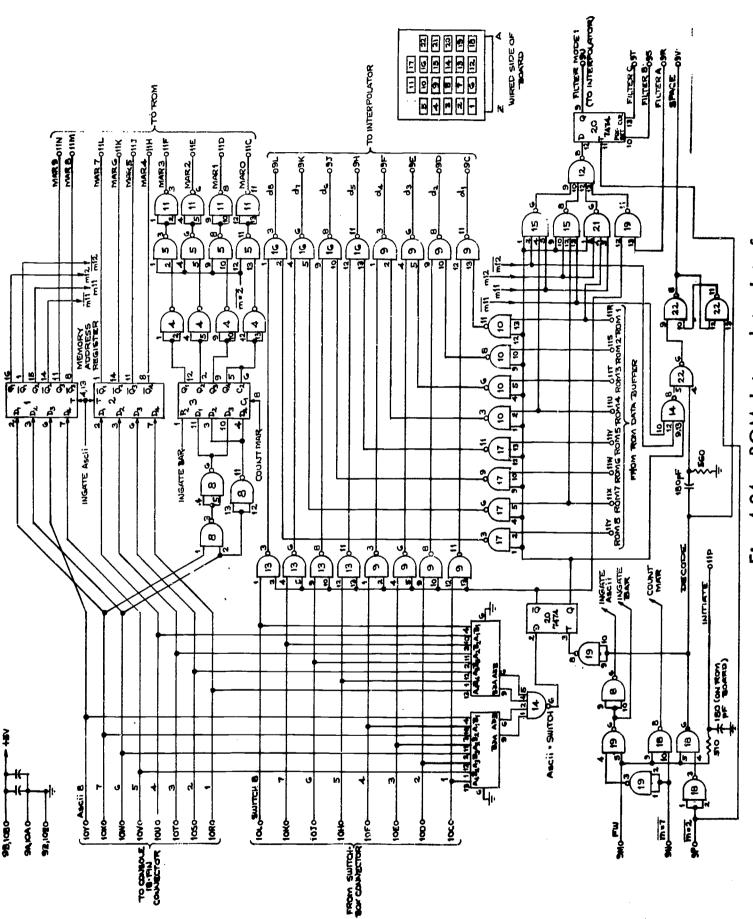

Figure 4.13 shows the hardware logic diagram which performs all the shifting and flipping operations necessary to generate the window matrix.

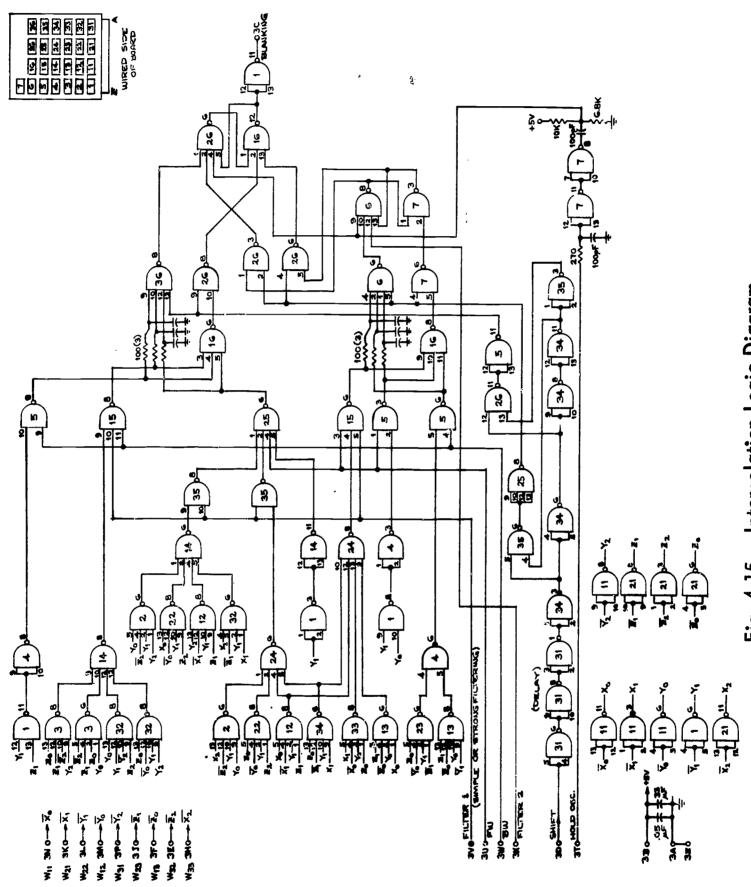

Figure 4.14 shows the patterns which must appear in the window to generate the four types of points in the display matrix. The combinational logic in Figure 4.15 implements these rules.

Two additional features are shown in that figure. It is possible to either apply rule no. 5 or not. If the level labeled FILTER MODE 1 is TRUE, rules no. 1 through no. 5 are used to generate the display matrix. (Strong interpolation is performed.) If FILTER MODE 1 is FAISE, only rules no. 1 through no. 4 are used. (Simple interpolation is performed.) This provision was added because best results are obtained by interpolating some characters using simple interpolation, and others using strong interpolation. An extra bit is stored in the read-only memory for each character, to tell which type of interpolation is to be applied.

The second addition was required because of the high operating frequency of the interpolator. Since a dot is generated every 25 nanoseconds, races in the combinational logic become critical. Note that strings of func-

# Primary Column, Primary Dot is on only if the Pattern is Present in the Three by Three, and None of the Following Patterns are Present Primary Column, Secondary Dot Secondary Column, Primary Dot Secondary Column, Secondary Dot

Fig. 4.14 Patterns in the Window Matrix for Strong Interpolation

Fig. 4.15 Interpolation Logic Diagram

tionally useless inverters or R-C delays have been added to several paths. This forces all paths to be within about one gate delay of each other. To prevent any remaining races from reaching the CRT, the two outputs for each shift-pulse are stored in two buffer flip-flops before they are multiplexed onto one output line.

The blanking amplifier, shown in Figure 4.16, was designed by Professor J. K. Roberge. It is capable of driving a 30 volt waveform into a 20pF load with a rise time of 6ns. The output stage is a complementary common emitter amplifier.

#### 4.2 TIMING CHAIN

The timing chain directs the operation of the data section of the interpolator just described. Supplied with only a single pulse every character, the timing chain forms some 200-odd time periods which are necessary to display that character. Design was complicated by the following facts:

- 1) The timing of the unit must follow the timing of the drum.

The unit cannot operate asynchronously.

- 2) A periodic signal must be used to produce the sinusoidal scan, and the appropriate frequency is not recorded on the drum.

- 3) Delays in the deflection circuits must be compensated for by the timing circuitry.

It proved impossible to synchronize all timing signals with one high speed clock. Pulses are consequently formed by subdividing the pulses from the drum into many shorter ones. The horizontal generator (Section 4.2.1) produces a fixed number of periodic column scans for each character pulse from the drum. One character-time interval is thus divided into the correct

Fig. 4.16 Blanking A. plifier

number of column intervals. Each of these display regions is then segmented by the "vertical generator" (Section 4.2.4) into dot-time intervals.

4.2.1 HORIZONTAL TIMING

It is now necessary to fix the number of columns generated per complete character. When displaying a full screen of characters, it is necessary to leave some space between characters to prevent them from running together. One solution is to add a staircase signal to the ramp before it goes into the horizontal deflection amplifier. The staircase would advance to a new step after each character and move the scan pattern right for the next character. Unfortunately, this scheme requires a settling time of approximately one half of the sine wave period and is therefore impossible with a 10µs deflection system.

Another more tractable method of spacing is to keep the constant sinusoidal scan across the line and leave blank scans between characters. It is desirable to use an even number of scans to plot a character and its space, since then an integral number of sine wave periods would be used, and all characters would begin on the same phase of the sine wave. Because there are an odd number of scans (9) consumed in plotting the 13 by 9 matrix, there must also be an odd number of blank scans. One scan gives insufficient space, but three blank scans yield the proper spacing. It is undesirable to go to five or more blank scans, because the percent of time used for plotting is decreased, and hence frequencies in the interpolator must go up. With three blank scans, a total of 12 scans, or six sine wave periods, are necessary per character.

It is therefore necessary to generate six cycles of a sine wave per character. Unfortunately, this frequency is not present in the internal

timing of the console. There are periodic pulses available at  $10 \cdot f_0$ , which are used to shift ten bit ASCII codes from the drum to the console. ( $f_0$  is the frequency of plotting characters;  $f_0 = 0.118 \text{MHz}$ .) These pulses are of no help, since 6 does not divide ten evenly. The only solution is to synthesize a 6· $f_0$  square wave from the  $f_0$  pulses present in the console.

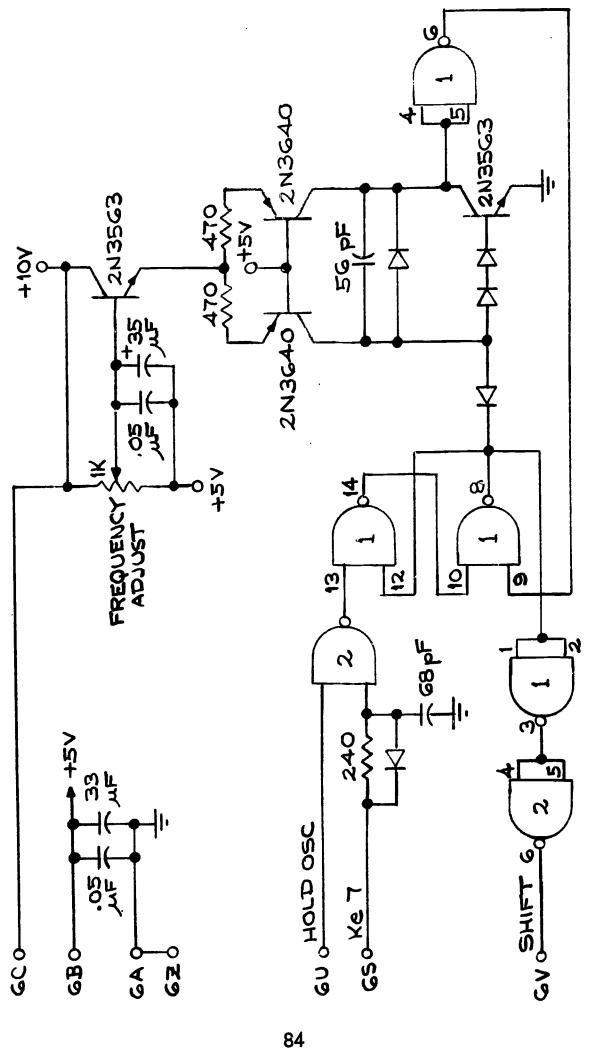

#### 4.2.2 PHASE-LOCKED LOOP

Figure 4.17 shows the details of the phase-locked loop shown in the lower left hand corner of Figure 4.1. It generates a frequency 6 times  $f_0$  from a reference signal at point A of  $f_0$ . (See Figure 4.17.) A voltage-controlled oscillator runs at about 6. $f_0$ . The output is divided by 6 to produce a signal at point B of about  $f_0$ . This signal is compared to the reference frequency at point A and if it is not the same, an error signal is sent to the integrator and the frequency of the voltage-controlled oscillator is changed appropriately.

It is the phase of the reference signal at A that is compared with the phase of the generated signal at point B. The comparison is done by a 4-state up-down counter which is incremented at every pulse from A, and decremented by every pulse from B. The counter stays in its highest state, called state 3, if it is incremented while in that state—it does not go to its lowest state as a modulo 4 counter would do. It also stays in the lowest state, called state 0, if decremented in state 0. If the counter were started in state 1, the number in the counter at any subsequent time would measure the difference in the number of pulses at point A from the number at point B, provided this difference never exceeds -1 or +2.

The output of the counter is an analog -1 unit if the counter is in state 0 or 1, and is an analog +1 unit if the counter is in state 2 or 3.

Fig. 4.17 Phase-Locked Loop

ERIC Arull Raxt Provided by ERIC Therefore the integrator's output has a negative slope if the counter contains a 0 or 1 and has a positive slope if the counter contains a 2 or 3. The output of the integrator is fed to a low pass filter, which rolls off with two poles (Q = 5) at about  $f_0/10$ . The filter reduces the pulse to pulse frequency modulation of the oscillator.

There are two distinct modes of operation of the loop, each characterized by the counter being in a different set of states. First is the capturing mode. If the synthesized frequency at point B is much larger (smaller) than the reference frequency for at A, then the counter will spend all of its time in states 0 and 1 (states 2 and 3). The integrator would therefore decrease (increase) its value, and the oscillator will also decrease (increase) its frequency. Finally, the frequency at B will actually be littler smaller (larger) than that of A. Two pulses at A (B) will occur between pulses at B (A), and the loop enters state 2 (state 1) from state 1 (state 2).

The second mode is called the locked mode, and is characterized by the counter being in state 1 or 2. To show that the loop does indeed lock when in states 1 or 2, it is necessary to get the open loop frequency response of the system. Figure 4.18 shows the frequency response of the various parts of the system. Two of the boxes require some special explanation. The first is the comparator. When operating exclusively in states 1 and 2, pulses come to the comparator alternately from points A and then from B. One pulse from A takes the comparator from state 1 to state 2, and then a pulse from B takes it from state 2 to state 1. The time average of the output of the counter, taken over one of these cycles, is zero if the two signals are exactly 180 degrees out of phase. The time average, taken in

Fig. 4.18 Frequency Diagram of Phase-Locked Loop

the same way, is proportional to the difference of the relative phases from 180 degrees. In terms of frequency of the square wave input, the output is proportional to the integral of the difference of frequencies. Therefore the comparator integrates its input frequency to obtain its output, and is denoted as an integrator.